晶体最全介绍

晶体最全面的介绍

晶体

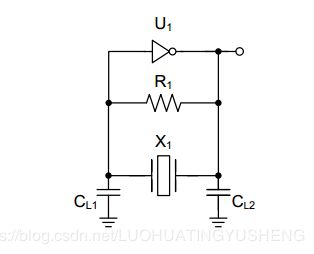

振荡器电路由反相放大器(显示为反相器),反馈电阻,两个电容和晶体组成。工作时,晶体和电容形成一个pi滤波器为内部放大器提供180度相移,保持振荡器锁定在指定频率。

振荡的产生

通过注入由噪声和/或瞬态电源响应组成的能量来实现振荡器启动。晶体振荡器由反馈网络和放大器或增益元件组成。

巴克豪森稳定性准则

振荡器背后的原理是满足巴克豪森条件的正反馈回路:如果闭环增益大于1且总相位滞后为360°,由此产生的闭环系统是不稳定的并且会自我强化。

这是振荡存在的必要但不充分的条件。当满足必要条件时,振荡器中的任何干扰(噪声)都将导致振荡开始。

满足巴克豪森条件的频率被放大最多,因为它与原始信号同相。初始振荡非常弱,并且需要花费时间将信号放大到所需的幅度。当建立振荡时,仅需要少量能量来补偿电路中的损耗。

在数学上,需要一个闭环增益来维持稳态振荡。MCU依靠内部稳压器在时钟信号达到所需幅度时将闭环增益调整为1。放大级和滤波器,决定哪个频率经历360度相位滞后。在晶体振荡器的情况下,滤波器由晶体和外部负载电容器组成。

石英晶体的负载电容

请注意晶体的负载电容指的是从晶体的两个引脚看进去的所有电容之和,即就是外部引脚调整电容和内部的寄生电容。

晶体的实际模型

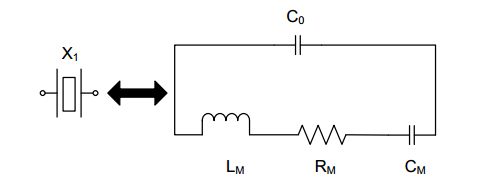

石英晶体是一种将电能转换为机械能的压电器件。该变换发生在共振频率。图中显示描述石英晶体的简化电气模型,其中Co是并联电容(是切割方式和封装导致的,基本上不会变化),LM是动态电感,CM是动态电容,RM是动态电阻。图中的模型是简化模型,仅包括基本振荡频率。事实上,晶体也可以在基频的奇次谐波处振荡。

晶体的频率

晶体具有两个谐振频率,其特征在于零相移。随着频率和电抗的增加,电感的存在变得更加明显。

串联谐振

忽略分流电容C0,串联谐振频率定义为电感和电容的电抗抵消。在此频率下,晶体仅出现电阻特性,且阻抗最小,而没有相位偏移,即就是串联谐振。

因此,串联谐振频率fS的值由LM和CM确定。串联谐振频率是自然谐振频率,其中机械能和电能之间的能量转换是最有效的。

反谐振频率

在较高频率下,等效电路将呈现电感性,这意味着更高的阻抗。当来自晶体的感抗抵消来自并联电容C0的容抗时,存在具有零相移的另一谐振频率。该频率称为反谐振频率fA。在此频率下,阻抗达到最大值。晶体中的电感和并联电容将相互馈电,并获得尽可能低的电流消耗。

fA与fS

fS和fA之间的频率范围称为并联谐振区域,是晶体正常振荡的区域。在谐振频率下,反馈环路中的相位滞后由具有180°相位滞后的放大器和具有180°相位滞后的两个电容器提供。在实际中,放大器提供略高于180°的相移,这意味着晶体必须具有轻微的电感性以满足巴克豪森标准。

如晶体数据表中所述,振荡频率在谐振频率之间。

等效串联电阻

等效串联电阻(ESR)是晶体在串联谐振频率下表现出的电阻。 下面给出了ESR计算公式。

由于C0通常约为1 pF且CL为5-9 pF,因此许多晶体的ESR约为RM,则ESR近似为动态电阻。

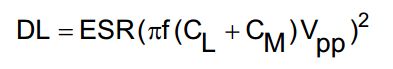

驱动电平

晶体的驱动电平指的是晶体中消耗的功率。晶体的最大驱动电平通常在晶体数据表中以μW表示。超过此值可能会损坏或缩短晶体的寿命,可能导致晶体振动发生异常。下面给出了W的驱动电平。

Vpp是晶体上的峰峰值电压;

用上式计算DL并将该值与晶体数据表中的最大指定DL进行比较可以揭示晶体在操作期间是否可能具有可靠性问题。

如何测量Vpp的值?(可以使用测量晶体电流,然后乘以电阻的方式来计算晶体的功率)。

一般的,为了防止CPU输出的驱动功率大于晶体的最大功率,我们会在晶体/CPU的Xout脚串联一颗电阻,防止CPU振坏晶体。

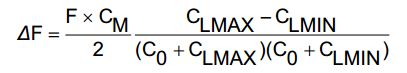

Crystal Pulling

通过改变负载电容可以改变晶体频率。参数ΔF是由于其负载电容的变化引起的晶体的谐振频率变化。通过下式给出晶体的指定(并联)谐振频率变化值。

CLMAX和CLMIN是可以提供给晶体的最大和最小负载电容。有时候,内部寄存器可以改变内部的可调电容,进而直接改变频率,可以省掉外面的电容。

负阻 negative Res

负阻最早见于隧道二极管中的描述。

术语负电阻历史上与诸如真空管或隧道二极管的有源器件相关联,其特性在其I-V曲线的2个特定区域中操作时改变。这些有源器件在I-V曲线中呈现下降,使得电压的增加导致电流减小。这种称为负电阻的行为在创建微波振荡器(在隧道二极管的情况下)中非常有用。

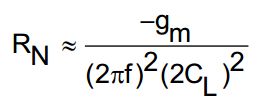

皮尔斯研究表明,所以提高增益和减小调整电容的容值可以提高负阻值。

为了确保晶体振荡器的稳健启动,在晶体初始启动期间,负电阻的值必须至少比ESR大5倍,但在启动后在稳态运行期间可能比ESR大2到3倍。

以下部分显示增加的负电阻幅度会减少振荡器的启动时间。

gm-是振荡器中有源元件的跨导

CL-是负载电容

您还可以通过引入与晶体串联的电阻来找到电路的负电阻。为避免寄生效应,建议使用0201电阻来完成此任务。额外的0201外部电阻和ESR或振荡器无法启动的晶体之和的阈值是与电路负电阻大致相同。

振荡器的时间常数

晶体振荡器的启动时间由导通时的瞬态条件,负电阻引起的小信号包络扩展和大信号幅度限制决定。包络扩展是总负阻和晶体的运动电感的函数。

包络扩展的时间常数与下式给出的振荡器的启动时间成比例。

具有低LM的晶体可以缩短启动时间高幅度RN(低CL)也是如此。

低运动电容(CM)引起的可牵引性与低运动电感引起的快速启动时间之间存在折衷(LM),因为晶体的频率取决于CM和LM。

较小封装尺寸的晶体具有较大的LM,并且比较大封装尺寸的晶体开始更慢。

降低CL也会降低驱动电平,从而允许振荡幅度增加。

晶振参数表

晶体Layout

1、为了最大限度地降低寄生天线和寄生耦合现象引起的噪声敏感度,晶振,电容(需要时)和MCU振荡器引脚之间的距离应尽可能短。

2、如果无法将外部振荡器元件靠近振荡器引脚,则在布线这些信号时应小心。

3、避免MCU下方的长迹线以及可能产生逻辑活动的伪耦合的其他电路。

4、还要避免将任何其他信号路由到晶体区域。

5、两个电容器的接地端(如果需要外部电容器)必须就近接地。这些连接应尽可能短,并且每个电容器的长度相等。

6、确保振荡器下方的接地平面完整。

7、不要在振荡器下面使用单独的接地层,与参考地的连接很窄,因为它可以充当天线。

8、为避免与周围信号走线耦合,最好在振荡器及其组件周围放置接地保护环。

端午节于深圳。