MIPI D-PHY 带宽矩阵用户指南

引言

随着视频信号从标清到高清和超高清的发展,原来所使用的视频信号并行传输接口,其难以扩展、接口引脚多以及高功耗等缺点已经变得尤为突出。新兴的基于数据包传输的串行接口,如MIPI CSI-2和DSI接口,可以解决并行接口的不足,同时也可以减小系统的复杂性。理解并行和串行接口带宽的计算方法,可以避免在选择正确的FPGA数据通道(Lane)数量和每个通道所需要的数据传输速率时遇到的问题。这篇文档详细地描述了图像传感器(image sensor)通过MIPI CSI-2或DSI接口的单个数据通道(single lane)或多个数据通道(multi-lane)在输出RGB,YUV或RAW数据时计算带宽和数据速率的方法。同样的计算方法可以被应用到其他的视频接口上,如FPD-Link,HiSPI和HDMI等。

图1表示一个CMOS Sensor桥设计的概念模型。在图的左边,一个CMOS Sensor通过1~4个串行数据通道(Lane)传输图像数据到FPGA;FPGA sensor桥将各个Lane中的数据组合起来,并转换这些数据为并行数据。在图的右边部分,图像数据以标准视频格式从并行总线输出。基于已知的输出视频格式信息,可以计算出所需要的带宽。因为FPGA不会缓存视频帧,CMOS传感器输入的视频信号峰值必须满足输出的带宽要求。根据这样的推定,可以估计最大数据速率和CMOS sensor接口的位(bit)时钟频率。

视频格式

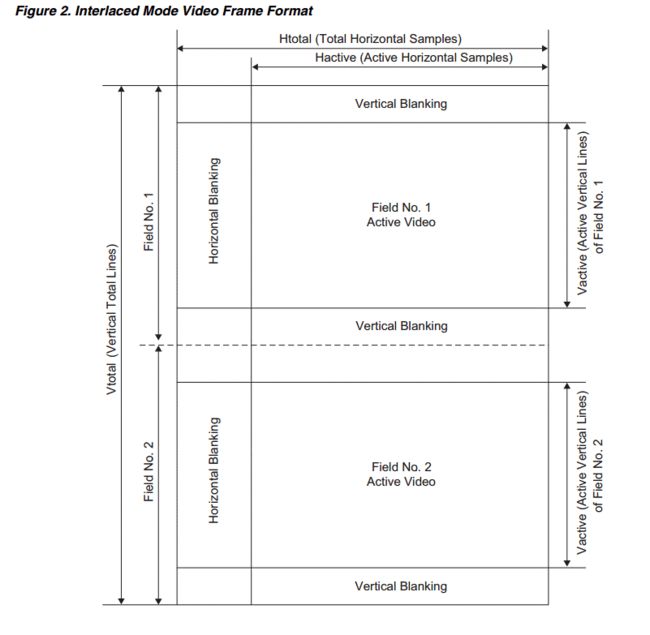

为了估算数据传输速率,需要理解经过sensor bridge传输的视频数据的格式。视频是由一系列的静止的图像组成的,每一幅静止的图像由很多个单独的像素行来组成的。图2表示一个图像隔行扫瞄视频帧的概念图。逐行扫描的视频帧与其非常相似,只是每帧只有一个Field.

对于数字视频,每一套单独的行同步(HorizontalSync HS),场同步(Vertical Sync VS)和数据有效(Data Enable DE)信号被用来同步视频数据传输;或一个嵌入到视频数据流的特殊的序列表示有效视频信号的开始(Start of Active Video SAV),有效视频的结束(End of ActiveVideo EAV)。对于MIPI CSI-2,在LLP层(Low Level Protocol)定义了两种包结构:长包携带有效的视频信号,短包里包含帧同步(例如帧起始和帧结束)和行同步(行开始和行结束)。

视频流有许多的特征,例如:帧速率,逐行扫描与隔行扫描,长宽比,立体,颜色空间和颜色深度等。在后续的讨论中,主要讨论的是用于计算数据传输速率的主要参数。

视频分辨率和像素时钟

视频分辨率定义为宽(width)×高(height),单位为像素。例如:1920×1080表示行有1920个像素,列有1080个像素。图3表示常见的分辨率。

有两种主要的视频格式标准:SMPTE/CEA为广播电视定义视频标准;VESA为计算机显示器定义视频标准。表1罗列了最常见的视频分辨率。在这些中间,我们选择HD(1280×720p) FHD(1920×1080p)和UHD(3840×2160p)为例在后续的章节中来计算带宽和数据传输速率。

有些图像传感器可以输出标准视频格式的图像,但同样也有一些输出为非标准的。无论哪种,最为重要的是要获取每一行总的采样数,总的行数,还有帧刷新速率。基于这些才能够讨论怎样计算带宽。

色彩深度

色彩深度,也称为位深,即表示单个像素中各个颜色分量的比特数。深颜色空间支持30/36/48bitRGB颜色深度。在本文档中,像素深度等于每一个像素中所有颜色的深度。例如:30bit深颜色RGB的像素尺寸定义每像素30 bit,或者每种颜色10bit.

MIPI CSI-2/DSI 接口

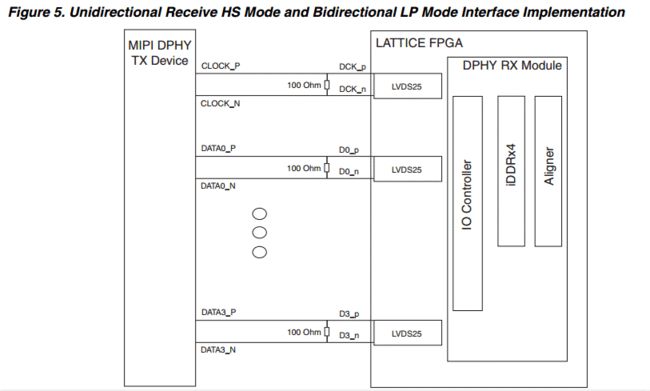

CSI-2和DSI是两种基于MIPI D-PHY物理接口的串行协议。MIPI D-PHY支持单向HS(High Speed)模式和双向LP(Low Power)模式。对于CMOS传感器桥的应用,只需要MIPI D-PHY接收器(RX)在FPGA的接收接口处,它允许连接桥接收HS数据,通过一个时钟Lane和多达4个的数据Lane.图4a显示了单向接收器HS模式的接口框图,图4b显示了单向接收器HS模式和双向LP模式的接口框图。

组包

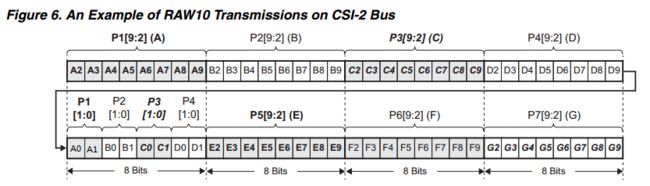

MIPI CSI-2支持YUV,RGB,或RAW数据,每个像素格式从6bit到24bit不等。在数据进入LLP(Low LevelProtocol)发送之前,发送器会将像素数据组包成字节(Pixel-to-byte Packing);在接收器端,从LLP层接收到的字节数据将会被解包到像素数据(Byte-to-PixelUnpacking).一个CSI-2的长包包括一整行图像数据。对于所有的数据类型,长包中的数据的总大小应该是8bit(Byte)的整数倍。图5是一个4个10bit(RAW10)像素数据组包成5个字节的例子。

表2表示了对所支持的数据格式的包大小约束。每个包的长度必须是表格中的数值的倍数。为简单起见,所有的数据格式例子都是单数据通路(single lane)配置。

多数据通道(Multi-Lane)

数据通道Lane是可扩展的,当需要传输的视频信号带宽大于一个数据通道所能承载的极限时,或者试图避免高时钟速率的场合应用时,可以将数据通路扩展为两个,三个或者四个,总线带宽可以获得近似线性的增加。

带宽和数据速率

定义

像素时钟pixel-clock — 传输单个像素的时钟,一般为MHz

带宽 Bnadwidth — 给定系统通过特定频率数据的能力

数据速率 Data Rate — 传输层每秒比特流的吞吐量

带宽和数据速率计算

在本章中,将总结怎样计算带宽和数据传输速率

像素时钟(MHz)

如果视频格式是标准的,像素时钟频率可以通过SMPTE/CEA或VESA的标准来获得。或者通过下面的等式来计算出:

Pixel Clock Frequency = Total Horizontal Sample × Total Vertical Lines × Refresh Rate

Total Horizontal Sample 和Total Vertical Line包括blanking period(消隐区域),Refresh Rate可以称之为帧频率或者垂直频率。

Total Data Rate或Bandwidth(Mbps/ Gbps)

给定视频格式的带宽(Bandwidth)是像素时钟频率和像素大小的乘积。CMOS传感器接口的总数据速率(Total Data Rate)必须与带宽(Bandwidth)相匹配。

Total Data Rate(Bandwidth) = Pixel Clock Frequency × Pixel Size(in bits)

每个数据通道的数据速率Data Rate per Lane(Mbps / Gbps)

每个Lane的数据速率是总的数据速率(带宽 bandwidth)除以总的数据通道数。CSI-2最大支持4个数据Lane.

Data Rate per Lane=Total Data Rate ÷ Number of Data Lane

位时钟 bit clock(MHz)

因为MIPI数据通道Lane是一个DDR(double data rate)接口,所以CSI-2的位时钟频率是每个通道的数据时钟速率的一半

Bit clock frequency = Data Rate per Lane ÷ 2

例子

器件选择

硬件特点

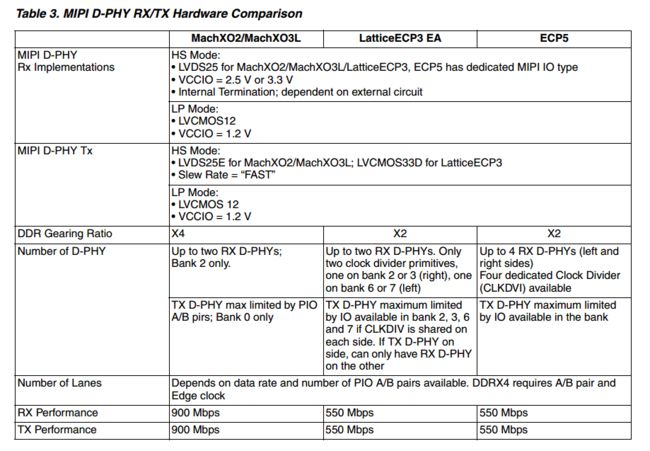

表3表示使用MachXO2 ,MachXO3L,Lattice ECP3 and ECP5 device families 的MIPI D-PHY硬件实现特性。对MIPI D-PHY接收器和发送器的资源利用情况和设计性能等更详细的细节,请参考RD1182文档。