将Arduino与开源RISC-V架构相结合,实现低成本,高性能嵌入式设计

嵌入式系统开发人员一直在寻找进一步缩短开发时间的方法,尤其是概念验证和快速原型开发。开发工具包(开发工具包)已经成为选择的捷径,但设计者需要能够平衡表单因素和广泛支持的生态系统与性能需求。

Arduino Uno开发板是这需要找到平衡的一个很好的例子。其形成因素已成为非常受欢迎的在这一领域,由于其成本低和数以百计的Arduino Shields提供Arduino的I/O功能插件扩展的可用性。然而,一些开发人员可能希望某些嵌入式应用程序比8位微控制器提供更多的性能。

对他们来说,解决方案可能躺在hifive1开发套件从人群供应。本文介绍了低成本hifive1开发套件,论述其特点使高性能嵌入式系统的快速原型设计,并介绍了可以帮助设计师开发工具开始。

什么是hifive1?

的hifive1开发套件是基于微控制器包含一个32位的RISC-V(发音为“风险五”)处理器核心(图1)。董事会接受了Arduino风格的盾牌,大大扩大嵌入式快速原型设计的实用。

图像的人群提供hifive1 Arduino兼容开发板

图1:hifive1 Arduino开发板兼容的微控制器采用基于32位RISC-V处理器核心。(图片来源:凯利讯半导体)

在hifive1心RISC-V处理器核心。这需要开源概念背后的Arduino板,并延伸它所有的方式到处理器本身。RISC-V指令集架构是一个开放(ISA)牢固建立在两个基础之上:精简指令集计算机(RISC),在上世纪80年代以来的概念,和开源的原则。因为它是开源的,RISC-V ISA可自由用于任何目的。任何人都可以设计,制造,销售和支付版税risc-v-based芯片和软件。

的risc-v-based单片机对hifive1板可编程以支持执行到位(XIP)期间减少指令缓存笔芯SPI命令架空方式。单片机的四SPI(QSPI)端口支持32字节的突发读取加速指令缓存笔芯从QSPI闪存来提高性能使用内存的XIP模式。

微控制器可以运行在320 MHz的时钟速率更快,但在hifive1板应限制在不超过133兆赫,使单片机的SPI串行时钟在董事会的128兆位QSPI闪存的限制操作。

Arduino的风格的标题-注意事项

开发套件的hifive1复制Arduino的独特的I / O头布局。它将接受许多可用的Arduino Shields的数百名有几个需要注意的问题。

首先,微控制器没有模拟输入引脚。只有数字I/O、中断和脉冲宽度调制(PWM)引脚分配是可能的hifive1 Arduino开发套件的风格的标题。物理头位置用于A0 A5模拟引脚上Arduino UNO板标有数字I/O引脚,通过对hifive1委员会D19 D14。如果添加的模拟功能是必要的,使用许多可用的模数转换器(ADC)是可能的,数字模拟转换器(DAC),或组合的ADC / DAC的Arduino Shields。

也请注意:

设计者可以指定多达九个PWM发生器Arduino风格头引脚上hifive1开发套件。

所有19的hifive1 Arduino开发套件的风格标题的I / O引脚可以作为中断输入。

船上的电压转换器给弹性为3.3伏或5伏的逻辑水平基础上的跳线设置所有的hifive1开发套件的数字I/O引脚。一个跳线设置(标记Ioref在板图1)对所有的I/O引脚上的hifive1 Arduino开发套件的风格标题的逻辑层次。

这就引出了第二警告:只有以下两Adafruit Arduino Shields已测试的hifive1至今,虽然Adafruit的支持库这两盾已经移植到hifive1图书馆:

Adafruit的电阻式触摸屏和LED显示屏

Adafruit的BLE SPI的朋友

就是说,任何盾,SPI,UART通信,或数字I/O应该易于使用的hifive1,虽然支持库可能需要小的调整。它仍然是非常早期hifive1外围护库:希望支持盾增多。

好的硬件需要良好的软件支持

为hifive1开发工具包软件开发工具可以在GitHub。这些工具包括一个C编译器和汇编器的RISC-V处理器架构,GDB调试器的RISC-V主机处理器,和RISC-V版本(片上调试)openocd。

一旦它的编写,编译,安装,开发者上传程序到hifive1开发套件通过USB调试接口。的hifive1店在其板上的SPI闪存芯片的程序。板载闪存芯片具有16 MB的容量,使它远远大于代码存储可在一个8位Arduino Uno板。这个地址空间的扩展是一个32位处理器体系结构的优点,risc-v.微控制器的片上SRAM的16字节也比较大。

董事会的核心

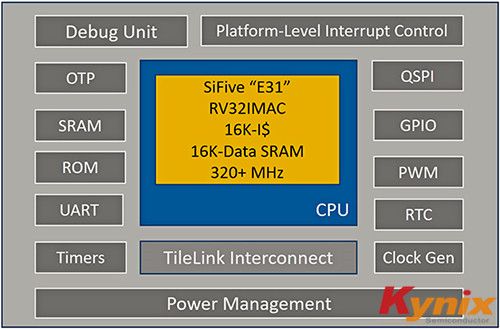

在hifive1单片机开发套件的心熊仔细一看(图2)。

这个开源的简化框图risc-v-based单片机

图2:简化的块图risc-v-based开源微控制器。(图片来源:凯利讯半导体)

单片机的中心是CPU核心,它是基于开放源代码的,32 RISC-V ISA。在RISC-V说,核心是一个rv32imac处理器,这意味着它使用32位整数指令集基础RISC-V(rv32i)整数硬件乘法和除法(M);原子,实时指导(一);和额外的支持16位的紧凑型(C)指令集。有64和128的RISC-V ISA位版本以及。核心还包括16字节的指令高速缓存(称为“我”的图)和16字节的ScratchPad SRAM。几个标准的外设,包括定时器、PWM信号发生器、实时时钟、UART、QSPI的串行接口,和一个片上硬件调试模块环绕处理器核心。

谁或后面的RISC-V的体系结构,是什么和为什么?

的hifive1开发套件和微控制器实际上是硬件演示车辆为开源RISC-V处理器架构,乞讨的问题:难道世界真的需要另一个处理器架构?

RISC-V项目位于伯克利的加利福尼亚大学开始,最终超越大学的围墙,抓住更多的志愿者和在电子行业工作的人的想象力。该项目的最终结果是一个开源的RISC处理器ISA(指令集架构),它和其他32位RISC ISA一样好。不同的是,RISC-V ISA可以被任何人自由地用于任何目的。

它需要一个生态系统。

与hifive1板,嵌入式系统开发者需要的不仅仅是一个处理器或微控制器芯片。对于嵌入式开发人员需要开发RISC-V,支持工具,表格的示例代码,库和软件栈。这种支持来自于成功的处理器架构和来自用户的生态系统。RISC-V处理器体系结构是比较新的,所以它的生态系统,但它的增长。除了开发工具从sifive上面所讨论的,其他的开发工具在RISC-V生态系统目前包括:

开源GNU单片机Eclipse,Eclipse的插件和工具,基于GNU工具链的多平台的嵌入式开发的一个家庭。

Segger的嵌入式工作室RISC-V,跨平台IDE嵌入式C/C++软件开发公司的J-Link调试探针。

结论

Arduino Uno开发板的廉价外形小,重量轻,并访问了成百上千的I / O和周围的盾牌。利用现有的hifive1开发套件的盾牌和伴侣,他们一个32位单片机的risc-v-based密切复制紧凑的Arduino Uno板的外形和独特的封头结构。

更大的hifive1开发工具包代码存储能力有车载16兆字节的闪存。虽然这是一个新的架构,有一个萌芽的开源生态系统提供了一个扩大RISC-V的软件开发工具套件,包括一个编译器、汇编器、调试器和Arduino IDE图书馆。