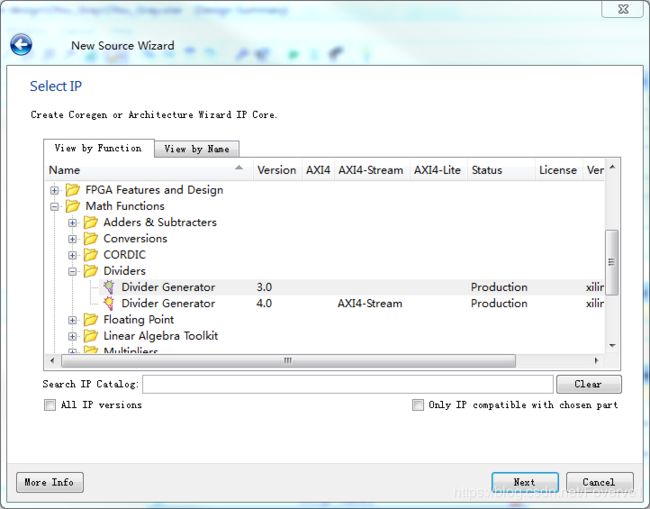

ISE之除法器IP CORE使用总结

IP CORE选择:

Algorithm Type:Radix2: Radix-2 non-restoring integer division using integer operands, allowing either a fractional or integer remainder to be generated. This is recommended for operand widths less than around 16 bits or for applications requiring high throughput.

使用整数操作数的Radix-2非恢复整数除法,允许生成小数或整数余数。 对于小于16位的操作数宽度或需要高吞吐量的应用程序,建议使用此选项。

High Radix:High Radix division with prescaling. This is recommended for operand widths greater than around 16 bits. This implementation uses XtremeDSP slices and is not available for devices that do not have XtremeDSP slices.

具有预定标的高基数分裂。 建议操作数宽度大于16位。 此实现使用XtremeDSP切片,但不可用没有XtremeDSP切片的设备。

Dividend and Quotient Width:被除数和商的宽度

Divisor Width:除数宽度

Remainder Type:Remainder:余数

Fractional:商的小数(用整数表示,按比例扩大一定倍数)

Fractional Width:小数宽度:如果选择小数类型,则确定在分数端口输出上提供的位数。

Operand Sign:选择输出类型是有符号数还是无符号数

Latency Configuration:延迟配置 Automatic or manual:自动或者手动

Latency: When Latency Configuration is set to Automatic, this field provides the latency from input to output in terms of clock enabled clock cycles. When Manual, this field is used to specify the latency required.

延迟:当“延迟配置”设置为“自动”时,此字段根据启用时钟的时钟周期提供从输入到输出的延迟。 手动时,此字段用于指定所需的延迟。

Clocks Per Division: Determines the interval in clocks between new data being input (and output)

每个时钟区:确定输入(和输出)的新数据之间的时钟间隔

Detect Divide-by-Zero: Check box. Determines if the core has a DIVIDE_BY_ZERO output port to signal when a division by zero has been performed.检测除零:复选框。 确定核心是否具有DIVIDE_BY_ZERO输出端口,以便在执行除零时发出信号。

Number of iterations: Read-only text field that reports the number of iterations performed by the High-Radix engine for each divide. This sets the maximum throughput of the divider. To achieve this throughput, the operands must be supplied as soon as requested by the core RFD output.迭代次数:只读文本字段,用于报告High-Radix引擎针对每个除法执行的迭代次数。 这设置了分频器的最大吞吐量。 要实现此吞吐量,必须在核心RFD输出请求后尽快提供操作数。

Throughput: Read-only text field that reports the maximum throughput that can be sustained by the divider when operands are supplied at a constant rate. This rate is controlled by ND and is not governed by RFD (that is, RFD will be high when ND is applied at this rate).吞吐量:只读文本字段,报告在以恒定速率提供操作数时分频器可以维持的最大吞吐量。 此速率由ND控制,而不是受RFD支配(即,当以此速率应用ND时,RFD将很高)。

CE: Check box. Determines if the core has a clock enable input.

SCLR: Determines if the core has a synchronous clear input.

SCLR/CE Priority: Determines which of SCLR or CE has priority over the other.

CE:复选框。 确定内核是否具有时钟使能输入。

SCLR:确定核心是否具有同步清除输入。

SCLR / CE优先级:确定SCLR或CE中的哪一个优先于另一个。

RFD:An output that indicates the cycle in which input data is sampled by the core. This is only applicable to cores where Clocks per Division is not 1. For the case of Clocks per Division is 1, the core samples the inputs on every enabled clock rising edge; hence, RFD will always be High.When Clocks per Division is either 2, 4, or 8, the core only samples data on every 2nd, 4th, or 8th enabled clock rising edge, respectively. The cycle on which data is sampled is indicated by RFD.

一个输出,指示核心对输入数据进行采样的周期。 这仅适用于每个分频时钟不为1的内核。对于每个分频时钟为1的情况,内核在每个使能时钟上升沿采样输入; 因此,RFD将始终为高。当每个分频的时钟为2,4或8时,内核仅分别在每个第2,第4或第8个使能时钟上升沿采样数据。 采样数据的周期由RFD指示。 这对延迟的定义很重要,简而言之就是数据已经准备好,核可以采集数据了

RDY:Signals that a result is available at the output of the core.表示结果在核心输出处可用。

New Data (ND). Used to signal to the core that new operands are present on the input to the core.用于向核发信号通知核,输入上存在新操作数。