使用ISE创建IP核(以加法器的IP核建立为例)

IP核介绍:

IP(知识产权)核将一些在数字电路中常用但比较复杂的功能块,如FIR滤波器,SDRAM控制器,PCI接口等做成一个“黑盒”或者可修改参数的模块,供设计者使用。IP核包括硬IP与软IP。调用IP核能避免重复劳动,大大减轻设计人员的工作量。

IP Core生成器(Core Generator)是Xilinx FPGA设计中的一个重要设计工具,提供了大量成熟的、高效的IP Core为用户所用,涵盖了汽车工业、基本单元、通信和网络、数字信号处理、FPGA特点和设计、数学函数、记忆和存储单元、标准总线接口等8大类,从简单的基本设计模块到复杂的处理器一应俱全。配合Xilinx网站的IP中心使用,能够大幅度减轻设计人员的工作量,提高设计可靠性。

Core Generator最重要的配置文件的后缀是.xco,既可以是输出文件又可以是输入文件,包含了当前工程的属性和IP Core的参数信息。

下面介绍在ISE中新建IP类型的源文件来启动Core Generator的方法:

1)在ISE Project Navigator新建工程,在工程管理区单击鼠标右键,在弹出的菜单中选择New Source,选中IP类型,在File Name文本框中输入adder(注意:该名字不能出现英文的大写字母),然后点击Next按键,进入IP Core目录分类页面,如下图示:

点击Next,以加法器模块为例介绍,找到并选中Math Funcation Adder & Subtracter Adder Subtracter v11.0,如下图:

点击Next,进入Summary界面,点击Finish,弹出一个Adder Subtracter 配置界面,如下图:

配置信息如上,根据自己的需求进行配置,配置完成后点击Generate,若在工程管理区出现一个“adder.xco”的文件。这样加法器的IP Core已经生成并成功调用。

如下图示单击adder.xco,双击View HDL Instatiation Template,即可复制,在Verilog HDL中例化adder IP核。

实例解析:

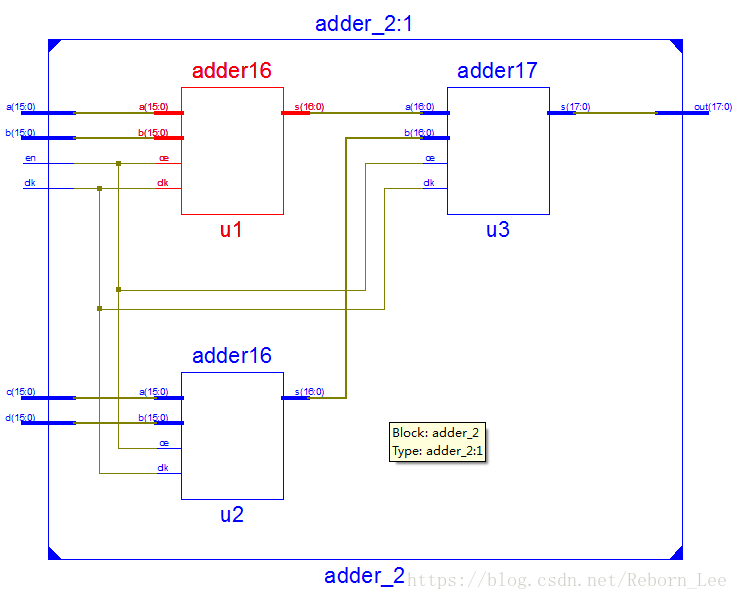

例:调用加法器的IP core,并用其实现图4-15所示的2级加法树。

按照上述方法,产生两个IP核,adder16和adder17,在verilog HDL源程序中例化即可实现上述加法树。其verilog HDL设计代码为:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 18:31:11 05/28/2018

// Design Name:

// Module Name: adder_2

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module adder_2(

input [15:0] a,

input [15:0] b,

input [15:0] c,

input [15:0] d,

input en,

input clk,

output [17:0] out

);

wire [16:0] out1, out2; //out1为a与b之和,out2是c与d之和

adder16

u1(

.a(a),

.b(b),

.clk(clk),

.ce(en),

.s(out1)

);

adder16

u2(

.a(c),

.b(d),

.clk(clk),

.ce(en),

.s(out2)

);

adder17

u3(

.a(out1),

.b(out2),

.clk(clk),

.ce(en),

.s(out)

);

endmodule

RTL schematic为:

测试文件为:

`timescale 1ns / 1ps

////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 18:50:40 05/28/2018

// Design Name: adder_2

// Module Name: F:/ISE_file/adder_IP/adder_2_tb.v

// Project Name: adder_IP

// Target Device:

// Tool versions:

// Description:

//

// Verilog Test Fixture created by ISE for module: adder_2

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////

module adder_2_tb;

// Inputs

reg [15:0] a;

reg [15:0] b;

reg [15:0] c;

reg [15:0] d;

reg en;

reg clk;

// Outputs

wire [17:0] out;

// Instantiate the Unit Under Test (UUT)

adder_2 uut (

.a(a),

.b(b),

.c(c),

.d(d),

.en(en),

.clk(clk),

.out(out)

);

always

begin

#10 clk = ~clk;

end

initial begin

// Initialize Inputs

a = 0;

b = 0;

c = 0;

d = 0;

en = 0;

clk = 0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

a = 15;

b = 25;

c = 45;

d = 85;

en = 1;

end

endmodule

仿真结果为:

(仿真结果是否有问题,有待确认)

参考地址