实验报告来自电子科技大学中山学院 _ 数字逻辑电路设计课程

1.实验目的与要求

通过实验,能够掌握译码器和选择器的原理和应用。

2.实验设备

硬件:PC机 一台

数字电路实验教学平台 一台

软件:Quartus II集成开发环境

3.实验内容

(1) 3-8译码器(74138)功能测试;

(2) 利用74151实现对输入数据进行选择。

4.实验预习要求

(1) 仔细阅读课本第二章的译码器、数据选择器,理解译码器、数据选择器的原理和功能。

5.基础知识

(1)键盘

键盘是计算机系统中最常见的输入设备,通过键盘按下或没有按下时键盘两端的金属片的导通或断开状态来标识指令。如图3.1是市场常见的键盘。

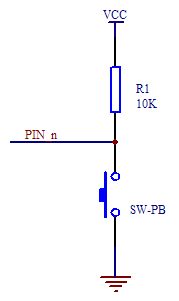

如图3.2所示,是单个键盘电路的典型连接方法。当键盘按下后,FPGA的管脚PIN_n与地相连,键盘输出状态为低电平;当键盘未按下,由于上拉电阻的作用,键盘输出状态为高电平。

为了用更少的管脚实现对多个键盘的控制,数字逻辑电路实验平台采用行列式连接方法,如图3.3所示。

当没有键盘按下时,由于上拉电阻的作用,KEYC1、KEYC2、KEYC3、KEYC4输出状态都为高。如果行控制线KEYL1、KEYL2、KEYL3不输出,则由于下拉电阻的作用,所有与行控制线KEYL1、KEYL2、KEYL3相接的键盘一端都为低电平。此时只能通过KEYC1、KEYC2、KEYC3、KEYC4区分四种不同的按键值,即KEY1、KEY5、KEY9其中之一的键盘按下后,KEYC1输出低电平;KEY2、KEY6、KEY10其中之一的键盘按下后,KEYC2输出低电平;KEY3、KEY7、KEY11其中之一的键盘按下后,KEYC3输出低电平;KEY4、KEY8、KEY12其中之一的键盘按下后,KEYC4输出低电平。

(2)蜂鸣器

蜂鸣器是一种一体化结构的电子发声器件,广泛应用于计算机、报警器、电子玩具、电话机、定时器等电子产品中,如图3.4为市场上常见的蜂鸣器产品,一种是有源蜂鸣器,另一种是无源蜂鸣器。

有源蜂鸣器直接接上额定电源就可连续发声,有源蜂鸣器工作的理想信号是直流电。因为蜂鸣器内部有一简单的振荡电路,能将恒定的直流电转化成一定频率的脉冲信号,从而实现磁场交变,带动钼片振动发音。但是在某些有源蜂鸣器在特定的交流信号下也可以工作,只是对交流信号的电压和频率要求很高,此种工作方式一般不采用。 无源蜂鸣器则和电磁扬声器一样,需要接在音频输出电路中才能发声,原因在于内部没有驱动电路。无源蜂鸣器工作的理想信号是方波。如果给预直流信号蜂鸣器是不响应的,因为磁路恒定,钼片不能振动发音。

一般的,两种蜂鸣器外观上看有些不同,如图 3.4(1)、(2),蜂鸣器背面可以看出有绿色电路板的一种是无源蜂鸣器,没有电路板而用黑胶封闭的一种是有源蜂鸣器。当然从外观上看多数可以这样判断,而最准确的判断方法可以用万用表电阻档 Rxl 档来测试:用黑表笔接蜂鸣器 "+"引脚,红表笔在另一引脚上来回碰触,如果触发出咔、咔声的且电阻只有 8 (或 16 )的是无源蜂蜂鸣器;如果能发出持续声音的,且电阻在几百欧以上的,是有源蜂鸣器。有源蜂鸣器直接接上额定电源(新的蜂鸣器在标签上都有注明)就可连续发声;而无源蜂鸣器则和电磁扬声器一样,需要接在音频输出电路中才能发声。

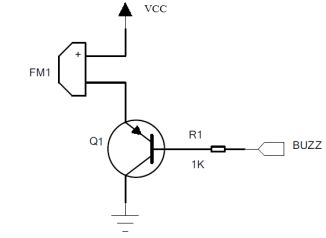

实验平台采用的蜂鸣器控制电路如图3.5所示,我校开发的数字逻辑电路平台采用的是有源蜂鸣器。

5.实验原理

(1) 74138是3位自然二进制编码的全译器,将输入的3位自然进制编码的8种取值分别译码输出,译码输出端的个数是23=8个。74138有一个高电平使能信号G1、2个低电平有效的使能信号G2AN和G2BN,只有当G1为1,G2AN和G2BN为0时,译码器才使能。74138的逻辑符号如图3.6所示。74138的A、B、C为地址输入端,Y0N~Y7N为8个状态信号输出端,在Quartus II中,74138的G1默认为高电平,G2AN和G2AN默认为低电平。三个控制输入端决定电路的状态。

在实验时,可以通过VCC或者GND设置成高电平或者低电平,也可以通过拨码开关设置A、B、C为地址输入端;Y0N~Y7N的输出状态可以通过 LED0~LED7的亮暗来观察。

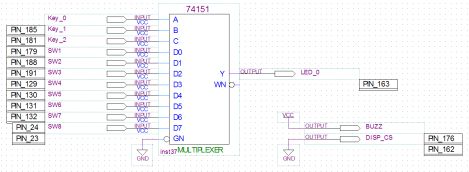

(2) 8选1数据选择器74151逻辑符号如图3.2所示。芯片信号输入脚为低电平时芯片被选中。A2A1A0用于指定从8个数据输入端D0 ~D7中选择一个输出,当地址为i时,被输出的数据是Di。A2A1A0可连到拨码开关来选择输出数据。2个输出端Y和是相互反相的信号,Y是高电平有效的输出端,当芯片选未被选中时,输出低电平;当芯片选中时,输出Di。的输出总与Y相反。D0 ~D7接到不同的信号脚上,Y和接到LED灯的信号脚,通过选择A2A1A0的输出地址,Y和可以看到数据选择的结果。

在实验时,数据选择端A2A1A0可以通过接VCC或者GND来选择,也可以通过接3个拨码开关进行数据选择。8个数据输入端D0 ~D7可以直接接VCC或者GND,也可以接上8个拨码开关来设置数据。

在数字电路实验教学平台各个LED管对应的FPGA控制管脚如表1.1所示:

表1.1 各LED管对应的FPGA控制管脚

| DISP_CS | LED0 | LED1 | LED2 | LED3 | LED4 | LED5 | LED6 | LED7 | Buzz(vcc) |

|---|---|---|---|---|---|---|---|---|---|

| 162 | 163 | 164 | 165 | 168 | 169 | 170 | 171 | 173 | 176 |

拨码开关对应的FPGA控制管脚表1.2所示:

表1.2 拨码开关对应控制管脚

| SW1 | SW2 | SW3 | SW4 | SW5 | SW6 | SW7 | SW8 |

|---|---|---|---|---|---|---|---|

| 188 | 191 | 129 | 130 | 131 | 132 | 24 | 23 |

按键和蜂鸣器对应的FPGA控制管脚表1.3所示:

表1.3 按键和蜂鸣器对应控制管脚

| KEY1 | KEY2 | KEY3 | KEY4 | BUZZ |

|---|---|---|---|---|

| 185 | 181 | 179 | 175 | 176 |

6.实验步骤

(1) 启动Quartus II,利用建立工程向导建立一个工程文件。

(2) 选择File->New->Block Diagram/Schematic,建立一个原理图输入文件。

(3) 双击原理图空白处,输入所要添加的器件(74138、74151等),然后设置引脚的输入、输出值,编译通过后对引脚进行IO分配。

(4) 把编译成功的文件下载到核心板上,观察结果。

(5) 填写实验报告(可以在背面填写或者另添纸填写)。

(6) 完成基本实验后可以设计自己的实验,视情况进行加分鼓励。

实验三 组合逻辑电路应用——译码器、数据选择器

基础实验

0.试电路

1.设计74138验证实验电路,并根据图表要求填写输出结果。

| G1 | G2AN | G2BN | C | B | A | Y0N | Y1N | Y2N | Y3N | Y4N | Y5N | Y6N | Y7N |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| L | X | X | X | X | X | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| H | L | L | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| H | L | L | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| H | L | L | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

2.给出74151验证电路图,分析其原理,并根据图表要求填写输出结果。

| A | B | C | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | Y | Wn |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

高级实验

请用按键以及学过的逻辑电路设计一键盘控制电路, 要求当KEY1按下时在8段数码管上显示1,KEY2按下时在8段数码管上显示2,KEY3按下时在8段数码管上显示3,按下KEY4时蜂鸣器响一声。