彻底掌握Quartus——基础篇

你可以在EETOP的论坛上面搜索到quartus的下载链接,然后在百度能找到破解方法。

不建议用quartus13以前的版本(旧版带的USB blaster驱动可能在WIN8、WIN10上面安装不了),还有quartus13及以后的版本都把IDE和器件包分成两部分,记得下载器件包。此外,quartus13.0sp1是最后一个支持cyclone II的版本。

接下来,介绍Quartus 13最基础的日常使用方法。

如何新建工程就不说了,但是要注意,工程目录和工程名不要有中文和空格,还有,要有一个设计文件(如,.v、.vhd、.bsf文件)的名称要跟工程名一样,不然会有警告。

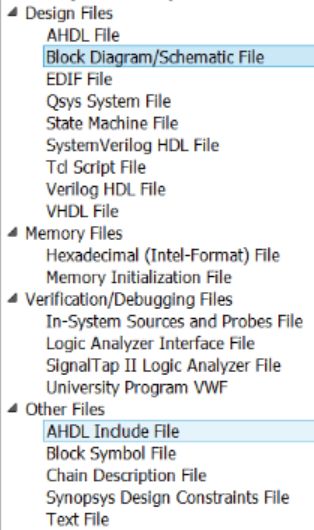

一、新建工程,New个设计文件,会出现下图所示。

上面那么多种文件有什么卵用?

1、AHDL文件,用于编写Altera发明的AHDL语言,此语言已经被淘汰,可以不管它。

2、Block Diagram/Schematic文件,原理图文件,跟AD、PADS、Cadence等电路图设计软件的用法差不多。

3、EDIF文件,网表文件。

4、Qsys system文件,用于设计软核,Qsys前身是NIOS。

5、State Machine文件,状态机文件。

6、System Verilog文件,用于系统级验证。

7、Tcl script文件,TCL脚本文件。

8和9、常用的HDL文件(包括verilog和VHDL)

10是十六进制文件,11是MIF文件,用于ROM或RAM的初始化。

12、Probe文件,用于观察FPGA内部某一信号,一般用Signaltap

13、 逻辑分析仪接口文件,暂时不知道有什么用。

14、VWF文件,用于调用quartus自带的仿真工具QSIM

15、AHDL头文件,可以不管它。

16、原理图的Symbol文件,用于编辑原理图Symbol,跟你用电路图设计软件时,画原理图库差不多。

17、JTAG链描述文件,给一个或多个芯片下载代码时用的。

18、Synopsys约束文件,时序约束用的SDC文件。

19、txt文件。

就算quartus支持那么多种文件,但常用的没几个,一般是原理图.bdf文件或者纯文本的.v或.vhd文件,就算后面需要用逻辑分析仪或者时序约束,也是可以用quartus自动给你生成的。

特别要注意一下,不同类型的文件,名字最好不一样。比如,已经有了test.v,就不要用弄test.vwf,不然你双击test的原理图Symbol的时候,会问你要打开test.v还是test.vwf,让你浪费不必要时间。我一般是除了.v或.vhd文件用test之外,vwf就用test_vwf.vwf,bdf就用test_top.bdf。

二、如何把HDL文件,转成原理图Symbol

先选中你要转的HDL文件。

![]()

白色衬底(左边)是被选中的HDL文件,右边是没有选中的,然后在菜单栏File下面。

点Create Symbol Files for Current File,即可把HDL转成原理图Symbol了,然后新建一个.bdf的原理图文件。

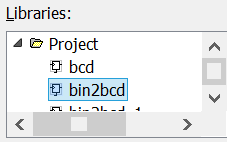

双击红圈位置,在libraries->Project下,已经生成了原理图Symbol了,点OK,可以调用了。(我的机子是高分屏,Symbol显示有点问题,是quartus对高分屏支持得不好)。

如果你觉得原理图的symbol不够大,可以按住Ctrl键,滑动鼠标滚轮,可以使symbol放大/缩小。

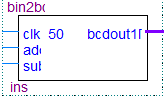

再来对照一下,原理图Symbol和.vhd文件的实体

entity bin2bcd is

port(

clk_50M : in std_logic;

add : in std_logic;

sub : in std_logic;

bcdout1 :out std_logic_vector(3 downto 0)

);

end bin2bcd;

这是一一对应,输入在左,输出在右,有多个输入的时候,也会按顺序排列,如果不方便连线,可以改一下引脚的顺序,再保存,生成Symbol,再update。

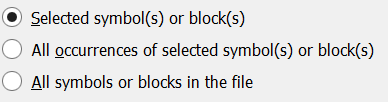

右击Symbol,就可以update了,update时,会出现下面的对话框。

懂点英语的,都能看懂上面三个选择。1、只update选中的symbol,2、update所有关联(名字一样)的symbol,3、update全部symbol。一般选第一个。

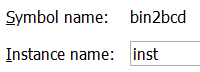

quartus13有个bug,生成的symbol的实例名可能会重名,而报警告。这时,可以右击symbol,选properties。

把上图的inst改成其它名字就可以了。

三、在刚才调用symbol的位置,还可以调用其它IP核。

在Name下面输入input,可以调用输入端口,output就是输出端口了,这些都是quartus自带的一些symbol,把primitives下面的折叠全部打开,你会发现有很多东西,如:与或非门、各种触发器等。当然,还有其它东西,自己去挖掘吧。特别要说明两个symbol,VCC代表高电平,GND代表低电平,可用于使能或者其它用途。

也是在刚才那个对话框,下面有MegaWizard,用来调用quartus自带的IP核,也叫宏功能模块(LPM),有部分是免费,部分是收费,还有部分需要联网下载的。

MegaWizard的使用方法也很简单,写上IP核的名字,一步步next到finish就可以了,调用也是在上面那个对话框里调用。

其中,原理图symbol之间的连线要注意一下位宽,不然会出错。也可以使用网络标号,先把线引出来,选中线,再输入网格标号就可以了,但是要注意一下格式,如:qout是8位,网络标号就要写成qout[7..0]。也有些特殊用法,如下图所示:

这里,引出64位宽的fre信号,而在另一个symbol则只连了[63..32]这几个脚,这是合法的,空出来的引脚,没用的话,可以不管。

四、编写好你的设计文件之后,就可以编译(也可以叫综合)了。因为综合很慢,所以先分析一下设计文件有无语法错误之类的,再综合。

综合的时候,要注意,哪个是顶层文件。比如你弄一个流水灯,在led_top.bdf里面,有分频模块fre_div的symbol和流水灯控制模块led_ctrl的symbol的话,那么led_top.bdf就是顶层文件,因为它调用了你所有的设计文件。你可以先选中led_top.bdf,再用快捷键Ctrl+Shift+J,把它设置为顶层文件,不然综合出来有很多警告,甚至出错。

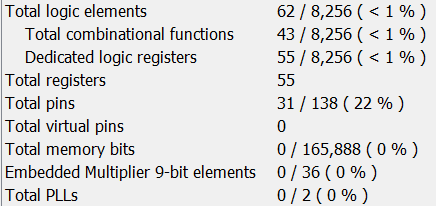

上图所示,蓝圈就是分析设计文件了,而红圈就是综合。综合之后,就会生成report,告诉你,你设计出来的电路占用哪些资源。

懂点英文和FPGA的内部结构的,都能看懂上图。现在解释一下:

1、电路占用了62个LE。

2、电路占用了43个组合电路。

3、电路占用了55个专用的寄存器。

4、整个电路占用了55个寄存器。

5、电路使用了31个引脚,我的FPGA是EP2C8Q208C8N,一共有208个引脚,其中138个引脚是可用的。

6、电路使用了0个虚拟引脚,虚拟引脚是前期设计时,预先分配的,可以解决引脚不够用导致无法综合的问题。

7、电路使用的内存为0 bit,这里memory是指FPGA内部的存储单元,包括ROM和RAM,其中RAM指的是块RAM而不是分布式RAM,因为分布式RAM是用LE实现的。

8、电路使用了0个PLL,我这芯片一共有2个PLL,PLL是固核(也可以认为是硬核,硬核和固核的分界线并不是很明确),可以配置一下就调用,某些FPGA会有4个或更多的PLL固核。

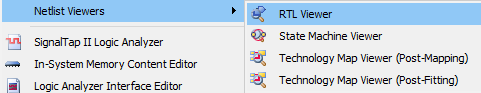

五、接下来看看,你综合出来是个什么电路。在菜单栏的Tools下面,点击查看RTL图、状态机图(前提是综合出来有状态机)或者工艺映射表(Technology Map)

其中RTL图和工艺映射表,都可以表示你设计出来的电路,区别在于,RTL图抽象层次更高一些,而工艺映射表更接近于门级。

某些时候,RTL并不能完全表示出电路的正确性,因为综合出来,有部分细节出错,在RTL图看不出来,这里得用工艺映射表。

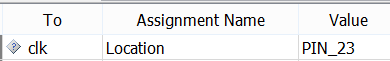

六、用Assignment Editor锁管脚。

在Value下面输入23,就可以把clk锁定在23号引脚了。如下图所示。

七、锁完之后,保存好,还要再综合一次,这样的综合出来的电路才是你需要的。如果不想综合两次,那就要用TCL脚本来锁管脚了。

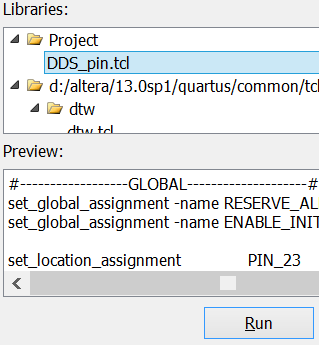

新建一个TCL脚本文件。输入如下代码:

set_location_assignmentPIN_23 -to clk

这样就可以把clk锁定在23号引脚了。如果你的引脚是按键,就要加上拉电阻(不然会容易烧坏IO口),输入如下代码:

set_location_assignmentPIN_208 -to switch_input

set_instance_assignment -name WEAK_PULL_UP_RESISTOR ON -to switch_input

这样就把switch_input这个锁在208号引脚,同时给208号引脚加了上拉电阻。

保存好你的TCL脚本,然后在菜单栏的tools下,点TCL scripts,

点Run,运行一下你的TCL脚本。这样,就只需要综合一次了。

八、接好你的JTAG就可以用Programmer下载代码了,由于此步骤太简单了,省略。

其中sof文件,是直接JTAG下载的,断电就没了;pof文件是AS下载,断电可保存。但是AS下载需要额外加点电路,而且对电路要求高,有点问题都无法下载,而且工业上的板子也只有JTAG下载口(节省PCB面积),这样就得用JTAG间接下载,断电可保存。

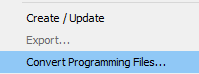

在菜单栏的file下,转换编程文件:

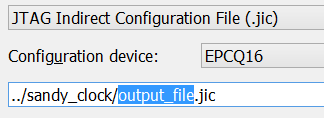

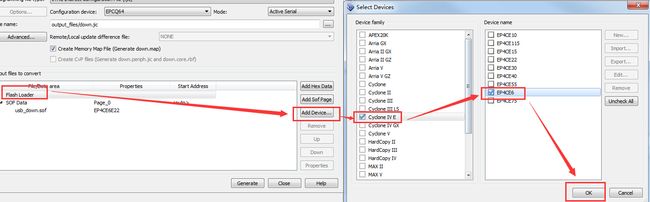

选择jic格式,配置芯片的型号(我这里是EPCQ16),然后改一下jic的名字,默认是output_file。

先设置一下flash loader(在Select Devices要选择你所用的芯片系列,下图为参考)。

再点一下SOF Data

然后add file,把你的SOF文件添加进去。

然后点generate即可生成jic文件。(你也把上面这些配置保存为.cof文件,以后可以重复使用)

最后在programmer,添加这个jic文件,就可以下载代码了。下载完之后,FPGA并不直接运行代码,需要先断电,再上电,FPGA才正常工作。