加法器

你的打赏是我奋笔疾书的动力!

一切为了乱学的几篇网贴,以免遗忘,故记之。

Wiki讲加法器是一种用于执行加法运算的数字电路部件,是构成电子计算机核心微处理器中算术逻辑单元的基础,加法器主要负责计算地址、索引等数据,除此之外,加法器也是其他一些硬件,例如二进制数乘法器的重要组成部分。其中“数字电路”,“微处理器”,“算术逻辑单元”,别问我是什么意思,查查谷歌也是略知一二。

暂时搁过加法器,我们先来聊聊“门”,为什么先要聊聊“门”?“门”和加法器有什么关系?还先来看看“门”到底讲什么。古有艳照“门”,而今数模中有AND与门,OR或门,NOT非门,XOR异或门。他们说这些门都是逻辑电路,逻辑电路,没错,就是模拟逻辑的电路。模拟什么狗屁逻辑,完全不知道你在讲什么?有人急了,博主博主,你瞎几把乱扯小心天朝刑法。逻辑就是“门”前面的那个词,好,下面我们看看这四种逻辑在二进制的计数系统下是什么样子.

逻辑有了,接下来逻辑怎么用电路模拟呢?我们看到逻辑中有0,1输入,也有0或1的输出,对应到模拟电路上就是电路中的高低电压来表示,那么进一步思考如何设计电路使得输入高和低的电压,从而输出高或低的电压呢?这个就是靠晶体管这种电子元件来组合实现了,最开始的时候是用继电器来实现,这玩意我们在高中物理里面学到过,然而现在手机芯片里用到的都是场效应管,场效应管是什么?好吧,你非要打破饭碗问到底,我也无能为力,我只知道它能实现和晶体管一样的逻辑。

好,说到晶体管,wiki里讲是一种固体半导体器件,基于输入的电流或电压,改变输出端的阻抗,从而控制通过输出端的电流或电压,具体物理原理,查查谷歌也许可以略知一二,暂且搁过,后面再讲。

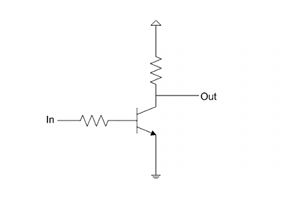

先来看看非门。晶体管的基极(Base)作为输入,集电极(collector)作为输出,发射极(emitter)接地。当输入为1(高电平),电流流向发射极,因此输出为0;当输入为0(低电平),电流从集电极流出,因此输出为1。

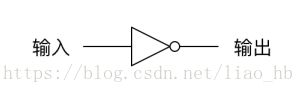

可以简记为下面的符号:

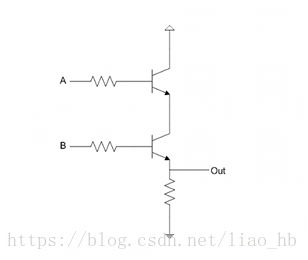

接着是AND。这需要两个晶体管,只有当两个基极的输入都为1(高电平),电流才会流向输出端,得到1。

可以简记为下面的符号:

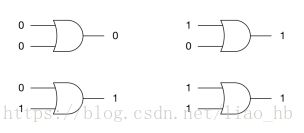

与上面逻辑表的对应图有:

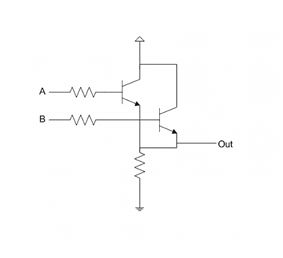

还有OR。这也需要两个晶体管,只要两个基极中有一个为1(高电平),电流就会流向输出端,得到1。

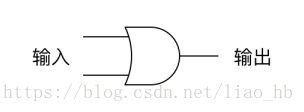

可以简记为下面的符号:

与上面逻辑表的对应图有:

最后是XOR。与门、或门、非门是三种最基础的门,所有其他逻辑运算都可以由这三种门组合得到。不过,为了方便起见,有一些常用的组合也有专门的名字,比如异或门(XOR)。

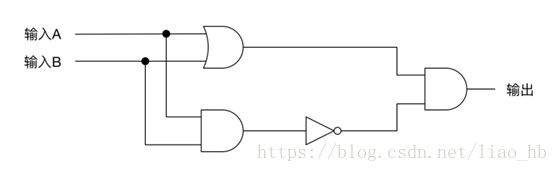

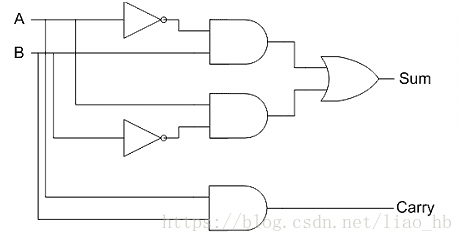

异或门结构可以有多种,我们给出2种,可把0或者1作为输入看看最后的输出是多少,验证一下异或的0-1逻辑

结构一:

A,B分别代入0或1,有四组输入,不难验证和上面的XOR逻辑表一致。

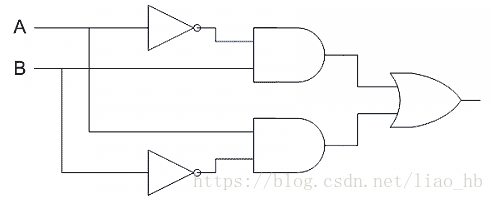

结构二:

同样验证可知和上面的XOR逻辑表一致。

结构三:……

以上就是各种逻辑门的电路图,各自都对应了一些有限规则的逻辑运算。把这些门放在前面讲,就是因为加法器的实现用到了这些基本的逻辑电路,好,下面我没来一步步看如何实现加法器.

先了解一位二进制数的加法是怎么加的?一共有4种情况的加法,分别如下:

0 +0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

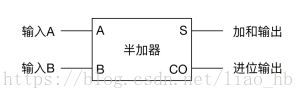

那你现在要考虑了,以为我们输入是2个信号,高低电压,我们的输出应该要设计几个信号呢?至少2个信号吧,至少让1 + 1 = 10这个输出占2个信号吧。那我们设计一位的二进制数加法器就很容易了,如下图:

图中输出和输入信号各有2个,进位输出望文生义就是指1 + 1 = 10中的“1”这个进位输出,加和输出是指一位二进制数的相加之和从右往左数第一位数,其实如果加和没有进位我们可以在和的左边补上假想进位数0,如下图:

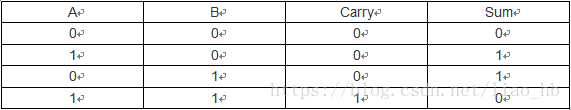

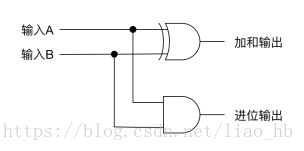

这个图"真值表",Carry就是进位输出,Sum是加和输出,我们可以看到,Carry一列的值可以由与门这个逻辑电路,Sum有没有对应的逻辑电路,有吧,没错就是异或门,那我们设计一位的二进制数加法器的电路就很容易了,无独有偶以下:(因为异或门的逻辑电路不止一个)

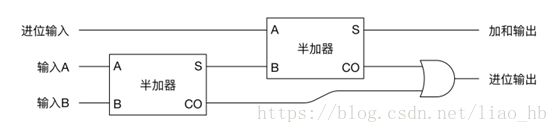

我们看到了上面的加法器的图示中有“半加器”字样,为什么是半加器呢?其实想一想一位二进制加法器有用吗,他只能处理以上四种0或者1的数字相加,而我们现实中的需求是成千上万的累加,累加的时候避免不了进位的操作,进位操作在半加器中无法体现,可是如果2个半加器叠加起来设计成如下电路,就有了进位的操作,然后把多个全加器串联,不就可以实现多位二进制加法了吗?

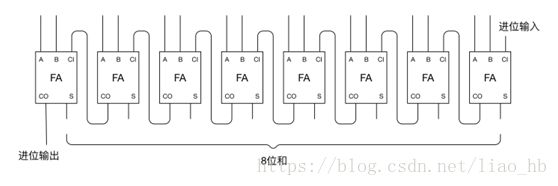

我们看到全加器的输入有3个信号,输出有2个信号,多个全加器的串联图如下:

上图是一个8位的加法器。

看了全加器,和8位加法器的电路设计图,有看官、老板肯定想付诸实践的冲动和欲望,然而说起来容易实现起来有点难,正所谓理论和实践之间其实也是有鸿沟的,大家都繁缛贴身我们还是看看就算了吧,这里有一个全加器的实物样例,和一个四位加法器的实物样例,上面的内容有一部分出自于这篇干洁的博文,自己琢磨下。

另外,实物图里的半导体晶体实在是大的可怜。而现在的晶体管的大小据目前的理论预测它的极限在3纳米左右,什么概念?有网据称7纳米已基本完成实验室阶段的研发,现在的晶体管,一个针头上就能放下大约3000万个。而摩尔定律告诉了我们一个睁眼见的事实,在芯片大小是一个硬性刚需的前提下,晶体管的大小被逼近原子大小,原子大小不可压缩,而摩尔定律还在发展,也就是说,芯片最终会被世界的发展速度所抛弃*_*。然而,也是据说,量子计算的发展可以翻盘这个尴尬,然而,量子计算机器势必是下一代的计算机时代。

若侵删!

转帖来自:

http://www.ruanyifeng.com/blog/2011/03/4-bit_computer.html

https://blog.oldj.net/2017/04/24/the-principle-of-adder/

-------------------------------------------------------------------------------------------------------------------------------------------------------------------------

再次加注:2018-10-27 14:35

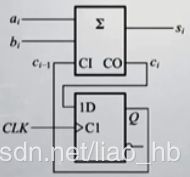

上面的加法器如果通电运行起来,2个8位数据的各个bit信号按照高电平为1,低电平为0的方式输入,我们会发现电路工作的时序是从右往左,一个一个全加器依次相加进位,最终有进位输出和其他8个bit位的输出;这样的加法器对每一个全加器的利用率是很低的(只有1/8),这是逻辑组合电路的设计,然而我们引入触发器后,会使得在8位相加的过程中,让全加器满负荷工作,这样的设计中考虑了暂存进位数据的思想,这种设计在数电中有一个名词叫时序电路设计,时序设计电路如下:

其中,ai,bi是2个8位数的每一位输入,ci-1就是每次按位相加前的进位输入,ci是每次位相加前的进位输出,它保存在触发器中,作为下一次按位相加的进位输入。si就是每次的按位相加后的输出位。

触发器的之所以能够储存电平信号,是因为电路中加入了一条输出到输入的(回环)反馈线路,从而使得输出端Q到输入端的回路中保持住电平信号。

你的打赏是我奋笔疾书的动力!

支付宝打赏:

微信打赏: