ARM(s5pv210)裸板驱动之(系统时钟1)

自从大家入行开始下至C51单片机上至n核arm架构cpu,时钟都贯穿始终。

平时我们说买了一台电脑cpu是几G的、几核几G的等,说的这个“G”就是主频,也就是时钟了。其实不是从事开发行业的人对这个也是很懂嘛。主频的高低决定这cpu 的运算速度,主频越高性能越强。对于我们开发人员来说仅仅了解这些是不够的。我们现在说的SOC芯片,一枚上面往往集成了很多片内外设。uart、nand、iic、spi等等他们都需要不同的时钟才能工作。为了让它们更好的工作还需要“倍频和分频”下面我们聊一辆常见的时钟结构。

一常见的时钟体系组成

1、外部时钟硬件+cpu,其实这种结构经常在帖子里见,但是我也是没有用过。可能是很早之前上学时见过实物但是记不清了。目前市场上主流的cpu都已经不是这种组成。

2、晶振+cpu内部时钟发生器 = 时钟。这个结构想必大家都不陌生,常在arm “M”级别cpu里常见,例如stm32、LPCxxx等等。这样组成有个特点,最终倍频后的主频都不是很高,72M、80M等,我用过最高的也就仅仅是204M(LPC4330)。这样的体系往往给人一种短小精悍的感觉。产品其实也蛮多的,只能手环、物联网产品等等,可运行裸板程序或者移植ucos、FreeRTOS等小型实施嵌入式系统使用。

3、晶振+cpu内部时钟发生器+倍频器+分频器 = 相应的时钟。这样的结构往往应用于主频可配置较高的芯片上,往往整个系统配有像linux、wince等这样的大型嵌入式操作系统。同时片内外设也较为丰富,故分频器是个重要的角色。

我们今天的主角s5pv210属于第三种结构。

外部晶振其实频率并不是太高,几十兆而已,需要通过cpu内部倍频,之所以这么设计,我觉得是一种成本的考虑,高速晶振毕竟很贵,可以想象成开车,想要达到高速,就得一档一档的往上升,不可能一下子用最高档位。我猜测可能也是更稳定的一种启动方式。毕竟晶振在电路印制板上是单独的存在,与cpu是用一定距离的且与周围的电路的位置不详,频率的上升必定会引起电磁兼容等问题。

但是为什么要倍频一次分频多次呢,为啥不单独一个个倍频呢,这个我查了一些资料显示,倍频器的设计和成本要大很多,分频成本要低很多。我打到目的尽可能少用倍频多用分频。个人拙见,希望明白人指点。

还有个一观点我们得明白,频率越高的不管是什么东西,都会带来高功耗的问题,同时发热量也会加大。在今后的帖子中我们说到低功耗处理的时候,会发现有个动作就是把不用外设时钟关掉,目的就是为了降低发热和功耗。

二、时钟系统简析

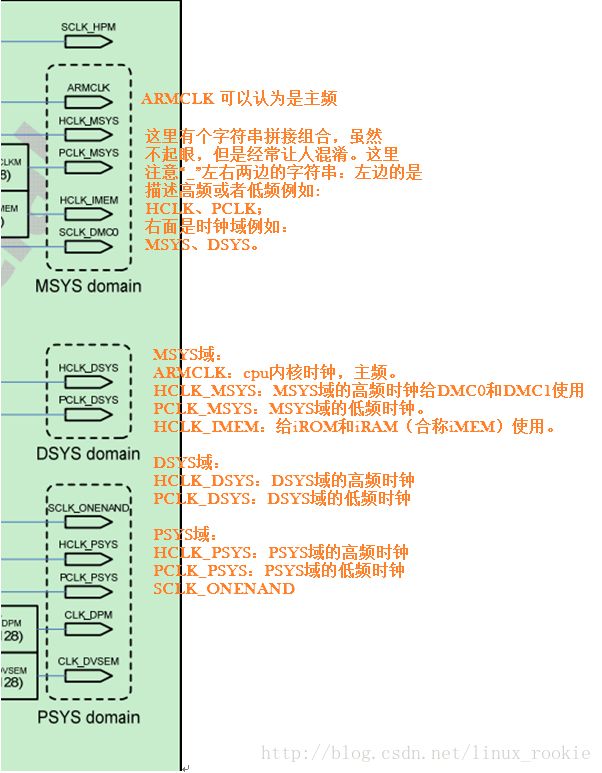

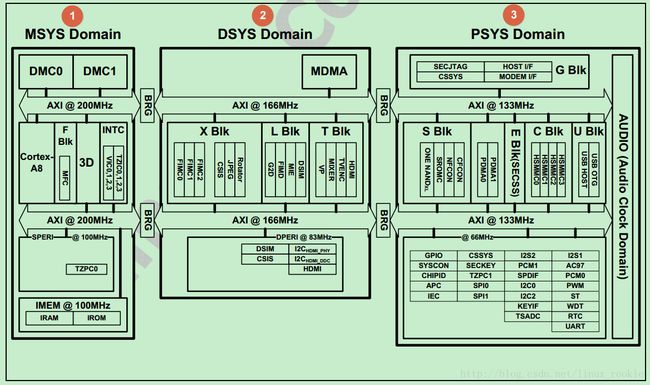

如上图,s5pv210(Cortex-A8) 的时钟与之前的arm9、arm11有所不同,分成了三个区域:

时钟区域:MSYS、DSYS、PSYS

偷个懒看看手册原来的解释:

S5PV210 consists of three clock domains, namely, main system (MSYS), display system (DSYS), and peripheral

system (PSYS), as shown in Figure 3-1.

• MSYS domain comprises Cortex A8 processor, DRAM memory controllers (DMC0 and DMC1), 3D, internal

SRAM (IRAM, and IROM), INTC, and configuration interface (SPERI). Cortex A8 supports only synchronous

mode, and therefore it must operate synchronously with 200MHz AXI buses.

• DSYS domain comprises display related modules, including FIMC, FIMD, JPEG, and multimedia IPs (all other

IPs mentioned in X, L, and T blocks), as shown in Figure 3-1.

• PSYS domain is used for security, I/O peripherals, and low power audio play.

• Each bus system operates at 200 MHz (maximum), 166 MHz, and 133 MHz, respectively. There are

asynchronous bus bridges (BRG) between two different domains.通过上述可知:

1、MSYS:这个时钟域主要都是需要告诉时钟的器件,例如DRAM 控制器(DMC0和DMC1)、IRAM&IROM等。

2、DSYS:都是和图像视频解码有关硬件时钟。

3、PSYS:低速设备,也是我们最关心且用的最多的片内外设,例如spi、iic、uart等等。

三、CLOCK DECLARATION

In ***typical*** S5PV210 applications,

• Cortex A8 and MSYS clock domain uses APLL (that is, ARMCLK, HCLK_MSYS, and PCLK_MSYS).

• DSYS and PSYS clock domain (that is, HCLK_DSYS, HCLK_PSYS, PCLK_DSYS, and PCLK_PSYS) and

other peripheral clocks (that is, audio IPs, SPI, and so on) use MPLL and EPLL.

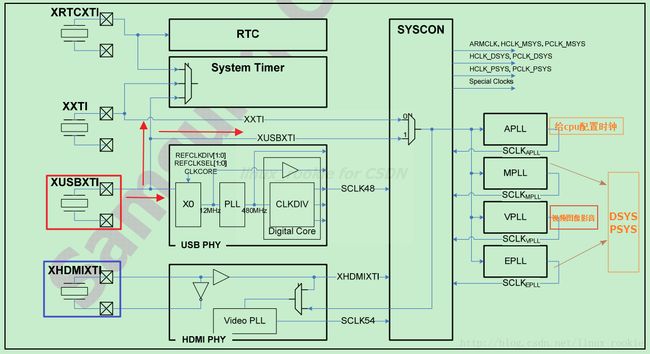

• Video clocks uses VPLL.手册的上述给出了一个典型的配置案例,或者是说默认配置。看下图:

从这张图中我们可以看到此cpu最大可以连接4个晶振为了经济我们可以只焊接红色区域框定的晶振,如果需要支持HDMI也要把蓝色框中框定的晶振焊接。我们可以看到红色框定的晶振它的去路最多,可以最大限度的支持系统的时钟。

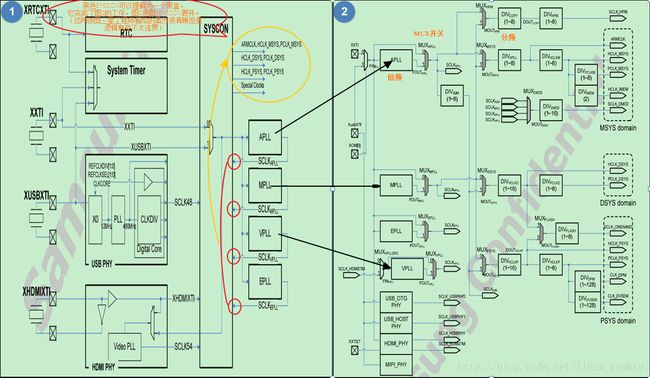

上图2是图1 SYSCON的一个展开,图2详细描述了倍频、mux开关、分频三部分的详细逻辑图,对于之后的寄存器配置起到了相当的引导作用。观图时注意图1的红色小圈中的反向箭头,其实对应图1到图2的黑色长箭头。

细心的朋友可能会发现,这两张逻辑图有点不太匹配,图2这么画主要依据是手册中的这样一段话:

• PLL

− APLL can drive MSYS domain and DSYS domain. It can generate up to 1 GHz, 49:51 duty ratio.

− MPLL can drive MSYS domain and DSYS domain. It supplies clock, up to 2 GHz and 40:60 duty ratio.

− EPLL is mainly used to generate audio clock.

− VPLL is mainly used to generate video system operating clock, 54 MHz.

− Typically, APLL drives MSYS domain and MPLL drives DSYS domain.时钟的逻辑匹配可以控制寄存器实现,但是总规是有个默认的配置,图2是根据默认的配置来画的导图。

同时还给出了默认配置值这个人觉得很重要,没有特殊需求就按照这样的参数去计算配置寄存器:

Values for the high-performance operation:

• freq(ARMCLK) = 1000 MHz

• freq(HCLK_MSYS) = 200 MHz

• freq(HCLK_IMEM) = 100 MHz

• freq(PCLK_MSYS) = 100 MHz

• freq(HCLK_DSYS) = 166 MHz

• freq(PCLK_DSYS) = 83 MHz

• freq(HCLK_PSYS) = 133 MHz

• freq(PCLK_PSYS) = 66 MHz

• freq(SCLK_ONENAND) = 133 MHz, 166 MHz