Verilog一个小程序:采用casez语句描述数据选择器

本程序包括功能模块和testbench。

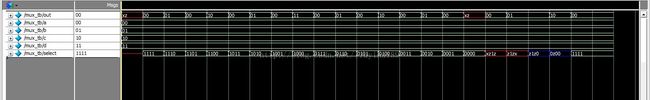

本程序的功能模块实现的是一个带优先级的数据选择器(低位优先级高)。

本程序说明的问题:

1、casez的敏感表达式的值中“?”代替的位表示不考虑;

2、casez会将激励信号z判断为与四值信号(0、1、x、z)都相等。

代码如下:

1、功能模块:

//mux.vmodule mux(out,a,b,c,d,select);

output[1:0] out;

input[1:0] a,b,c,d;

input[3:0] select;

reg[1:0] out;

always @(select or a or b or c or d)

begin

casez(select)

4'b???1:out=a;

4'b??1?:out=b;

4'b?1??:out[1:0]=c[1:0];

4'b1???:out[1:0]=d[1:0];//加不加[1:0]都行

default: out[1:0]=2'bxz;

endcase

end

endmodulemux_tb.v`timescale 10ns/1ns

module mux_tb;

wire[1:0] out;//out必须是wire型

reg[1:0] a,b,c,d;

reg[3:0] select;

mux mux(out,a,b,c,d,select);

initial

begin

a=0;b=1;c=2;d=3;

#5 select=4'b1111;//out=a,即0

#5 select=4'b1110;//out=b,即1

#5 select=4'b1101;//out=a,即0

#5 select=4'b1100;//out=c,即2

#5 select=4'b1011;//out=a,即0

#5 select=4'b1010;//out=b,即1

#5 select=4'b1001;//out=a,即0

#5 select=4'b1000;//out=d,即3

#5 select=4'b0111;//out=a,即0

#5 select=4'b0110;//out=b,即1

#5 select=4'b0101;//out=a,即0

#5 select=4'b0100;//out=c,即2

#5 select=4'b0011;//out=a,即0

#5 select=4'b0010;//out=b,即1

#5 select=4'b0001;//out=a,即0

#5 select=4'b0000;//out=xz

#5 select=4'bxz1z;//out=a,即0

#5 select=4'bz1zx;//out=b,即1

#5 select=4'bz1z0;//out=b,即1

#5 select=4'b0z00;//out=c,即2

#5 select=4'b1111;//out=a,即0

#10//$display和$finish必须放在begin end块里面

$display("please remember:h-h love m-e!");

$finish;

end

endmodule命令窗口输出为:

run

# please remember?h-h love m-e!

# ** Note: $finish : ./mux_tb.v(39)

# Time: 1150 ns Iteration: 0 Instance: /mux_tb

# 1

# Break in Module mux_tb at ./mux_tb.v line 39