- I.MX6 Android 平台CAN总线调试(包含测试C语言代码)

Donald Linux

Android

I.MX6Android平台CAN总线调试(包含测试C语言代码)前言:这几天需要调试NXPAndroid平台CAN总线,以前到工作中都没有接触过can总线,折腾了几天,终于通信成功。至于can总线的原理我就不细说了,网上很多,原理很复杂,也比较难懂,我们主要还是学习如何使用就可以了。这里就记录以下在android平台下如何使用can进行通信。一、外围电路CAN总线收发驱动电路。二、在imx6q的的

- Linux学习笔记3-GPIO(1)

raulcy

linux学习笔记arm

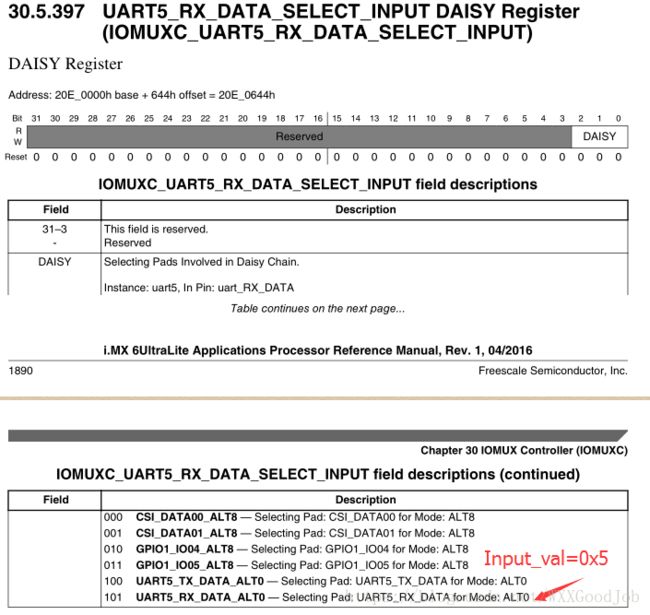

学习单片机时最开始也是从GPIO开始的,Linux的主芯片I.MX6UL有124个GPIO,当然很多是复用的,与之对比,STM32F407系列的单片机GPIO口是112个。回顾之前单片机的学习,大部分的GPIO功能是通过HAL库函数调用的,例如HAL_GPIO_WritePin()和HAL_GPIO_TogglePin()都是很方便的操作GPIO的库函数,编程者无需关心寄存器如何设置。那I.MX6

- 【LINUX】i.MX6学习笔记(4) IIC驱动 smec98sp

taotao830

LINUXIMX6嵌入式

1.引言最近一个linux项目需要用到smec98sp来做一个加密鉴权的功能。鉴权方案就不写了,这里主要记录一下IIC驱动smec98sp的过程,顺便记录下linux下IIC设备的框架。2.IIC简介IIC总线介绍见上一篇【硬件】IIC总线。在此不再赘述。3.smec98sp简介smec98sp是中巨伟业的一款加密芯片,用于进行系统的一些加密校验,可以从官网下载到SDK开发包,从淘宝购买对应的下载

- 基于freescale i.Mx6(ARM)的阿里云oss调试记录

weixin_33939843

交叉编译阿里OSS调试记录1.1开通oss服务具体参考以下链接:https://help.aliyun.com/document_detail/31884.html?spm=a2c4g.11186623.6.558.n2g1UA1.2SDK安装在ubuntu下安装,安装步骤如下:安装CMake执行以下命令安装CMake。sudoapt-getinstallcmake安装第三方库执行以下命令安装第三

- 移植TensorFlow Lite到ARM板i.MX6上

lucca_x

上一篇文章说到移植到LC1860C板上失败后,我又换了一块库更全更新的板子,继续大业。运行label_image./label_image-v1-m./mobilenet_v1_1.0_224.tflite-i./grace_hopper.jpg-l./imagenet_slim_labels.txtalloc失败遇到的第一个问题是alloc失败。...83:MobilenetV1/Mobilen

- Tensorflow Lite tflite模型的导入 - ARM板i.MX6

lucca_x

上一篇文章中讲了tflite模型的建立和Python端的导入,现在开始在ARM板上的导入。为了不再重新生成输入数据,我将PC上python生成的数据保存到txt文件。所以稍微改了下上次那个代码:importnumpyasnpimporttimeimportmathimporttensorflowastfSIZE=1000X=np.random.rand(SIZE,1)X=X*(math.pi/2.

- open62541交叉编译

姚家湾

ubuntulinuxIEC61499OPCUA

好久没有做嵌入式ArmLinux的开发了。最近要将open62541的应用程序移植到i.mx6u嵌入式控制器。网络上讲解i.mx6交叉编译的文章太多了。但是都过于复杂,大多数使用虚拟机实现。其实在ubuntuOS下,开发ARM嵌入式应用软件相对是相当简单的。这里记录了在ubuntuLinux下,交叉编译i.mx应用软件的过程。安装交叉编译工具及其基本库目标设备为两种ARMNXPi.mx6基于Arm

- 从单片机开发转向Linux开发系列博客二:运行Hello World

TopSemic嵌入式

2.Linux处理器

1.引言前天写的文章《Linux学习系列一:开发环境搭建》,放到阿莫论坛里没想到第二天就变成火帖了,看来还是有很多人对这个主题挺感兴趣的。借着大家的鼓舞,趁热打铁,今天再写一篇。今天给大家介绍的是在一个嵌入式Linux板子上运行HelloWorld,入门学习的经典操作。依稀记得两年前,我第一次在飞思卡尔(现NXP)I.MX6上运行出HelloWorld的那种喜悦之情。希望这篇文章也能对你有帮助。2

- NXP i.MX6读取MPU内部温度命令

beetleinv

软件设计linuxubuntu

基于Linux系统个和imx6平台,读取MPU内部温度的命令。root@imx6ul7d:~#cat/sys/devices/virtual/thermal/thermal_zone0/temp34341root@imx6ul7d:~#cat/sys/class/thermal/thermal_zone0/trip_point_0_typepassiveroot@imx6ul7d:~#cat/sy

- nxp i.mx6系列处理器修改和查看eFuse的方法

beetleinv

硬件设计软件设计linux

博主在发此博文前,已经在i.mx6ul和i.mx6ull处理器验证过了。在uboot阶段进行查看或修改eFuse,语法如下。=>fuseread[]//从影子寄存器中读取eFuse的值=>fusesense[]ReadstheeFusevaluedirectlyfromthefusebox.=>fuseprog[-y]//写eFuse值到fusebox,此操作是不可逆的,错误的操作可能会损坏芯片=

- 第三代NXP i.MX6ULL核心板硬件设计指南

飞凌嵌入式

i.MX6ULLlinux运维服务器

NXPi.MX6ULL扩展了i.MX6系列,它是一个高性能、超高效、低成本处理器子系列,采用先进的ARMCortex-A7内核,运行速度高达800MHz。i.MX6ULL应用处理器包括一个集成的电源管理模块,降低了外接电源的复杂性,并简化了上电时序,目标应用有:汽车远程信息处理、IoT网关、人机界面、家庭能源管理系统、智能能源信息集中器、智能工业控制系统、电子POS设备、便携医疗设备、打印机和2D

- 基于linux5.15.5的IMX 参考手册 --- 2

chocolate2018

linux驱动NXP芯片linux

基于linux5.15.5的IMX参考手册—22.3引导映像2.3.1介绍对于i.MX6和i.MX7,引导映像只使用U-Boot引导加载程序。对于i.MX8系列中的SoC,引导映像更加复杂,包括U-Boot以及成功引导所需的各种固件。本章介绍i.MX8系列引导加载程序的附加组件。对于i.MX7ULP,引导分区需要ArmCortexM-4SDK闪存,因为ArmCortexM-4引导U-Boot引导加

- ARM与Qt及openCV的思路总结

wangzi199822

嵌入式ARMopenCVQt

本文经过拜读师兄一路调bug的实验过程,深知入门不易,在这接着总结一些嵌入式配置opencv等的大致思路。同时对摄像头读取操作和QT中opencv处理作详细的记录。附上其文章,建议常读:i.MX6开发板嵌入式linux开发上面笔记记录一些嵌入式内核配置opencv的过程,同时简述opencv+qt在嵌入式内核中运行的配置;一、思路1.ARM+Qte的配置本次实验的ARM板子是IMX6开发板,烧写u

- 在arm,i.mx6上调试使用EC20 4G模块上网

YANGXUSHI520

笔记嵌入式arm物联网

1,添加USB设备信息1.1,修改drivers/usb/serial/option.c(1)添加PID和VID#defineQUECTEL_VENDOR_ID0X2C7C#defineQUECTEL_PRODUCT_EC200X0125(2)将ID宏信息添加到option_ids数组中staticconststructusb_device_idoption_ids[]={{USB_DEVICE(

- 嵌入式人工智能教学科研平台

9#月芳

机器学习

ZN-AI-BC01型嵌入式人工智能教学科研平台一、产品特点VS-AI-BC01型嵌入式人工智能教学科研平台采用目前市场上*主流的i.MX6工业级处理器,具有图像硬件加速器与原生千兆以太网;基于Ubuntu18.04系统,支持OpenCV3.2.0,Python2.7/3.6.7,Qt5.9.5,包含OpenCV、Python实验体系,拥有图像识别、语音识别案例,可与百度人工智能平台、天工平台对接

- linux共享文件夹_嵌入式Linux系列第2篇:运行Hello World

weixin_39610774

linux共享文件夹linux如何复制粘贴linux怎么复制粘贴虚拟机qt文件运行跑linux的单片机

1.引言今天给大家介绍的是在一个嵌入式Linux板子上运行HelloWorld,软硬件入门学习的经典操作。依稀记得两年前,我第一次在飞思卡尔(现NXP)I.MX6上运行出HelloWorld的那种喜悦之情。希望这篇文章能对你有所帮助。2.硬件平台选择能够运行Linux系统的嵌入式硬件平台,我了解的有这么几个,一是三星的2440系列,著名的韦东山老师的Linux视频教程就是用的这个平台。二是TI的A

- opencv 手册_I.MX6 Linux Yocto与OpenCV

weixin_39601641

opencv手册opencv手册opencv镜像

配件环境:主机:Ubuntu16.04LTS64bit开发板:NXPimx6qsabresdBspversion:fsl-yocto-L4.1.15_2.0.0-gaYoctoProjectversion:2.1Yocto配置:主机包安装:打开Terminal依次输入以下三条语句,如果速度很慢,可以更换国内下载源。$sudoapt-getinstallgawkwgetgit-corediffsta

- i.MX8M Mini与i.MX6的一些比较分析

vickycheung3

嵌入式产品i.MX8MMinicortex-A53cortex-M4物联网开发板

在NXPi.mx8系列发布前,imx6系列一直是nxpimx系列的主力军,应用于工业物联、数据采集、车载产品等领域。在万物互联时代,对产品有了进一步的要求,更多的设备,更快的处理速度、更低的能耗,推动高性能、低能耗处理器不断更新。启扬智能基于NXPi.MX8MMini推出IAC-IMX8MM-CM,是启扬经典产品IAC-IMX6-CM的升级之作。IAC-IMX6-CMVSIAC-IMX8MM-CM

- 【转载】NXP i.MX8系列处理器介绍

vickycheung3

分享技术分享NXPi.MX8cortex-A72Cortex-A53

NXPi.MX系列应用处理器是基于32和64位ARM技术,提供多核解决方案,适用于多媒体和显示应用,具有高性能和低功耗、可扩展、安全可靠等特点。发展经历了早期的i.MX28系列,到大获成功的i.MX6系列,再到更高性能的i.MX7和i.MX8系列,此外还有跨界MCUi.MXRT系列。今天主要来介绍一下最新的i.MX8系列。I.MX8系列应用处理器是恩智浦针对高端应用市场推出的旗舰型产品,根据不同配

- 嵌入式学习:裸机开发_L5_BSP工程管理LED实验

fzx2020

嵌入式

裸机开发_L5_BSP工程管理LED实验0.本节目标1.目录结构2.硬件层电路2.1正点原子i.MX6ULLALPHAV2.2开发板2.2飞凌i.MX6UL-C开发板3.软件编写0.本节目标Makefile的编写:函数使用BSP分门别类1.目录结构2.硬件层电路2.1正点原子i.MX6ULLALPHAV2.2开发板查看底板原理图可知:功能管脚芯片引脚LED0GPIO1_IO032.2飞凌i.MX6

- RTL8723BU在I.MX6 DQ平台上的移植

jinron10

WIFIBT汽车电子Android技术开发

摘要:在移植时请注意,因为Realtek发布的移植代码和文档不是针对Freescale平台的,所以首先看一下,目前使用的平台是否已经支持BT和WIFI功能(可能不是我们要移植的模块)。一般情况下,原厂发布BSP都支持BT和WIFI功能,也就是说AndroidOS部分已经完整的包含BT和WIFI功能,只要适配驱动和HAL即可。我们针对RTL8723BU的BT和WIFI的移植就是基于这个思路去移植的。

- 迅为开发板-i.MX6Q开发板飞思卡尔imx6开发板专业推荐

chengzhou7664

i.MX6系列推出了基于ARM?CortexTM-A9架构的包括单核、双核和四核在内的高扩展性多核系列应用处理器平台,促进了消费电子、工业和汽车车载娱乐系统等新一代应用的发展。通过与ARMCortex-A9架构的高效处理能力、前沿性的2D与3D图形以及高清晰视频功能实现一流水平的集成,i.MX6系列可以提供令人瞩目的多媒体性能,以支持超越现有界限的下一代用户体验。使i.MX单核、双核和四核产品获得

- 如何使用makefile编译不同平台的目标文件(makefile的参数传递)

leon1741

玩转linux

最近在研究一个嵌入式开发项目,在编写实际的项目代码时,需要临时写一些测试代码对部分功能进行预测试。编写的这些代码,有时候需要在PC机(x86)的平台上运行,有时候则需要在A嵌入式平台(arm端)i.mx6的平台上运行,而还有时候则需要在B嵌入式平台(arm端)mini2440的平台上运行,需要能随时进行切换,编译出对应平台所需要的可执行文件。为了解决这个问题,最土的办法自然就是写三份makefil

- i.MX6 Yocto工程简介与分析

致守

Linux

i.MX6Yocto工程简介与分析按照NXP官方网站的说法,i.MX6的源码都发布在YoctoProjectFreescalei.MX6release工程里了。TheFSLYoctoProjectCommunityBSP(freescale.github.io)是一个社区驱动的在YoctoProject里提供相关i.MX6单板支持和维BoardSupportPackagemetalayer社区。使

- I.MX6 按键开关机 PMIC 检测

weixin_33810302

/**************************************************************************I.MX6按键开关机PMIC检测*说明:*最近一直在被i.MX6的开机、关机流程控制,其内部是如何检测到1秒按钮,*2秒按钮,4秒按钮的,这其中的工作机制是如何实现,由于发现这部分工作并*不是在PMIC上实现了,现在终于在数据手册上找到这部分相关介绍

- Yocto i.MX6 (TQIMX6) (01) : 3.14.28内核的适配

dxmcu

飞思卡尔I.MX6Q

FreesacleYocto的环境配置与编译到Freescale下载imx6LinuxSourceCode,解压里面的fsl-yocto命名的压缩包得到Yoctosetup手册:Freescale_Yocto_Project_User's_Guide.pdf然后按照里面的步骤操作即可编译出一个完整的distribution,当然很可能会因为网络或者一些Package早已不存在,或者因为大家都知道的

- 使用Buildroot为Nxp i.mx6ul制作文件系统

WindLOR

i.mx6ulARM

随着神Us3c2440,6410的停产,NXP针对中国市场推出低成本方案i.mx6ul,可用于商业级和工业级应用,10年超长供货周期,市场很有潜力。官方只支持Yocto,但个人感觉Yocto太多庞大且太复杂,而工业市场业务并不是特别负责,需要用到的软件包有限,且在特定的一个范围。工业市场对稳定性要求较高,并不需很大的灵活度。本文将介绍使用Buildroot为i.mx6制作文件系统,相对来说Buil

- I.MX6 PCB设计的一点心得

metersun

从最初的protel99se双面板,四层板,到使用PADS设计的8层板,到当前主要使用allegro来进行大部分的4层,6层,8层板设计,做PCB设计和布板断断续续已近10年了。由于工作需要,我不能把全部精力放在硬件设计上,不得不抽出大量的时间来做软件和系统设计(这么多年也一直关注linux的发展)。人的时间和精力是非常有限的。所以,在软硬件方面,我自愧都不能走的太远。2016年中,在专注做较高端

- Linux Kernl添加spidev的设备节点

www.wowothink.com

LinuxDeviceDriver

一、spidev介绍如果在内核中配置spidev,会在/dev目录下产生设备节点,通过此节点可以操作挂载在该SPI总线上的设备。用户空间通过该节点可以访问内核空间。二、配置spidev设备步骤在i.MX6,Kernel4.1.15上配置spidev的支持。1、配置dts支持spi根据spi的连接原理图配置对应的imx6qp-xxx.dts,如:&ecspi1{compatible="fsl,imx

- 飞思卡尔i.mx6交叉编译工具链BUG

liuhuahan

Linux系统开发C语言

最近在用飞思卡尔的i.mx6平台做一个项目,编写完代码在i.mx6上测试的时候发现有一个函数的返回值判断一直不正确,我一个函数的返回值类型为"char"错误返回值是‘-2’,并且用其返回值与‘0’值比大小来进入不同处理分支,但是测试的时候发现,程序始终无法进入错误分支,最后经反复测试才找到问题,因为返回‘-2’的时候系统把他当做254来处理了。后来我在char前边加一个signed修饰,就能正确返

- 如何用ruby来写hadoop的mapreduce并生成jar包

wudixiaotie

mapreduce

ruby来写hadoop的mapreduce,我用的方法是rubydoop。怎么配置环境呢:

1.安装rvm:

不说了 网上有

2.安装ruby:

由于我以前是做ruby的,所以习惯性的先安装了ruby,起码调试起来比jruby快多了。

3.安装jruby:

rvm install jruby然后等待安

- java编程思想 -- 访问控制权限

百合不是茶

java访问控制权限单例模式

访问权限是java中一个比较中要的知识点,它规定者什么方法可以访问,什么不可以访问

一:包访问权限;

自定义包:

package com.wj.control;

//包

public class Demo {

//定义一个无参的方法

public void DemoPackage(){

System.out.println("调用

- [生物与医学]请审慎食用小龙虾

comsci

生物

现在的餐馆里面出售的小龙虾,有一些是在野外捕捉的,这些小龙虾身体里面可能带有某些病毒和细菌,人食用以后可能会导致一些疾病,严重的甚至会死亡.....

所以,参加聚餐的时候,最好不要点小龙虾...就吃养殖的猪肉,牛肉,羊肉和鱼,等动物蛋白质

- org.apache.jasper.JasperException: Unable to compile class for JSP:

商人shang

maven2.2jdk1.8

环境: jdk1.8 maven tomcat7-maven-plugin 2.0

原因: tomcat7-maven-plugin 2.0 不知吃 jdk 1.8,换成 tomcat7-maven-plugin 2.2就行,即

<plugin>

- 你的垃圾你处理掉了吗?GC

oloz

GC

前序:本人菜鸟,此文研究学习来自网络,各位牛牛多指教

1.垃圾收集算法的核心思想

Java语言建立了垃圾收集机制,用以跟踪正在使用的对象和发现并回收不再使用(引用)的对象。该机制可以有效防范动态内存分配中可能发生的两个危险:因内存垃圾过多而引发的内存耗尽,以及不恰当的内存释放所造成的内存非法引用。

垃圾收集算法的核心思想是:对虚拟机可用内存空间,即堆空间中的对象进行识别

- shiro 和 SESSSION

杨白白

shiro

shiro 在web项目里默认使用的是web容器提供的session,也就是说shiro使用的session是web容器产生的,并不是自己产生的,在用于非web环境时可用其他来源代替。在web工程启动的时候它就和容器绑定在了一起,这是通过web.xml里面的shiroFilter实现的。通过session.getSession()方法会在浏览器cokkice产生JESSIONID,当关闭浏览器,此

- 移动互联网终端 淘宝客如何实现盈利

小桔子

移動客戶端淘客淘寶App

2012年淘宝联盟平台为站长和淘宝客带来的分成收入突破30亿元,同比增长100%。而来自移动端的分成达1亿元,其中美丽说、蘑菇街、果库、口袋购物等App运营商分成近5000万元。 可以看出,虽然目前阶段PC端对于淘客而言仍旧是盈利的大头,但移动端已经呈现出爆发之势。而且这个势头将随着智能终端(手机,平板)的加速普及而更加迅猛

- wordpress小工具制作

aichenglong

wordpress小工具

wordpress 使用侧边栏的小工具,很方便调整页面结构

小工具的制作过程

1 在自己的主题文件中新建一个文件夹(如widget),在文件夹中创建一个php(AWP_posts-category.php)

小工具是一个类,想侧边栏一样,还得使用代码注册,他才可以再后台使用,基本的代码一层不变

<?php

class AWP_Post_Category extends WP_Wi

- JS微信分享

AILIKES

js

// 所有功能必须包含在 WeixinApi.ready 中进行

WeixinApi.ready(function(Api) {

// 微信分享的数据

var wxData = {

&nb

- 封装探讨

百合不是茶

JAVA面向对象 封装

//封装 属性 方法 将某些东西包装在一起,通过创建对象或使用静态的方法来调用,称为封装;封装其实就是有选择性地公开或隐藏某些信息,它解决了数据的安全性问题,增加代码的可读性和可维护性

在 Aname类中申明三个属性,将其封装在一个类中:通过对象来调用

例如 1:

//属性 将其设为私有

姓名 name 可以公开

- jquery radio/checkbox change事件不能触发的问题

bijian1013

JavaScriptjquery

我想让radio来控制当前我选择的是机动车还是特种车,如下所示:

<html>

<head>

<script src="http://ajax.googleapis.com/ajax/libs/jquery/1.7.1/jquery.min.js" type="text/javascript"><

- AngularJS中安全性措施

bijian1013

JavaScriptAngularJS安全性XSRFJSON漏洞

在使用web应用中,安全性是应该首要考虑的一个问题。AngularJS提供了一些辅助机制,用来防护来自两个常见攻击方向的网络攻击。

一.JSON漏洞

当使用一个GET请求获取JSON数组信息的时候(尤其是当这一信息非常敏感,

- [Maven学习笔记九]Maven发布web项目

bit1129

maven

基于Maven的web项目的标准项目结构

user-project

user-core

user-service

user-web

src

- 【Hive七】Hive用户自定义聚合函数(UDAF)

bit1129

hive

用户自定义聚合函数,用户提供的多个入参通过聚合计算(求和、求最大值、求最小值)得到一个聚合计算结果的函数。

问题:UDF也可以提供输入多个参数然后输出一个结果的运算,比如加法运算add(3,5),add这个UDF需要实现UDF的evaluate方法,那么UDF和UDAF的实质分别究竟是什么?

Double evaluate(Double a, Double b)

- 通过 nginx-lua 给 Nginx 增加 OAuth 支持

ronin47

前言:我们使用Nginx的Lua中间件建立了OAuth2认证和授权层。如果你也有此打算,阅读下面的文档,实现自动化并获得收益。SeatGeek 在过去几年中取得了发展,我们已经积累了不少针对各种任务的不同管理接口。我们通常为新的展示需求创建新模块,比如我们自己的博客、图表等。我们还定期开发内部工具来处理诸如部署、可视化操作及事件处理等事务。在处理这些事务中,我们使用了几个不同的接口来认证:

&n

- 利用tomcat-redis-session-manager做session同步时自定义类对象属性保存不上的解决方法

bsr1983

session

在利用tomcat-redis-session-manager做session同步时,遇到了在session保存一个自定义对象时,修改该对象中的某个属性,session未进行序列化,属性没有被存储到redis中。 在 tomcat-redis-session-manager的github上有如下说明: Session Change Tracking

As noted in the &qu

- 《代码大全》表驱动法-Table Driven Approach-1

bylijinnan

java算法

关于Table Driven Approach的一篇非常好的文章:

http://www.codeproject.com/Articles/42732/Table-driven-Approach

package com.ljn.base;

import java.util.Random;

public class TableDriven {

public

- Sybase封锁原理

chicony

Sybase

昨天在操作Sybase IQ12.7时意外操作造成了数据库表锁定,不能删除被锁定表数据也不能往其中写入数据。由于着急往该表抽入数据,因此立马着手解决该表的解锁问题。 无奈此前没有接触过Sybase IQ12.7这套数据库产品,加之当时已属于下班时间无法求助于支持人员支持,因此只有借助搜索引擎强大的

- java异常处理机制

CrazyMizzz

java

java异常关键字有以下几个,分别为 try catch final throw throws

他们的定义分别为

try: Opening exception-handling statement.

catch: Captures the exception.

finally: Runs its code before terminating

- hive 数据插入DML语法汇总

daizj

hiveDML数据插入

Hive的数据插入DML语法汇总1、Loading files into tables语法:1) LOAD DATA [LOCAL] INPATH 'filepath' [OVERWRITE] INTO TABLE tablename [PARTITION (partcol1=val1, partcol2=val2 ...)]解释:1)、上面命令执行环境为hive客户端环境下: hive>l

- 工厂设计模式

dcj3sjt126com

设计模式

使用设计模式是促进最佳实践和良好设计的好办法。设计模式可以提供针对常见的编程问题的灵活的解决方案。 工厂模式

工厂模式(Factory)允许你在代码执行时实例化对象。它之所以被称为工厂模式是因为它负责“生产”对象。工厂方法的参数是你要生成的对象对应的类名称。

Example #1 调用工厂方法(带参数)

<?phpclass Example{

- mysql字符串查找函数

dcj3sjt126com

mysql

FIND_IN_SET(str,strlist)

假如字符串str 在由N 子链组成的字符串列表strlist 中,则返回值的范围在1到 N 之间。一个字符串列表就是一个由一些被‘,’符号分开的自链组成的字符串。如果第一个参数是一个常数字符串,而第二个是type SET列,则 FIND_IN_SET() 函数被优化,使用比特计算。如果str不在strlist 或st

- jvm内存管理

easterfly

jvm

一、JVM堆内存的划分

分为年轻代和年老代。年轻代又分为三部分:一个eden,两个survivor。

工作过程是这样的:e区空间满了后,执行minor gc,存活下来的对象放入s0, 对s0仍会进行minor gc,存活下来的的对象放入s1中,对s1同样执行minor gc,依旧存活的对象就放入年老代中;

年老代满了之后会执行major gc,这个是stop the word模式,执行

- CentOS-6.3安装配置JDK-8

gengzg

centos

JAVA_HOME=/usr/java/jdk1.8.0_45

JRE_HOME=/usr/java/jdk1.8.0_45/jre

PATH=$PATH:$JAVA_HOME/bin:$JRE_HOME/bin

CLASSPATH=.:$JAVA_HOME/lib/dt.jar:$JAVA_HOME/lib/tools.jar:$JRE_HOME/lib

export JAVA_HOME

- 【转】关于web路径的获取方法

huangyc1210

Web路径

假定你的web application 名称为news,你在浏览器中输入请求路径: http://localhost:8080/news/main/list.jsp 则执行下面向行代码后打印出如下结果: 1、 System.out.println(request.getContextPath()); //可返回站点的根路径。也就是项

- php里获取第一个中文首字母并排序

远去的渡口

数据结构PHP

很久没来更新博客了,还是觉得工作需要多总结的好。今天来更新一个自己认为比较有成就的问题吧。 最近在做储值结算,需求里结算首页需要按门店的首字母A-Z排序。我的数据结构原本是这样的:

Array

(

[0] => Array

(

[sid] => 2885842

[recetcstoredpay] =&g

- java内部类

hm4123660

java内部类匿名内部类成员内部类方法内部类

在Java中,可以将一个类定义在另一个类里面或者一个方法里面,这样的类称为内部类。内部类仍然是一个独立的类,在编译之后内部类会被编译成独立的.class文件,但是前面冠以外部类的类名和$符号。内部类可以间接解决多继承问题,可以使用内部类继承一个类,外部类继承一个类,实现多继承。

&nb

- Caused by: java.lang.IncompatibleClassChangeError: class org.hibernate.cfg.Exten

zhb8015

maven pom.xml关于hibernate的配置和异常信息如下,查了好多资料,问题还是没有解决。只知道是包冲突,就是不知道是哪个包....遇到这个问题的分享下是怎么解决的。。

maven pom:

<dependency>

<groupId>org.hibernate</groupId>

<ar

- Spark 性能相关参数配置详解-任务调度篇

Stark_Summer

sparkcachecpu任务调度yarn

随着Spark的逐渐成熟完善, 越来越多的可配置参数被添加到Spark中来, 本文试图通过阐述这其中部分参数的工作原理和配置思路, 和大家一起探讨一下如何根据实际场合对Spark进行配置优化。

由于篇幅较长,所以在这里分篇组织,如果要看最新完整的网页版内容,可以戳这里:http://spark-config.readthedocs.org/,主要是便

- css3滤镜

wangkeheng

htmlcss

经常看到一些网站的底部有一些灰色的图标,鼠标移入的时候会变亮,开始以为是js操作src或者bg呢,搜索了一下,发现了一个更好的方法:通过css3的滤镜方法。

html代码:

<a href='' class='icon'><img src='utv.jpg' /></a>

css代码:

.icon{-webkit-filter: graysc