PL读写DDR3 实现PS和PL间的数据交互 时序波形图

本文是PL读写DDR3 实现PS和PL间的数据交互 以及 PL读写DDR3 实现PS和PL间的数据交互 代码分析的继续

虽然在代码分析一文中分析了代码,但还是时序波形图比较直观,我这是用 Vivado的集成逻辑分析仪ILA 在有sdk 下的应用入门 介绍的方法采集的。

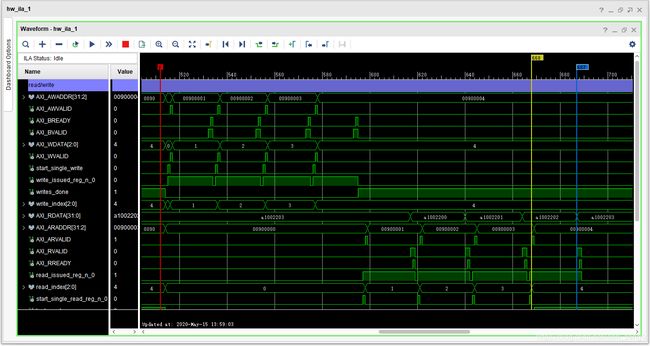

波形如下:

上面波形图的信号名依次是:

system_i/AzIP_AXI_Master_0_M00_AXI_AWADDR

system_i/AzIP_AXI_Master_0_M00_AXI_AWVALID

system_i/AzIP_AXI_Master_0_M00_AXI_BREADY

system_i/AzIP_AXI_Master_0_M00_AXI_BVALID

system_i/AzIP_AXI_Master_0_M00_AXI_WDATA

system_i/AzIP_AXI_Master_0_M00_AXI_WVALID

system_i/AzIP_AXI_Master_0/inst/AzIP_AXI_Master_v1_0_M00_AXI_inst/start_single_write_reg_n_0

system_i/AzIP_AXI_Master_0/inst/AzIP_AXI_Master_v1_0_M00_AXI_inst/write_issued_reg_n_0

system_i/AzIP_AXI_Master_0/inst/AzIP_AXI_Master_v1_0_M00_AXI_inst/writes_done

system_i/AzIP_AXI_Master_0/inst/AzIP_AXI_Master_v1_0_M00_AXI_inst/write_index

system_i/AzIP_AXI_Master_0/inst/AzIP_AXI_Master_v1_0_M00_AXI_inst/last_write(这个信号遗漏了)

system_i/AzIP_AXI_Master_0_M00_AXI_RDATA

system_i/AzIP_AXI_Master_0_M00_AXI_ARADDR

system_i/AzIP_AXI_Master_0_M00_AXI_ARVALID

system_i/AzIP_AXI_Master_0_M00_AXI_RVALID

system_i/AzIP_AXI_Master_0_M00_AXI_RREADY

system_i/AzIP_AXI_Master_0/inst/AzIP_AXI_Master_v1_0_M00_AXI_inst/read_issued_reg_n_0

system_i/AzIP_AXI_Master_0/inst/AzIP_AXI_Master_v1_0_M00_AXI_inst/read_index

system_i/AzIP_AXI_Master_0/inst/AzIP_AXI_Master_v1_0_M00_AXI_inst/start_single_read0

system_i/AzIP_AXI_Master_0/inst/AzIP_AXI_Master_v1_0_M00_AXI_inst/last_read

system_i/AzIP_AXI_Master_0_m00_axi_txn_done (没显示)

system_i/AzIP_AXI_Master_0_m00_axi_error (没显示)

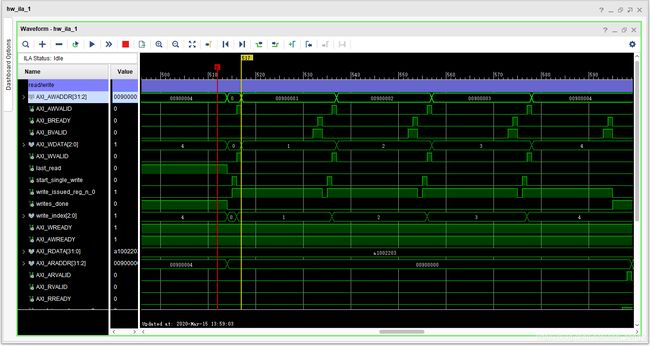

下面是单一的write

由于ip优化的缘故吧,AXI_WDATA[2:0] 只有这2位变化,0,1,2,3,4

AXI_AWADDR[31:2] ,分别是00900000-4,而0,1这2位一直为0

现在从信号分析流程:

start_single_write 开始,只是一个单脉冲,同时write_issue为高指示一个write 流程,

start_single_write 单脉冲的时候,=>AXI_AWVALID,AXI_WVALID,都变高,也是一个高脉冲。

同时数据AXI_WDATA和地址AXI_AWADDR,write_index都在此时变化。(这是下一周期的地址,不是本次的)

等待从设备的AXI_BVALID,AXI_BVALID==1,则立马给一个AXI_BREADY上脉冲。

AXI_BREADY,AXI_BVALID都为1,写过程完成, write_issue<=0。

如果是最后一个写last_write==1, write_done<=1。

last_write 的判断为((write_index == C_M_TRANSACTIONS_NUM) && M_AXI_AWREADY),这就是说在AWREADY为1时,上图没有这个信号,但最后一个图里有。

代码中

设置写保护级别:assign M_AXI_AWPROT = 3’b000;

写使能:assign M_AXI_WSTRB = 4’b1111;

这2个信号没有出现在图中,因为是固定的。

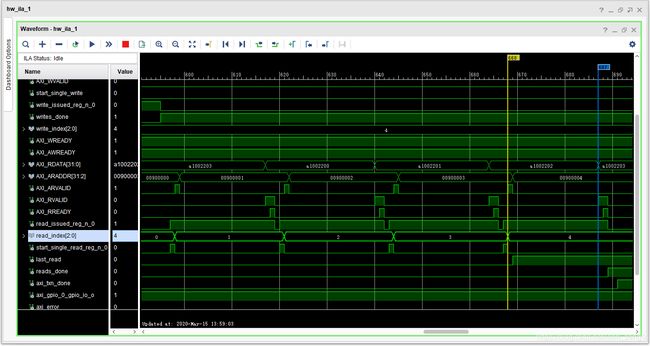

单一的read流程

AXI_ARADDR也一样,[31:2] ,分别是00900000-4,0,而1这2位一直为0

读的过程也是start_single_read 开始:

start_single_read 一个周期高脉冲,同时read_issue 为1,指示整个read过程。

start_single_read脉冲时,M00_AXI_ARVALID<=1 ,read_index++;

AXI_ARVALID==1时,AXI_ARADDR地址更改好。(这是下一周期的地址,不是本次的)

等待从设备的AXI_RVALID,AXI_RVALID==1时,给个AXI_RREADY<=1

AXI_RVALID,AXI_RREADY都为1时,read流程结束,read_issue<=0

这个时候(M_AXI_RVALID && axi_rready)也是读取数据的时候,这个程序里只是比较数据,也算读取。

如果是最后一个写last_read==1, read_done<=1。

last_read 的判断为((read_index == C_M_TRANSACTIONS_NUM) && M_AXI_ARREADY),这就是说在ARREADY为1时。

最开始的波形图有last_write,但少其他的次要信号

开始对这个波形图的理解有点偏差。

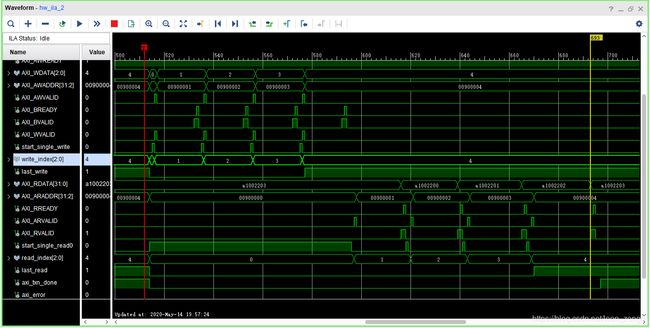

我们读写的ddr 到底是哪4个呢?

我用sdk 验证是0x2400_0000, -0x2400_0010,那么怎么理解上面的波形图呢?

sdk 代码是 :

printf("E=>PL ddr=%x, %x %x %x %x\n",Xil_In32(MY_DDR),Xil_In32(MY_DDR+4),Xil_In32(MY_DDR+8),Xil_In32(MY_DDR+12),Xil_In32(MY_DDR+16));

结果是:

E=>PL ddr=a1002200,a1002201, a1002202,a1002203, 11755e78

最后一次读取流程如下:

1: AXI_ARADDR 是 0x2400_000c (900_0003)

2: start_single_read <=1, read_issued<=1;

3:M00_AXI_ARVALID<=1 ,read_index++; start_single_read <=0

4:AXI_ARADDR <=0x2400_0010 这是下一读周期的地址,不是本次的地址

5:等待 AXI_RVALID==1

6: AXI_RREADY<=1 ,read_issued<=0;

介绍到此,希望对你有用。