XILINX SGMII千兆以太网 (2)

参考PG047

The LogiCORE™ IP 1G/2.5G Ethernet PCS/PMA or Serial Gigabit Media Independent Interface (SGMII) core provides a flexible solution for connection to an Ethernet Media Access Controller (MAC) or other custom logic.

It supports two standards: the 1000BASE-X and 2500BASE-X Physical Coding Sublayer (PCS) and Physical Medium Attachment (PMA) operation, as defined in the IEEE 802.3-2008 standard and the Gigabit Media Independent Interface (GMII) to Serial-GMII (SGMII) bridge or SGMII to GMII bridge, as defined in the Serial-GMII Specification V1.7 (CISCO SYSTEMS,

ENG-46158) [Ref 1].

Dynamic switching between 1000BASE-X and SGMII standards is also supported

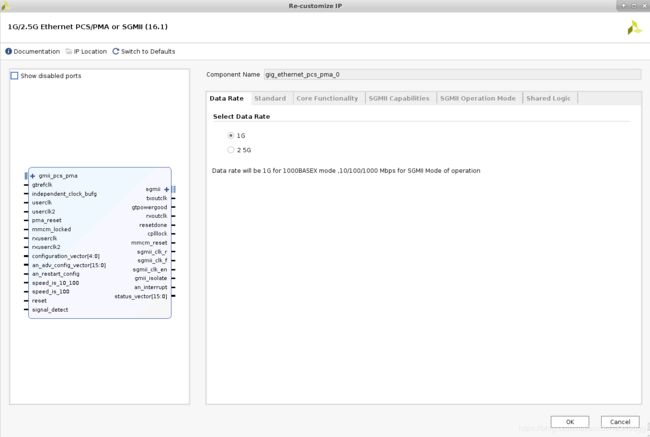

速率和模式

从IP核的名字可以看出,该核通过配置可以生成两种核,光口可以用以太网PCS/PMA mode,电口具有PHY采用SGMII mode,这里速率采用1G,因为其内部有8b/10b转换,所以参考时钟则是125MHz,有效的数据传输速率就变成了125*10*8/10。

备选项如果勾选,IP核就会把底层SerDes的一些寄存器接口引出来供用户配置,这里不需要。

核配置

1000BASEX 的核配置就简单的多了,因为必须要使用到PCS和PMA,因此物理接口必选 Device Specific TR,然后是GMII解析出来的时钟选择,自协商功能勾选,MDIO是一种配置IP核的总线,有时钟、数据、标志信号和中断,我的感觉是提供给CPU用的,给上层提供一个方便的配置管理接口。

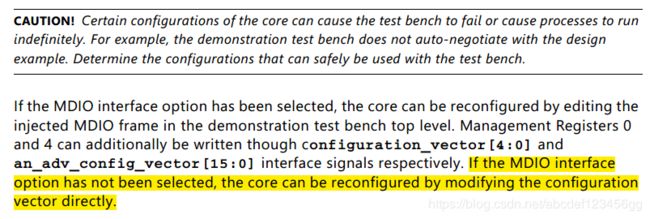

对于FPGA来说,可以采用另一种途径,Configuration Register,通过寄存器的形式去完成配置,虽然FPGA也能利用MDIO总线,总归是麻烦了些,所以就只用默认的寄存器配置途径。

SGMII 模式的物理接口除了可以用 TR ,还可以用 LVDS 接口。

PHY 与 FPGA 跨时钟的 BUFFER 选项,这个看手册 Figure 3-11。

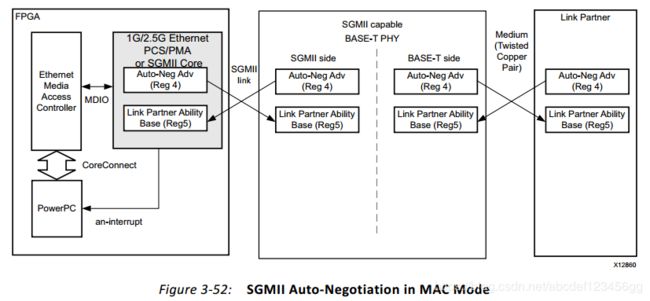

还有工作模式选项,默认MAC mode,勾选PHY mode,这个对自协商功能来说非常重要,因为,只有PHY mode,自协商广播寄存器是可写的(Advertisement register is programmable)。

按照我的理解就是,MAC 模式中的速率、双工、流控等信息只能从对端获取,PHY 模式则可以通知对端自己的配置信息。关于自协商的数据过程,SGMII mode 和 1000BASEX mode 比较类似,都是通过协议里的两个寄存器 Reg4、Reg5 交叉式的通知与获取,当然,并不是像图中那样还有专门的连线,自协商信息也是通过 SGMII 总线收发的,抓 status vector 的信号就可以看到协议里/C/码形式的,bit2 代表的自协商配置信息流(AN CONFIG Sequences),总之,前端选择默认模式就好,但后端一定要选择 PHY mode,因为它必须把自协商信息广播(advertise)给交换芯片的 reg5。

接收 GMIl 时钟源:选择接收路径和 GMII RX 接口的时钟源。2.5G数据速率不支持 RxGmiClkSrc=RXOUTCLK。当选择 RXOUTCLK 时,由于 RX 数据路径与恢复时钟是同步的,所以不需要对 fabric elastic buffer 进行 required 。因此,SGMll 速度选择不需要 SGMIl capability选项卡。

Shared Logic

Xilinx很贴心,它把所需要的外围电路都设计好了,主要包括时钟管理和复位的一些逻辑。

in Core 表示它会把这些逻辑封装进核里,成为一个新核,把处理后的接口引出来。

in Example design 则是会像例子里的一样,外围电路以独立模块的形式呈现。

举个例子,in Example design 模式里 MMCM 会将时钟锁定信息输入到核的 mmcm_locked,而在 in Core 模式,只能看到mmcm_locked_out,模块间的逻辑因为进一步封装而被隐藏了。

因为,需要用它来加速工程开发,并不意味着不要要看它的代码和手册,这里面也有坑,比如,它的异步复位是高有效。

收发器被配置为在 txoutclk 端口上输出该时钟的一个版本(1G为125 MHz, 2.5G为312.5 MHz)。然后 txoutclk 路由到 BUFG_GT。USERCLK:生成 userclk (1G为62.5 MHz、125 MHz,2.5G为312.5 MHz、156.25 MHz)、userclk2 (1G为125MHz, 2.5G为312.5 MHz),并放置到全局时钟路由上。USRCLK:这些时钟被输入回用户接口时钟端口usrclk和usrclk2上的收发机。

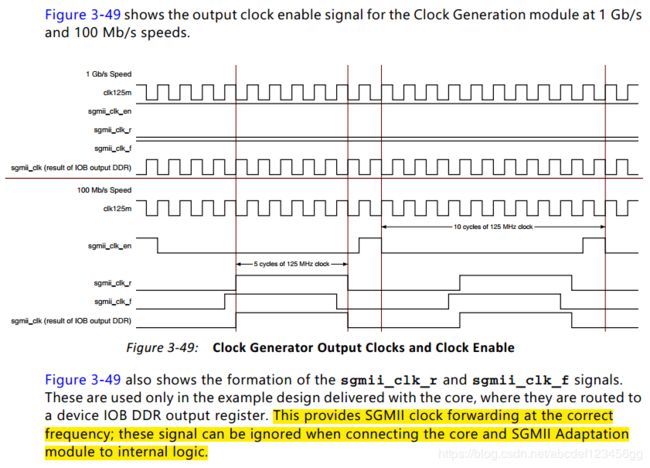

sgmii_clk_r、 sgmii_clk_f

这提供了 SGMII 时钟传递以正确的频率;当将 core 和 SGMII 自适应模块连接到内部逻辑时,可以忽略这些信号。

选择默认的即可。

include shared logic in core:

IP 核的内部信号初始化配置以及常量定义

DRP:Dynamic Reconfiguration Port

status_vector

output 端口,phy 层反馈的信号。

bit 0 :连接状态。这个信号表示链路的状态。

当高时,链路是有效的:链路的同步已经获得,自动协商(如果存在并启用)已经成功完成,收发机的重置顺序(如果存在)已经完成。

当低时,没有建立有效的链接。链接同步失败或自动调整(如果存在并启用)失败。

当启用自动协商时,此信号与状态寄存器第1.2位:链接状态相同。

当禁用自动协商时,此信号与status_vector位[1]相同。在这种情况下,可以使用任何一位。

speed_is_10_100

默认设置为:speed_is_10_100 = 0;speed_is_100 = 0;

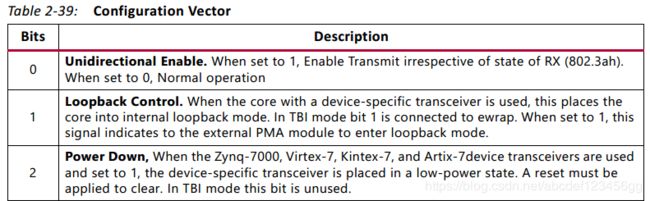

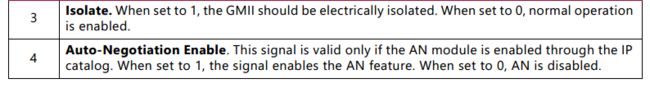

configuration_vector

默认设置为: configuration_vector = 5‘b00000

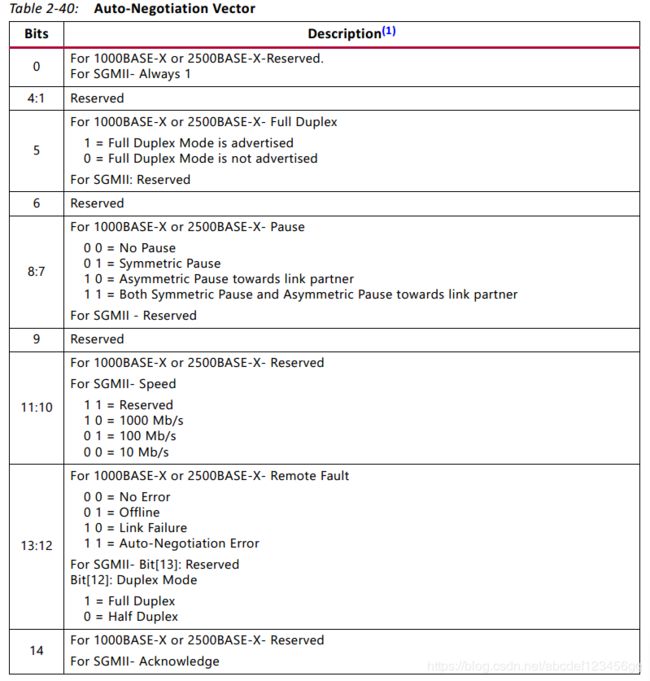

an_adv_config_vector

如果 MDIO 接口没有选择的话,core 可以被配置通过 configuration_vector。

默认设置为(参考 example design): an_adv_config_vector = 15’b0_00_00_0_00_0_1_0000_1

signal_detect

连接出现问题,非 AN 模式下:

查看是否连接:

1. 读 register 1 的 bit 1.2。

2. 查看 status_vector [0] 的 logic 是否是 1。

如果没有连接成功需要进行一下操作:

1. 确保在 core 和 link partner (连接到 core 的设备或测试设备)中禁用自动协商

2. 监视 core 的 signal_detect 输入信号:

2.1. 连接到光模块以检测光的存在。逻辑1表明光模块对光的检测是正确的;逻辑0表示错误。因此,要确保驱动的极性正确。

2.2. signal_detect 信号逻辑置 1。

默认设置为:signal_detect = 1。

an_restart_config

这个信号只有在AN存在时才有效。此信号的上升沿是重写 Bit 9 或 Register 0 的使能信号。为了触发一个 AN 的开始,这个信号应该被置0,然后重新置1。

在 AN 模式下起作用。

默认设置为:an_restart_detect = 0。

reset

异步复位,整个 core 的复位,reset 高电平有效。

sgmii_clk_r、sgmii_clk_f

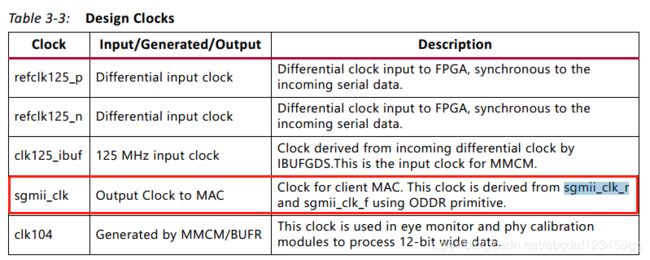

sgmii_clk 输出到 MAC,这个时钟是 sgmii_clk_r、sgmii_clk_f 通过使用 ODDR 的原语得到。

monitor clock for the GMII receiver

在 example design 中

assign mon_rx_clk = gmii_rx_clk;

gmii interface

gmii_rx_er