虚拟存储器和高速缓存总结

概述

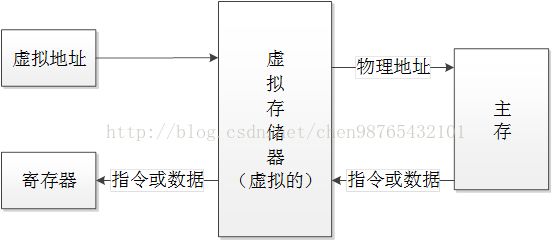

为了更加有效的管理存储器并且少出错,现代操作系统提供了一种对主存的抽象,叫做虚拟存储器。虚拟存储器是被应用程序所意识和使用的。也就是说,它是被抽象出来的,虚拟出来的主存。所以,从应用程序的层面,程序看到的和使用的虚拟地址都是属于虚拟存储器的。虚拟存储器充当一种中间转换的角色,把虚拟地址对应的主存转换到真实的主存上面。

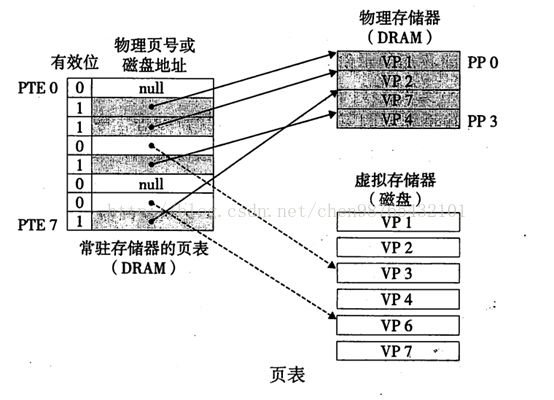

如图:

虚拟存储器是不存在的,是虚拟出来的,如程序文件段,它是对应在磁盘上程序文件所在位置的代码段的,主存中可能存在着一部分或全部的缓存。运行时堆段对应着磁盘上的swap区,主存中可能存在着一部分或全部的缓存。所以,虚拟存储器也可以说对程序段的组织,当需要访问时,再到主存或者虚拟存储器指向的真正位置去取。

虚拟存储器的作用:- 它将主存看成是磁盘的一个高速缓存,在主存中只保留活动的区域,并根据需要在磁盘和主存之间传送数据,进而高效的利用有限的主存。

- 它为每个程序提供了一致的地址空间(虚拟地址空间),简化了存储器管理。例如,加载、链接和共享因虚拟存储器而变的简单。

- 它保护每个进程的地址空间不被其他进程破坏。每个进程的地址空间是私有的,即使所有进程的地址空间范围是一样的,访问的地址也可能相同,但虚拟存储器管理着进程能访问到的真实内存,假如程序访问不存在或使用错误权限访问都将返回错误。

虚拟寻址和物理寻址

程序使用虚拟寻址,物理内存使用物理寻址。

程序执行是产生一条虚拟地址,通过MMU(内存管理单元),转换为物理地址,使用该物理地址访问物理内存,取得数据。地址空间

地址空间包括虚拟地址空间和物理地址空间。假如一个存储器的容量是N=2n字节,那么他有N个地址,n位的地址空间。

CPU产生的地址是虚拟地址,属于虚拟地址空间。现代系统有32位和64位地址空间,这个地址空间就是虚拟地址空间。

物理地址空间是用来寻址物理内存的。

地址空间的概念很重要,它清楚的区分了数据对象(字节)和它们的属性(地址)。那么可以将其推广,允许每个数据对象有多个独立的地址,其中每个地址都选自一个不同的地址空间。这也是虚拟存储器的基本思想。

虚拟存储器架构

缩写解释:

VA:虚拟地址

VPN:虚拟页号

PTE:页表项

PTEA:页表项地址

PA:物理地址

DATA:数据

MMU:内存管理单元

TLB:地址翻译缓冲器

设置存储器层次结构主要是为了缓存低速的存储器。主存是对磁盘等设备的缓存,cache是对主存的缓存,tlb是对主存页表的缓存。

寻址方式:

- tlb是虚拟地址寻址的。

- cache、主存是物理地址寻址的。

- 磁盘是磁盘的方式地址寻址的。

- CPU产生一个虚拟地址,虚拟地址传送到MMU中,MMU首先根据虚拟地址在tlb中找对应的项,对应的项中包含虚拟地址对应的物理地址,如果找到,就用得到的物理地址在cache中找物理地址对应的数据,如果找到,就把数据从cache中返回给CPU。上述的情况是最理想的情况,即tlb命中,cache也命中。

- 如果tlb未命中,则MMU根据VA,应用一定的逻辑计算出PTE的物理地址(PTEA)。用PTEA在cache中找对应的数据(PTE),如果cache命中,把PTE返回给MMU,并填充到TLB中,下次再查找TLB时,TLB就会命中了。

- 如果CACHE未命中,则用PA从主存中取数据,返回数据并填充CACHE对应部分,下次就可以从CACHE中命中。

- 还有一种情况是,如果请求的数据未在主存中缓存,而是在磁盘中,例如页表项(PTE)中对应的地址是磁盘的地址,主存未命中,称为缺页,则缺页处理程序(操作系统)从主存中找到合适的位置,把磁盘中的内容填充到相应位置。

存储器的相联方式

主存对磁盘的缓存

主存和磁盘之间缓存的单位是页。页的大小默认是4k,也有大页2M,甚至1G的,关于大页的讨论,以后再写文章讨论。也就是说,主存缓存磁盘内容是页大小的整数倍,那么页的基地址的最后12位必然是全0的。

cache的访问速度是主存的10倍,主存的访问速度是磁盘(机械)的100000倍。所以,缺页的代价是严重的,所以主存对磁盘的相联方式采用全相联的方式,即磁盘上的一页可以放到主存的任意一页中。并且因为访问磁盘的时间很长,主存总是采用写回的方式,而不是直写。cache对主存的缓存

虚拟地址和物理地址的转换

页表

MMU

TLB对页表的缓存

TLB种类:

在X86体系的CPU里边,一般都设有如下4组TLB:

- 第一组:缓存一般页表(4K字节页面)的指令页表缓存(Instruction-TLB)

- 第二组:缓存一般页表(4K字节页面)的数据页表缓存(Data-TLB)

- 第三组:缓存大尺寸页表(2M/4M字节页面)的指令页表缓存(Instruction-TLB)

- 第四组:缓存大尺寸页表(2M/4M字节页面)的数据页表缓存(Data-TLB)

实例:intel core i7 高速缓存结构

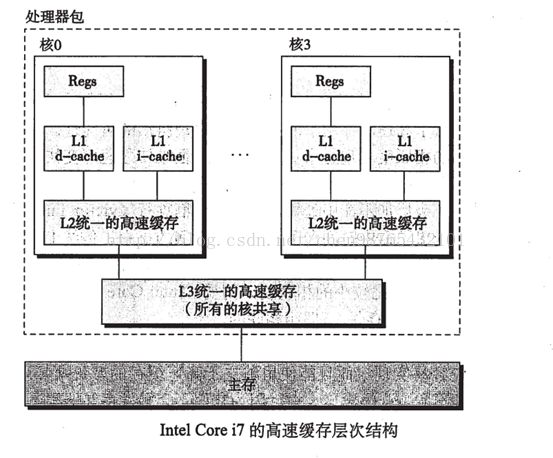

结构化的高速缓存层次结构

- L1cache通常包括两个单独的i-cache(指令cache)、d-cache(数据cache)

- L3 cache是同一颗CPU多核间共用的。

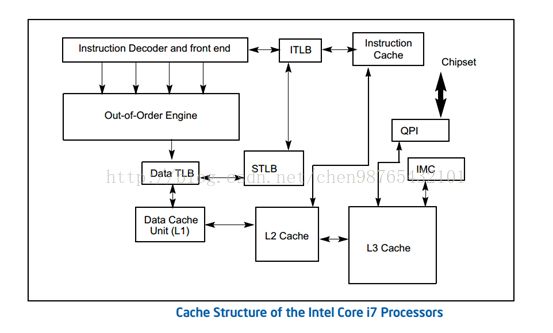

i7存储器系统

说明:

L2统一TLB:Second-level Unified TLB(4-Kbyte Pages),通常称为STLB,是i7在原TLB上专门增加的又一级更大的512条目的TLB cache,这样的话TLB的缓存就不用缓存在cache系统中了,而是缓存在STLB中。当TLB和STLB都不明中的时候,MMU会把主存中的相关页表项缓存在STLB中,而非L1、L2、L3cache系统中。i7高速缓存参数

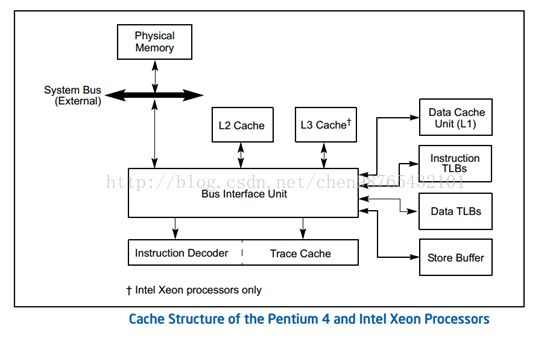

i7详细cache结构

Table 1. Characteristics of the Caches, TLBs, Store Buffer, and

Write Combining Buffer in Intel 64 and IA-32 Processors

| Cache or Buffer |

Characteristics |

||

| Trace Cache1 |

• Pentium 4 and Intel Xeon processors (Based on Intel NetBurst® microarchitecture): 12 Kìops, 8-way set |

||

| L1 Instruction Cache |

• Pentium 4 and Intel Xeon processors (Based on Intel NetBurst microarchitecture): not implemented. |

||

| L1 Data Cache |

• Pentium 4 and Intel Xeon processors (Based on Intel NetBurst microarchitecture): 8-KByte, 4-way set |

||

| L2 Unified Cache |

• Intel Core 2 Duo and Intel Xeon processors: up to 4-MByte (or 4MBx2 in quadcore processors), 16-way set |

|

|

| L3 Unified Cache |

• Intel Xeon processors: 512-KByte, 1-MByte, 2-MByte, or 4-MByte, 8-way set associative, 64-byte cache line |

|

|

| Instruction TLB |

• Pentium 4 and Intel Xeon processors (Based on Intel NetBurst microarchitecture): 128 entries, 4-way set |

|

|

| Data TLB (4-KByte |

• Intel Core i7, i5, i3 processors, DTLB0: 64-entries, 4-way set associative. |

|

|

| Instruction TLB |

• Intel Core i7, i5, i3 processors: 7-entries per thread, fully associative. |

|

|

| Data TLB (Large |

• Intel Core i7, i5, i3 processors, DTLB0: 32-entries, 4-way set associative. |

|

|

| Second-level Unified |

• Intel Core i7, i5, i3 processor, STLB: 512-entries, 4-way set associative. |

|

|

| Cache or Buffer |

Characteristics |

|

|

i7地址翻译

说明:

VPN和VPO的翻译是同步进行的,在用VPN查找页表中对应的PPN的同时,用VPO(12位)查找L1 cache(6+6位)取得其中的标记,再用PPN和标记比较,检查是否命中。i7页表翻译

参考文献

- 深入理解计算机系统(原书第3版)

- Intel®64 and IA-32 Architectures Software Developer’s Manual Volume 3A: SystemProgramming Guide, Part 1