ARM安全技术-使用TrustZone技术构建安全系统(翻译)

第一章 介绍

本章提供了一些与嵌入式系统安全相关的背景知识。

本章包括以下部分:

•什么是安全?第1-2页

•第1-4页的安全需求

•威胁是什么?第1-6页

1.1 什么是安全?

在非常抽象的术语中,术语security可用于涵盖设计的许多非常不同的基本特性。但是,它本质上是系统的一个属性,确保有价值的资源不会被复制、损坏,或者让真正的用户无法使用。每个系统设计都需要一组不同的安全属性,这取决于它试图抵御恶意攻击的资产的类型和价值。

资产

值得保护的有价值的资源。资产可以是有形的对象,例如用户密码,也可以是无形的资产,例如网络可用性。

攻击

故意获取、损坏或破坏其无权访问的资产的行为。

攻击可能包括使用恶意软件、硬件监控和硬件篡改。

保护

设计一个系统行为,包括硬件或软件机制,提供对抗攻击的对策。

1.1.1 基本安全特性

几乎所有高级属性都可以其作为基础的基本安全属性是机密性和完整性。

保密性

机密资产不能被一组定义的攻击复制或窃取。此属性对于密码和加密密钥等资产是必需的。

完整性

保证其完整性的资产不受一组已定义的攻击的修改。此属性对于系统其余安全性所基于的某些设备上的根机密以及安全软件在运行后都是必需的。

真实性

在某些情况下,设计不能提供完整性,因此提供了真实性的属性。

在这种情况下,攻击者可以更改资产的值,但防御者将能够在使用资产之前检测到更改,从而在攻击导致安全错误之前检测到更改。

此属性对于安全软件至关重要。

如果攻击者可以在程序代码加载到安全执行位置之前对其进行篡改,而不被检测到,则可以绕过软件提供的安全性。

1.1.2 安全解决方案的局限性

所有的安全解决方案都是为了防御可能遭受的攻击的一个子集。防御所有可能的攻击是不可能的任务;总有人愿意花费大量的时间和金钱来使用非常复杂的攻击来破坏任何安全方案。因此,设计必须决定它要保护哪些资产,以及它要保护这些资产免受哪些可能的攻击。这也许是设计过程中最关键的部分;

保护错误资产免受错误或不完整攻击列表的设计很容易被破坏。

假设所有的安全性都可以用足够的时间和金钱来打破,那么设计的安全性要求不应该被描述为“无法绕过”,而应该用价值术语来描述:“对资产B的攻击A至少需要Y天和Z美元”。如果一组对策意味着一次成功的攻击将花费太长或太多的时间,那么防御就是成功的。大多数攻击者在这种情况下会转移到另一个目标。

1.2 安全需求

嵌入式设备正在处理越来越有价值的数据,例如消费者银行凭证。它们也在稳步成为具有高水平的设备外连接的开放软件平台,使消费者能够下载任意第三方应用程序。这使得这些设备处于高风险状态。在桌面环境中,开放式软件平台、任意应用程序下载和设备上的有价值资产的组合被证明显著增加了被利用的安全漏洞的风险。此外,如果通过这些系统的数据的价值在增加,攻击者更有可能投资于破坏它们。

ARM TrustZone技术的目的是使设备能够从功能丰富的开放操作环境和健壮的安全解决方案中获益。一个设计良好的系统硬件架构和适当的安全软件设计可以确保敏感数据保持安全,无论不太可信的操作环境做什么。

1.2.1 硬件强制安全

使嵌入式产品免受恶意攻击会对整个系统设计产生影响。设备中的硬件和软件必须协同工作,以便能够针对正确类型的攻击采取可靠的安全对策。可信计算小组白皮书《在融合网络上保护移动设备安全》指出,从设计过程开始,从处理器核心和SoC基础设施的规范开始,受保护最好的系统具有专用的硬件安全措施。在这个早期阶段对硬件安全性的仔细考虑允许在设备中内置保护,这在以后的设计过程中是不可能添加的。

ARM TrustZone技术通过将保护措施集成到ARM处理器、总线结构和系统外围IP中,实现了这种级别的系统范围安全。通过集成硬件和软件组件的组合,TrustZone技术提供了一个框架,允许在对设备成本影响最小的情况下实现多种安全系统架构。

1.3 什么是危险?

在探索TrustZone硬件体系结构的细节之前,重要的是了解在这种情况下安全性的含义,以及与预防成本相比,攻击带来的风险是什么。只有掌握这些信息,系统设计师才能在硬件或软件防御方面做出合理的设计选择。

有许多关于嵌入式系统抵抗攻击失败造成损失的例子,跨越多个应用和行业。一些攻击(如支付欺诈)会导致服务提供商必须承担直接的成本,而另一些攻击(如在机顶盒中添加经过修改的硬件芯片)则会在设备的整个生命周期内造成长期的收入损失。

1.3.1 市场部门概述

每个市场部门试图防范攻击的敏感资产是多种多样的。

例如,移动手机旨在保护无线网络的完整性,而电视机顶盒则防止未经授权访问订阅频道。受保护资产的不同类型和价值,再加上不同的底层系统实现,意味着每种攻击所经历的情况也各不相同。本节旨在概述在某些可能部署TrustZone技术的市场部门中安全历史的一小部分。

移动部门

GSM手机的两个关键部分是国际移动设备识别码IMEI(一个用于在连接到网络时识别单个手机的唯一的15位代码)和一个用于将特定设备绑定到特定网络运营商的SIM卡的低级SIMLock协议。

这两个组件都用于提供安全功能:IMEI用于阻止被盗手机访问网络,SIMLock协议用于在合同期间将设备绑定到运营商。在许多手机上,这两种保护机制都可以通过使用USB线和运行在桌面工作站上的再编程工具不费吹灰之力地被绕过。实施过程中的这些不安全性导致了欺诈行为的大规模发生,据英国路透社(Reuters UK)报道的统计数据显示,手机盗窃推动了一半的街头犯罪,每年给整个行业造成数十亿美元的损失。

新移动设备上的安全要求不再仅仅与网络有关,还与设备上本地可用的内容和服务有关。通过数字版权管理(DRM)保护数字媒体内容,以及保护机密用户数据(如同步电子邮件帐户)正变得越来越重要,因为运营商和用户都试图从其设备中获得更多价值。

消费电子和嵌入式领域

对便携式游戏机和家庭电影播放器等消费电子产品的需求正与移动市场上的需求趋同。越来越多的有线和无线连接、更大的用户数据存储、可编程内容的动态下载以及更高价值服务的处理,都表明需要一个高性能和健壮的安全环境。

安全攻击不限于具有用户可扩展软件堆栈的开放系统。

在汽车市场中,大多数系统都是封闭的或深度嵌入式的,然而里程表欺诈(里程计读数被回滚以抬高二手车的价格)仍然普遍存在。美国交通部报告称,仅这一欺诈行为每年就使美国消费者在汽车价格虚高的情况下损失数亿美元。

这些嵌入式系统中通常面临的安全特性是那些验证固件更新是否真实的特性,以及那些确保调试机制不会被恶意使用的特性。这些需求可以通过使用ARM TrustZone技术构建的精心设计的系统来满足。

1.3.2 安全问题的经济价值

如果使用风险分析来平衡成功攻击的概率、成功攻击对业务的成本以及防止该攻击的成本,那么几乎每一个安全设计都是合理的。在某些情况下,风险分析表明攻击的概率太低,不值得防御。在其他情况下,与被保护资产的价值相比,保护措施的成本太高。

然而,在大多数情况下,某种形式的资产保护是合理的。接下来的几章将展示ARM TrustZone技术可以潜在地降低实现安全解决方案的成本;该体系结构允许降低系统复杂性,从而降低设计成本、开发成本和测试成本。这使得系统设计能够保护比历史上更广泛的资产,如果仅仅是出于经济原因的话。

许多可能的攻击者也可以被认为是出于经济原因。业界最大的损失来自于专业黑客而非最终用户的攻击,而专业黑客的主要动机是获得经济利益。他们对一次攻击的投资不会超过他们合理预期的财务回报。

许多设备攻击都是由专业罪犯、学术安全研究人员和在家工作的爱好者发起的。无论是为了经济利益、学术声望,还是仅仅为了娱乐,这些组织都可以将大量时间集中在分析系统和开发旨在破坏系统的复杂攻击上。

这些攻击最受追捧的结果是同类破坏;一种容易复制的攻击,可以用来破坏整个一代或一类设备。属于这一类的最广泛发布的攻击是针对消费娱乐设备部署的攻击,例如破坏游戏机软件限制和DVD电影内容保护方案的攻击。

在许多设备硬件受到攻击的同类破坏场景中,攻击者的第一次调查研究可能会花费大量的成本。这笔钱投资用于获得工具,如电子显微镜和晶体管激励激光器,用于硅级别分析。此类攻击的目标是发现安全弱点,这些弱点随后可以在多个设备上利用,而无需付出巨大代价。如果可攻击设备的数量足够多,这些同类破坏的攻击会极大地改变经济论据的平衡,有利于攻击者。

实证经济学

安全环境的好处不仅仅局限于技术上。研究表明,增强消费者对易用和安全支付系统的信心,可以将消费者的支出提高20%,同时也可以加快新收入来源和不同商业模式的吸收。

在设备制造商越来越多地处于消费者意识到安全问题的大环境下,设备的安全特性正成为一个具有差异化的竞争点。

具有良好安全审查和有用安全功能的设备将优先于在这些方面没有明确考量的设备被选择。对于部署到企业环境中的设备尤其如此,在企业环境中,移动设备可以连接到内部网络。将机密电子邮件和日历约会同步到智能手机的功能非常有用,但正如《华盛顿邮报》报道的那样,如果设备丢失或被盗,所属公司将面临高风险。许多公司现在限制了对公司网络的访问,降低了智能设备的价值,或者要求设备本身附加安全机制。

1.3.3 如何发起设备攻击?

设计中的下一个最重要的因素是用于执行攻击的机制。执行攻击的不同机制称为攻击向量,这些机制分为本文档中定义的三类:黑客攻击、shack攻击和实验室攻击。

黑客攻击

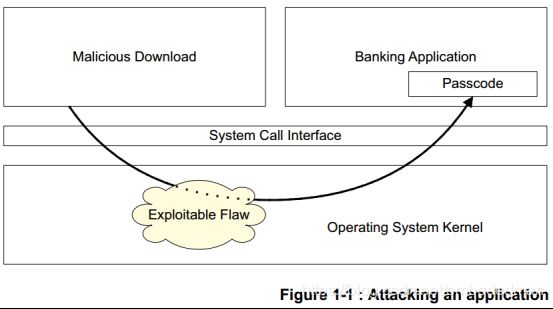

黑客攻击是指黑客只能执行软件攻击。

黑客攻击的例子包括通过物理或无线连接下载到设备的病毒和恶意软件。

在许多成功的黑客攻击案例中,设备用户无意中批准安装软件,然后执行攻击。这可能是因为恶意软件假装是用户确实要安装的软件的一部分,或者是因为用户不理解操作环境显示的警告消息。在“安全Java”一书中,有一节总结了典型用户在选择安全性和所需功能时的决策能力:“如果在跳舞的猪和安全性之间做出选择,用户每次都会挑选跳舞的猪。”

shack攻击

shack攻击是一种低成本的硬件攻击,使用的设备可以从商业街上的商店购买,如radio shack。在这些情况下,攻击者可以物理访问设备,但没有足够的设备或专业知识来攻击集成电路包。攻击者可以尝试使用JTAG调试、边界扫描I/O和内置自检工具连接到设备。他们可以使用逻辑探针和网络分析仪被动地监视系统,以监听总线、管脚和系统信号。攻击者还可以执行简单的主动硬件攻击,例如强迫管脚和总线处于高电压或低电压,重新编程内存设备,以及用恶意替代品替换硬件组件。

实验室攻击

实验室攻击载体是最全面、最具侵入性的。如果攻击者可以使用实验室设备,如电子显微镜,他们可以对设备执行无限的逆向工程。必须假设攻击者可以对设计中的任何敏感部分(包括逻辑和存储器)进行晶体管级的反向工程。

攻击者可以对设计进行反向工程,将微观逻辑探针连接到硅金属层,并使用激光或其他技术使正在运行的电路出现故障。攻击者还可以监视模拟信号,如设备电源使用和电磁辐射,以执行加密密钥分析等攻击。

在大多数情况下,考虑到每个设备都可能被破坏的经验法则,设备不应试图直接防御实验室攻击,而应采取措施限制设备被破坏时的损害,从而使实验室攻击不划算。使用每设备唯一秘钥就是一个例子,其中反向工程单个设备不会向攻击者提供有用的信息;它们拥有自己已经拥有的设备的秘钥,但不拥有该类中的任何其他设备的秘钥。

注意

TrustZone技术旨在在安全组件和SoC基础设施的其他部分之间提供硬件强制的逻辑分离。

实验室攻击不在TrustZone技术提供的保护范围内,但如果某些资产需要物理攻击保护,则使用TrustZone的SoC可以与ARM Securore©智能卡结合使用。

1.3.4 谁会发起设备攻击?

一旦设计人员确定了资产和可能的攻击,就必须确定可能的攻击者。不同的攻击者可以部署不同类型的攻击,某些资产只会吸引某些攻击者。此分析有助于合理化每个资产需要防范的攻击。

分析还应包括明确信任谁可以访问存储在设备上的资产的描述。这会突出安全模型中的弱点。

在已经公布的一些案例中,消费者数据被维护或维修技术人员从设备上窃取,随后在互联网上公布。

远程攻击者

攻击者的经典视图是我们在桌面工作站上看到的恶意软件的分发服务器:病毒和其他恶意软件。这些攻击者对他们正在攻击的设备没有物理访问权限,但可能有权访问类似的设备来发起攻击,并依赖于利用软件漏洞和用户错误来获取对敏感资源的访问权限。

嵌入式设备的软件复杂性不断增加,这意味着攻击者可以利用的漏洞在统计上更多。安装第三方代码的功能,包括执行基于浏览器的内容,使恶意代码更容易进入设备执行攻击。

安全专家

最有技术能力的攻击者是犯罪团伙、安全专家和用户,他们为了好玩而攻击设备。这个群体能够执行如第1-10页所述的实验室攻击。

此类攻击者通常试图发现可在大量设备上复制的同类破坏攻击。此辅助攻击可能由另一个攻击者部署。

可信开发人员

一种通常未经深思熟虑的攻击是由一个可以被认为是可信的人执行的,或者至少是协助的。有公司员工最终被新闻曝光,因为他们窃取了与设计相关的秘密信息,或者故意破坏了内部计算机网络。在许多情况下,这些员工在被发现攻击的前一天会被认为是被明确信任的。

利用经济论据来证明防御此类攻击的正当性,贿赂有权获得设计信息的人通常比反向工程一块硅晶要便宜,也更快。

虽然这类攻击很难防范,但可以在业务流程中使用一些防御措施。限制访问敏感材料,审查谁访问过这些材料,这样的业务流程可以使用。

设备所有者

我们将在本文档中讨论的针对设备的最后一组攻击者是设备所有者本身。这组攻击者的典型目标是获得对服务和内容的自由访问。一般来说,设备所有者有动机执行攻击,但在技术上不称职。一位技术专家将开发出一种攻击,并在线发布其详细信息;设备所有者所要做的就是按照配方进行复制。

值得注意的是,这类设备的拥有者暴露在比通常更高的攻击风险中。他们试图破坏现有的保护措施时,错误地从由黑客托管的网站下载了预先打包的攻击软件;这些网站通常包括病毒和其他恶意软件,用户随后会无意中将这些软件安装到他们的系统上。

第二章 系统安全

本章在介绍ARM TrustZone硬件架构之前首先概述一下嵌入式系统中一些已经存在的安全选项。本章内容包括:

page2-2 系统安全

page2-7 TrustZone 硬件安全

2.1 系统安全

嵌入式设备的系统设计非常复杂,包括多个独立的处理器核心、DMA引擎等二级总线masters以及大量的内存和外围总线slaves。除了这些功能组件外,通常还有一个并行的系统基础设施用来提供侵入式和非侵入式调试功能,以及组件边界扫描和内置自测试(BIST)功能。

平台中的每一个子系统的设计和集成必须使其与安全解决方案协同工作,而不是独立于安全需求开发每一个子系统。如果设备的威胁模型表明它需要防范shack攻击,那么仅保护系统的功能部分是没有意义的。对调试端口具有无限制访问权限的攻击者可以绕过可能存在的许多功能性保护。

本节旨在介绍一些历史上在市场上可用的安全体系结构,以及它们的优缺点。

2.1.1 外部硬件安全模块

嵌入式应用的经典安全解决方案是在主SoC之外包含一个专用的硬件安全模块或可信元件。例如,手机中的SIM卡,或机顶盒中的条件访问智能卡。

优点

外部安全设备将资产封装在一个物理设备中,该物理设备是为可靠的安全性而设计的。完全独立的设计和制造流程,可以使用技术和硅工艺,从而提供高水平的抗篡改性和物理安全性。智能卡的制造和个性化过程经常通过批准的评估方案得到正式认证。这使得它们适合于需要高度安全保证的用例,例如信用卡和借记卡支付方案。

缺点

用于智能卡的硬件技术和过程对于标准SoC设计来说是不切实际的,因为它们会给设计过程增加很大的工作量,并损害设备的面积、功率效率和性能。提供物理安全性的制造方法也迫使处理器性能的下降(损耗大约为5-20MHz),以及设备内少量的RAM损耗。这些设计特征将可以部署在智能卡上的可能用例限制为可以从非易失性存储器运行的相对静态程序,这些程序不需要安全边界上连续的高带宽通信。智能卡的另一个问题是,它们只提供处理和安全存储功能;它们无法直接访问父设备的任何用户界面。智能卡依赖于在其安全边界之外运行的软件来提供这些设施,因此无法保护所有感兴趣的资产。例如,用户输入的个人识别码(PIN)必须由智能卡之外的不太安全的软件管理,从而使其容易受到攻击。智能卡的商业缺点可能比技术上的更为严重。在主SoC旁边提供一个智能卡是昂贵的,因此对大多数资产来说是不经济的,因为它们不够有价值。

2.1.2 内部硬件安全模块

位于SoC中的硬件安全模块牺牲了智能卡所提供的硬件防御,以降低成本并方便成为系统的一个集成部分。集成模块的精确形式各不相同,但有两种主要形式。第一个是管理加密操作和密钥存储的硬件模块。第二个是一个通用的处理引擎,放在主处理器旁边,它使用自定义硬件逻辑来防止对敏感资源的未经授权的访问。

优点

与智能卡选项相比,这些系统的主要优势是显著的成本降低和性能改进。

为安全子系统提供专用通用处理器的系统在安全性方面与TrustZone硬件解决方案相当。

缺点

加密模块实现与智能卡有一个类似的问题,即它们具有受限的边界,因此只能保护加密密钥材料。密码学本身是一种工具,而不是一个目标;由密码学方法保护的资源将不可避免地需要在密码学模块之外使用,它们不再受其保护并且可能受到攻击。与TrustZone系统相比,提供专用于安全子系统的辅助通用处理器的设计具有较小的缺点。一个问题是,该设计需要单独的物理安全处理器。这种处理器通常比主应用程序处理器的功能要弱,而且还消耗大量的硅晶面积。另外,两个处理器之间的通信需要将任何数据刷新到相关存储器中,而相关存储器通常是外部存储器。这个操作很费时,需要消耗大量的能量。另一个问题是,任何资源分离都需要在SoC内部的专用硬件扩展中实现。这需要大量的设计和测试工作,迁移或扩展系统变得更加困难。

这里介绍的密码模块和辅助处理器解决方案通常试图保护系统的功能方面。SoC中调试和测试机制所带来的系统安全风险往往被忽略,并提供了一个易受攻击的接口。为了避免这个问题,必须完全禁用调试,这使得在现场诊断软件问题变得困难。

2.1.3 软件虚拟化

虚拟化是一种软件安全机制,其中一个高度可信的管理层(称为hypervisor)以通用处理器的特权模式运行。

hypervisor使用内存管理单元(MMU)分离运行在其上的多个独立软件平台,将每个平台放在由hypervisor软件控制的虚拟机中。

一些虚拟机监控程序的紧凑性意味着,如果能够对它们进行彻底的测试,那么在其控制的一个虚拟机中运行的软件可以确信,它不会受到在另一个虚拟机中运行的软件的攻击。

注意

本节介绍半虚拟化,这是嵌入式市场中常见的虚拟化类型。也存在对于hypervisor有一种特殊的处理器模式的处理器体系结构。这些体系结构允许hypervisor托管一个完整的操作系统,然后可以使用MMU细分hypervisor提供的内存空间。

优点

任何带有MMU的处理器都可以用来实现虚拟化解决方案,一些常见的富操作系统已经被移植到它们上面运行,也不需要额外的硬件来实现hypervisor。安全敏感的应用程序可以被移植到运行在hypervisor上面的安全环境中运行,但不在富操作环境的视图范围内。hypervisor可以提供通信机制,用于允许软件虚拟机通信。

缺点

虚拟化技术提供的隔离仅限于实现hypervisor的处理器。系统中的任何其他总线主机,如DMA引擎和图形处理单元(GPU),都可以绕过hypervisor提供的保护,因此也必须由hypervisor管理,以强制执行所需的安全策略。

这在不损害系统性能的情况下很难实现;在不降低图形性能的情况下验证可编程GPU的复杂输入超出了大多数虚拟化解决方案的范围。虚拟化忽略与硬件攻击相关的安全问题,例如使用调试或测试基础结构的威胁。为了保护虚拟化系统免受此类攻击,您需要完全禁用调试和测试可见性,这使得软件开发和现场缺陷诊断非常困难。

2.2 TrustZone 硬件安全

与前一节讨论的安全系统相关的问题之所以存在,是因为设计只能保护系统中受限制部分的某些资产,或者是因为安全解决方案忽略了攻击问题空间的大部分。在许多情况下,安全设计的限制性意味着错误的资产受到保护。加密硬件模块主要设计用于保护密钥,这些密钥无疑是宝贵的资产,但如果攻击者在加密硬件之外的媒体播放器中使用解密内容时,能够反复窃取这些内容,那么密钥的保护对内容权限所有者来说就没有什么安慰作用。对今天部署的真实设备的攻击是广泛和多样的,但可以显示为涵盖了本章前面概述的所有攻击配置。任何只试图满足其中一个威胁区域的安全解决方案,都忽视了问题的一半以上,无法抵御现实世界中存在的许多攻击。这可能会使许多解决方案实现的安全级别低于它们打算提供的级别,从而意味着许多资产没有得到充分的保护。

2.2.1 系统范围安全

在嵌入式世界中实现可信计算的ARM方法是基于可信平台的概念;一种在整个系统设计中扩展安全基础设施的硬件架构。TrustZone体系结构并未对某个专用硬件模块中的资产进行保护,而是使系统的任何部分都变得安全,从而实现了包括功能单元和调试基础框架在内的端到端安全解决方案。适当使用建立在TrustZone架构之上的安全协议,例如安全启动和验证调试启用,许多可能的黑客和shack攻击威胁可以有某种形式的对策。如果这些防御措施可以与减轻实验室攻击相关风险的方法结合使用,例如,通过让每个设备使用统计上唯一的秘钥,那么将会呈现一个非常强大的解决方案。

第三章 TrustZone硬件架构

本章详细介绍了TrustZone硬件体系结构及其对系统结构、处理器和调试基础结构的影响。

本章包括以下部分:

•第3-2页概述

•第3-4页的系统架构

•处理器架构见第3-6页

•调试架构,第3-17页

3.1 概述

TrustZone硬件体系结构旨在提供一个安全框架,使设备能够应对其将遇到的许多特定威胁。TrustZone技术没有提供固定的一刀切的安全解决方案,而是提供了基础设施,允许SoC设计者从一系列可以在安全环境中实现特定功能的组件中进行选择。

该体系结构的主要安全目标实际上相当简单:能够构建一个可编程环境,使几乎任何资产的机密性和完整性都能免受特定攻击。一个具有这些特点的平台可以用来构建一系列广泛的安全解决方案,而这些解决方案在传统方法中并不具有成本效益。

系统的安全性是通过划分SoC的所有硬件和软件资源来实现的,这样它们就存在于两个世界中的一个:安全子系统的安全世界,以及其他一切的正常世界。启用了TrustZone的AMBA3 AXI™ 总线结构中提供的硬件逻辑确保正常世界组件不能访问任何安全世界的资源,从而在两者之间建立一个强大的安全边界。将敏感资源放在安全世界实现了在安全处理器核心上运行的健壮软件,可以保护几乎任何资产免受许多可能的攻击,包括那些通常难以保护的攻击,例如使用键盘或触摸屏输入的密码。

TrustZone硬件体系结构的第二个方面是在一些ARM处理器核心中实现的扩展。这些附加功能使单个物理处理器核心能够以时间切片的方式安全高效地执行来自正常世界和安全世界的代码。这消除了对专用安全处理器核心的需求,节省了硅晶面积和功耗,并允许高性能安全软件能够与正常世界操作环境同时运行。

TrustZone硬件体系结构的最后一个方面是一个具有安全意识的调试基础框架,它可以控制对安全世界调试的访问,而不影响正常世界的调试可见性。这三个方面的每一个都将在本章后续章节中详细讨论。注意《ARM架构参考手册》和许多硬件组件技术参考手册使用了“安全”和“非安全”这两个术语,它们相当于安全世界和正常世界。

仅提及硬件时,本文档将使用安全和非安全命名约定,以避免混淆。术语“安全世界”和“正常世界”将用于描述构成每个执行环境的硬件和软件的组合。

3.2 系统架构

系统IP的体系结构更改提供了将硬件资源分为两个世界的机制。本节介绍这些更改的影响以及已修改的组件。

3.2.1 The AMBA3 AXI system bus

扩展总线设计的最大特点是为主系统总线上的每个读写通道添加额外的控制信号。这些位称为非安全位或NS位,并在公共AMBA3高级扩展接口(AXI)总线协议规范中定义。

•AWPROT[1]:写事务-低是安全的,高是不安全的。

•ARPROT[1]:读事务-低是安全的,高是不安全的。

所有总线master设备在进行新事务时设置这些信号,总线或slave设备解码逻辑必须对它们进行解释,以确保不违反所需的安全分离。所有不安全的master设备必须在硬件中设置NS位为高,这使得它们无法访问安全的slave设备。访问的地址解码将与任何安全slave不匹配,事务将失败。

如果非安全master尝试访问安全的slave,则实现将定义该操作是以静默方式失败还是生成错误。根据硬件外围设备设计和总线配置,slave或总线可能引起错误,因此可能发生SLVERR(从机错误)或DECERR(解码错误)。

3.2.2 The AMBA3 APB peripheral bus

TrustZone体系结构最有用的特性之一是能够保护外围设备,如中断控制器、计时器和用户I/O设备。这使得安全环境得以扩展,从而可以解决一些更广泛的安全问题,这些问题不仅仅需要一个安全的数据处理环境。安全中断控制器和定时器允许不可中断的安全任务监视系统,安全时钟源支持健壮的DRM,安全键盘外围设备支持安全输入用户密码。AMBA3规范包括一个称为高级外围总线(APB)的低门计数、低带宽外围总线,它使用AXI-to-APB网桥连接到系统总线。APB总线不包含与NS bits相当的位。这确保了现有的AMBA2 APB外围设备与实现TrustZone技术的系统兼容。AXI-to-APB网桥硬件负责管理APB外围设备的安全性;网桥必须拒绝不适当安全设置的事务,并且不得将这些请求转发给外围设备。

3.2.3 Memory aliasing

将NS位添加到总线事务和系统中的任何缓存标记中,都可以被视为提供了第33个地址位。安全事务和非安全事物各有32位物理地址空间。

与任何地址空间一样,包括那些不使用TrustZone技术的地址空间,必须注意确保33位地址空间的使用方式使其存储的所有位置的数据保持一致,否则可能导致数据损坏。

考虑这样的情况:安全世界的master希望访问缓存的非安全slave。设计可以实现以下任一选择:

•master对slave进行非安全访问。

•master对slave进行安全访问,非安全的slave接受安全事务,但slave将这些访问视为不安全的。

在第二种设计中,硬件必须支持地址空间别名。在这个别名内存系统中,相同的内存位置在地址映射中显示为两个不同的位置,一个安全,一个不安全。因此,可以有多个值同时表示高速缓存中存在的相同数据。对于可修改的数据,此别名会导致一致性问题;如果一个数据副本被修改,而另一个存在于缓存中,则您将拥有两个不同版本的数据。系统设计者必须意识到潜在的数据一致性问题,并且必须采取措施避免这些问题。

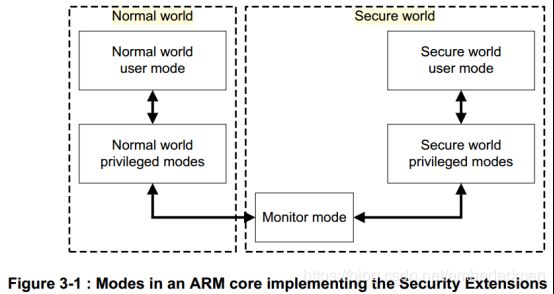

3.3 Processor architecture

最重要的体系结构更改适用于实现体系结构安全扩展的ARM处理器。目前包括:

•ARM1176JZ(F)-S型™ 处理器

•Cotex™-A8处理器

•Cortex-A9处理器

•Cortex-A9MPcore™ 处理器

这些设计中的每个物理处理器核心都提供了两个虚拟核心,一个被认为是不安全的,另一个是安全的,以及在它们之间可靠地进行上下文切换的机制,称为监视器模式。在主系统总线上发送的NS位的值是从执行指令或数据访问的虚拟核心的标识间接派生的。这使得虚拟处理器可以简单地集成到系统安全机制中;非安全的虚拟处理器只能访问非安全系统资源,但安全虚拟处理器可以看到所有资源。

3.3.1 Switching worlds

这两个虚拟处理器以时间切片的方式执行,在更改当前运行的虚拟处理器时,上下文将通过名为monitor mode的新核心模式进行切换。物理处理器从正常世界进入监控模式的机制受到严格控制,并且都被视为监控模式软件的异常。监控模式的入口可以由执行专用指令的软件、安全监控调用(SMC)指令或硬件异常机制的子集触发。IRQ、FIQ、外部数据中止和外部预取中止异常都可以配置为使处理器切换到监视模式。

在监视模式下执行的软件是实现定义的,但它通常保存当前世界的状态,并恢复正在切换到的世界的状态。然后,它执行从异常返回以在还原的世界中重新启动处理。

处理器正在执行的世界由系统控制协处理器CP15中安全配置寄存器(SCR)中的NS位指示,除非处理器处于监视模式。当处于监视模式时,无论SCR NS位的值是多少,处理器总是在安全的世界中执行,但是如果SCR NS位设置为1,则对banked CP15寄存器的操作将访问正常世界的副本。

注意

如果安全世界软件在处理器不处于监视模式时将SCR NS位设置为1,则处理器将立即切换到正常世界中运行。这将降低软件对仍在运行中的指令执行的可信性,以及对处理器寄存器中保存的任何数据的可信性。如果指令或寄存器中的数据是敏感的,这可能会导致安全冲突。因此,建议只有监控模式软件直接修改NS位。

正常世界软件无法访问SCR的内容。

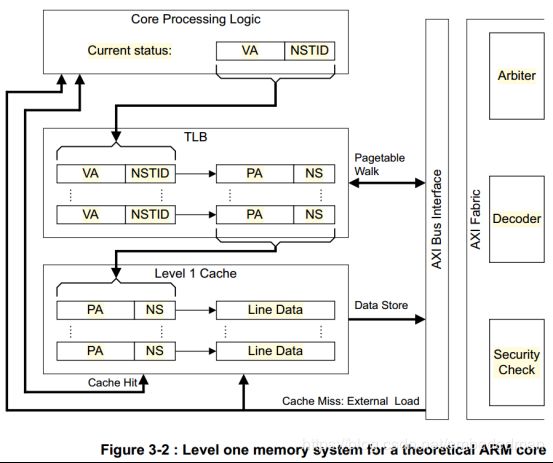

3.3.2 保护一级内存系统(Securing the level one memory system)

核心之外的内存基础设施将系统分为两个世界,并且需要在核心中应用类似的分区,以分离在一级(L1)内存系统的组件中使用和存储的数据。

存储器管理单元MMU

ARM应用级处理器中L1内存系统的主要组件是内存管理单元(MMU),它能够将运行在处理器上的软件看到的虚拟地址空间映射到存在于处理器外部的物理地址空间。地址转换使用软件控制的转换表进行管理,该表详细说明了每个虚拟地址对应的物理地址,以及有关内存访问的其他一些属性,如可缓存性和访问权限。

在具有MMU但没有安全扩展的ARM核心中,例如ARM926EJ-S™ 处理器,在任何时刻都有一个虚拟地址到物理地址的映射。特权模式代码通常重写或将硬件指向进程上下文开关上的一组新表,以提供多个独立的虚拟内存空间。

在TrustZone处理器中,硬件提供两个虚拟mmu,每个虚拟处理器一个。这使得每个世界都有一组本地转换表,使它们能够独立地控制虚拟地址到物理地址的映射。ARMv6和ARMv7 L1转换表描述符格式包括NS字段,安全虚拟处理器使用该字段来确定在访问与该表描述符相关联的物理内存位置时要使用的NS位的值。非安全虚拟处理器硬件忽略此字段,并且始终使用NS=1进行内存访问。此设计使安全虚拟处理器能够访问安全或非安全内存。为在两个世界之间实现高效的上下文切换,arm处理器会标记转换查询缓冲区(TLB)中的条目,TLB缓存了地址转换表的遍历结果,并使用执行遍历的世界的标识,这允许非安全和安全条目在TLB中共存,从而加快切换,因为无需刷新TLB条目。

注意

TLB标记中所属世界的标识的存在不受ARM体系结构的强制;它是由实现定义的。某些处理器硬件可能会在两个世界切换时刷新部分或全部TLB条目。

caches

支持缓存中两种安全状态的数据是任何高性能设计的理想特性。这消除了在世界之间切换时缓存刷新的需要,并使高性能软件能够在世界范围内进行通信。为了实现这一点,在适用的第二级和更高级别,处理器缓存被扩展为一个额外的标记位,该标记位记录访问内存的事务的安全状态。

就安全状态而言,缓存的内容是动态的。可以收回任何未锁定的缓存线,以便为新数据腾出空间,而不管其安全状态如何。安全cache line加载可以逐出非安全cache line,非安全cache line加载可以逐出安全cache line。

举例

将上述所有概念放在一起,图3-2显示了理论上ARM处理器的L1内存系统在访问内存系统时如何处理与安全扩展相关的状态。

- 核心处理逻辑尝试数据加载、数据存储或指令预取。硬件将虚拟地址(VA)和当前世界标识(非安全表标识符,或NSTID)传递给TLB,使其能够执行地址转换。

- TLB加载物理地址(PA)和与它所传递的VA和NSTID相关联的NS位,执行页表遍历,并在必要时强制NS=1(如果NSTID=1)。然后,TLB将此信息传递到缓存以执行实际的数据或指令访问。

- 缓存尝试将TLB中的PA和NS位与现有缓存线的标记相匹配。如果成功,它将从该缓存线返回数据,否则将从外部内存系统加载缓存线。

在将加密音频内容加载到普通世界媒体播放器中并在安全世界中解密的媒体应用中,安全世界软件可以在安全世界翻译表中映射包含属于媒体播放器的数据的非安全存储器。这允许安全世界直接访问包含需要解密的音频内容的非安全缓存线;这种类型的内存称为世界共享内存。因此,普通世界应用程序可以通过缓存层次结构中的任何级别将数据传递给安全世界中的伙伴任务。与要求将缓存数据从缓存中刷新并放入外部内存的解决方案相比,这使得高性能系统成为可能。

紧耦合存储器

ARM1176JZ(F)-S处理器支持紧耦合存储器(TCM),TCM是高性能的SRAM块,与L1缓存在内存层次结构中处于同一级别。根据合成时配置的TCM的总大小,每个指令和数据接口上最多有两个TCM块。软件可以将TCM的每个块配置为只进行安全访问,或只进行非安全访问,并独立控制每个块的基地址。

加速器一致端口

一些ARM处理器,如ARM Cortex-A9 MPCore处理器,包括一个可选的加速器一致端口(ACP)。ACP是处理器上的一个AXI从机接口,它允许连接到它的任何外围主机访问与处理器一致的物理内存映射。这允许外部外设访问位于ARM处理器缓存层次结构内的数据。这种技术减少了需要从ARM处理器的缓存中清除和/或失效数据的用例数量,提高了必须与外部外设(如DMA控制器)紧密共享数据的软件的性能。ARM处理器内存系统代表使用ACP的外部主机进行的内存访问的安全状态将与访问ACP的总线事务的安全状态相同。在ACP接口读取的ARPROT[1]信号的值将用于读取,而AWPROT[1]信号的值将用于写入。

AXI从机可以区分ARM处理器代表内部处理单元进行的事务和代表ACP事务进行的事务。这取决于处理器的微体系结构,且可能在所有实现中都不可用。Cortex-A9 MPcore处理器根据存储器访问的发起方设置以下AXI信号:

• ARIDMx[2]: Read transaction – low if originator is the ARM processor, high if

it is the ACP.

• AWIDMx[2]: Write transaction – low if originator is the ARM processor, high if

it is the ACP

该信号可由安全敏感从机的解码逻辑使用,以确定访问是否来自受信任的master。这项技术可以,例如,用于隐藏ARM处理器的物理内存映射的一部分,使其不被其他可以访问ACP的master看到。

注意

ACP只能像其他AXI从机一样进行安全访问。

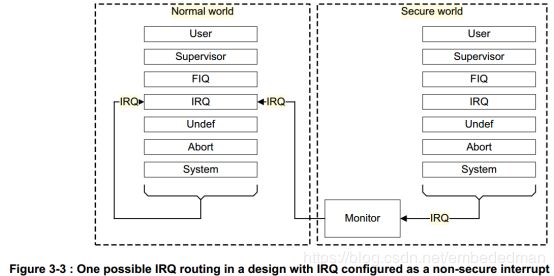

3.3.3 安全中断

能够将IRQ和FIQ直接捕获到监视模式,而无需任何世界的代码干预的能力,允许为安全中断源创建灵活的中断模型。一旦执行到达监视器模式,受信任的软件可以相应地路由中断请求。当与具有安全意识的中断控制器结合时,这允许设计提供安全的中断源,而这些中断源不能被正常世界的软件操作。

ARM推荐的模型是使用IRQ作为正常世界的中断源,FIQ作为安全世界的中断源。IRQ是大多数操作环境中最常用的中断源,因此使用FIQ作为安全中断意味着对现有软件的修改最少。如果处理器在发生中断时运行的是正确的虚拟核心,则不会切换到监视器模式,中断将在当前世界中本地处理。如果核心在另一个世界,当一个中断发生时硬件陷入到监视器模式,监控软件会导致上下文切换并跳转到恢复的世界,此时中断会被接收。

注意

建议监视器始终在屏蔽中断的情况下执行。

为了防止恶意的正常世界软件屏蔽敏感的安全世界中断,处理器硬件在CP15中包括一个配置寄存器,可用于防止任何正常世界软件修改CPSR中的F(FIQ掩码)和A(外部中止掩码)位。此控制寄存器只能由安全世界软件访问。请注意,没有选项可以阻止正常世界屏蔽IRQ中断。

处理器异常向量表

为提供上述异常行为,启用TrustZone的处理器实现了三组异常向量表。其中一个表用于正常世界,一个用于安全世界,另一个用于监视模式。

复位时安全世界异常向量表的基址与处理器输入信号VINITHI的设置一致;如果未断言,则为0x00000000;反之则为0xFFFF0000。其他表的基址未定义,应在使用前由软件设置。与前几代ARM处理器不同,每个表的位置都可以在运行时移动。这是通过在CP15中编程适当的向量基址寄存器(VBAR)来实现的。

注意

通过在CP15控制寄存器中设置V bit,可以在运行时启用或禁用高段矢量。如果设置了V bit,则无论VBAR中存储的值如何,始终从0xFFFF0000开始的表中获取处理器异常。V bit的值是banked,可以独立配置安全世界和正常世界异常向量表。

V bit仅适用于相应的安全世界和正常世界异常表,监视模式异常表始终位于监视模式向量基地址寄存器中指定的内存地址。

3.3.4 安全处理器配置

为了能够在虚拟CPU上独立地执行代码,硬件严格管理CP15中的配置选项。被视为敏感的配置选项,或全局应用于核心的配置选项,只能由安全世界软件编写,尽管大多数配置选项可以由正常世界软件读取。不具有全局敏感性并因此可以在每个世界的本地进行应用的设置,通常存储在硬件中。这使每个世界都可以独立地控制影响其实现的设置。只有安全世界才能修改的某些全局配置选项对正常世界的实现有一定影响,特别是与访问某些低级硬件有关的功能(如缓存锁定或系统协处理器)。然而,传统软件通常只需要很少或根本不需要更改即可在正常世界里执行。

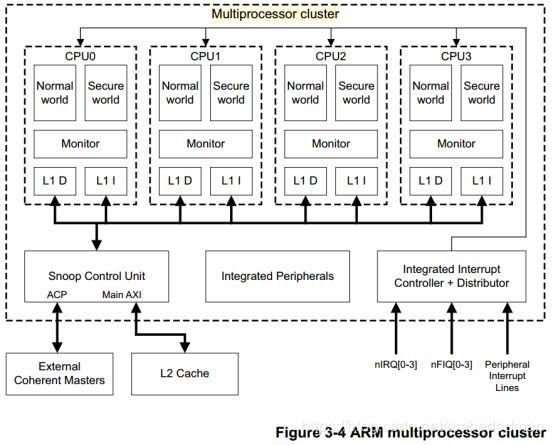

3.3.5 带安全扩展的多处理器系统

ARM体系结构包括对集群中1到4个处理器之间的多处理器设计的支持。集群中的处理器可以配置为以对称多处理(SMP)模式或非对称多处理(AMP)模式执行。

当处理器以SMP模式执行时,集群的Snoop控制单元(SCU)将透明地将跨SMP处理器共享的数据保存在L1数据缓存中。当处理器以AMP模式执行时,如果需要,执行软件必须手动保持内存一致性。

这些多处理器系统可以实现ARM安全扩展,为集群中的每个处理器提供本章前面描述的程序员模型特性。目前实现多处理器功能和安全功能的ARM处理器是Cortex-A9 MPCore处理器

注意

多处理器系统通常包括一个加速器一致性端口,它允许外部总线master访问与处理器集群相同的物理内存视图。详见第3-10页。

每处理器两个世界

多处理器集群中的每个处理器都有一个正常世界和一个安全世界。这使得一个四处理器集群总共有八个虚拟处理器,每个虚拟处理器都可以独立控制它们的MMU配置。

集群中任意数量的处理器可能在任何时间点处于安全世界中,并且处理器可以独立于集群中的其他处理器在世界之间进行转换。特定的软件实现可以选择限制安全世界软件的并发执行,以降低与复杂软件设计相关联的安全风险。

注意

在第5-13页的安全软件和多处理器系统中讨论了多处理对安全世界软件设计的潜在影响。

如第3-8页的Caches部分所述,集群中的每个缓存线都将其包含的数据的安全状态存储为其标记的一部分。这使得当集群中的处理器以SMP模式执行时,可以在L1处理器数据缓存中同时存储安全和非安全数据。一致性硬件在执行一致性操作时使用整个缓存标记,使其能够同时保持安全和非安全数据的一致性。

Snoop控制单元配置

SCU包括许多配置寄存器,它们决定SCU本身的配置,集群中每个ARM处理器的配置,以及处理器本地计时器对非安全内存事务的可访问性。

•SCU访问控制寄存器决定集群中哪些处理器可以重新编程SCU的配置寄存器。

•SCU安全访问控制寄存器确定非安全访问是否可以重新编程SCU配置寄存器或访问处理器本地计时器。

中断处理

Cortex A-profile多处理器系统包括一个集成的中断控制器,该控制器基于与PrimeCell通用中断控制器(PL390)相同的技术,如第4-6页所述。这个中断控制器提供了一个灵活的中断模型,它能够在多处理器集群中分配优先中断,打断在接收到高优先级中断时已经执行的低优先级中断处理程序。在同时实现安全扩展的多处理器系统中,此中断控制器可识别TrustZone。这允许它管理安全和非安全中断,并防止非安全的内存访问读取或修改安全中断的配置。

通过在中断安全寄存器中编程适当的位,可将由集成中断控制器管理的中断配置为安全中断。一旦中断安全,任何非安全访问都不能修改其配置。

由集成中断控制器管理的所有中断都被分配一个优先级,以确定是否允许它们打断已经由ARM处理器处理的异常。硬件确保低优先级中断将一直等到高优先级中断被清除后才发出给处理器。对优先级空间进行分区,以确保安全中断始终可以配置比非安全中断更高的优先级。为安全世界分配高优先级中断可用于防止非安全世界使用中断对安全世界执行拒绝服务攻击。

集成中断控制器可以支持本章前面描述的模型,导致它控制的安全中断生成FIQ异常,而它控制的非安全中断生成IRQ异常。在这种情况下,所有中断都由集成中断控制器管理,并且不可能从外部中断控制器直接生成中断。集成中断控制器还可以支持许多传统配置,这些配置使得FIQ和/或IRQ异常由外部中断触发器生成,完全绕过集成中断控制器。

可以独立地为FIQ和IRQ异常配置传统中断的生成:

•如果仅为FIQ异常启用传统模式,则集成控制器将其控制的安全和非安全中断路由到IRQ异常向量。

•如果仅为IRQ异常启用传统模式,则集成控制器将无法为非安全中断生成异常,安全中断将路由到FIQ异常向量。

•如果为FIQ和IRQ异常启用传统模式,则完全绕过集成中断控制器。

注意

如果在设计中使用它们,则到处理器集群的传统中断输入信号通常由一个或多个外部中断控制器生成。这些外部设备可以使用与TrustZone系统中的任何其他外部AXI或APB从属设备相同的方法进行安全保护。

3.4 调试架构

与安全扩展集成的系统基础设施的最后一部分是调试支持。ARM提供的调试解决方案分为两部分:处理器调试组件和系统调试组件。

3.4.1处理器调试控制

在引入安全扩展之前,ARM处理器包含一个调试控制信号,全局启用或禁用对处理器的调试器访问。在这些设计中,将安全敏感软件与富操作环境一起部署意味着必须全局禁用调试,否则您将面临来自简单硬件攻击的重大威胁。随着操作环境变得越来越大,越来越复杂,这开始成为一个远远不理想的情况,特别是当有大量的开发人员希望为富操作环境开发软件时。这些人通常需要在设备进入现场并启用安全软件之后调试他们的应用。TrustZone调试扩展将调试访问控制分成以下每个方面的独立可配置视图:

•安全特权入侵(JTAG)调试

•安全特权非侵入(跟踪)调试

•安全的用户侵入式调试

•安全的用户非侵入式调试

安全的特权调试访问由两个输入信号控制,分别是SPIDEN(入侵)和SPNIDEN(非入侵)。

安全用户模式调试访问由CP15寄存器中仅能通过安全特权进行访问的两个位SUIDEN(入侵)和SUNIDEN(非入侵)控制。这些设置使TrustZone处理器能够在设备部署后控制调试可见性。例如,可以提供完全正常世界的调试可见性,同时还可以阻止所有安全世界的调试。

注意

ARM处理器还包括全局调试启用输入信号:DBGEN和实现ARMv7体系结构的核心上的NIDEN。这些信号可用于禁用核心的所有调试可见性,包括正常世界的调试。

•ARMv6:DBGEN–全局侵入性和非侵入性调试启用。

•ARMv7:DBGEN–全局入侵调试启用。

•ARMv7:NIDEN–全局非侵入性调试启用。

多处理器调试控制

在实施多处理器扩展的ARM处理器中,如第3-13页带安全扩展部分的多处理器系统所述,集群中的每个处理器都提供独立的DBGEN、NIDEN、SPIDEN和SPNIDEN输入信号。这允许集群中的处理器子集以可能的方式进行调试。

注意

系统设计者必须知道,SMP数据一致性硬件可能允许启用侵入式调试的处理器修改禁用侵入式调试的处理器使用的数据。

性能分析

为了实现代码的低级基准测试,ARMV6和ARMV7应用级处理器在CP15中包含一个性能监视器。此硬件单元可用于定时代码执行和统计运行时可能发生的处理器事件,如缓存线回收。为了防止在针对安全世界软件的攻击中使用性能监视器,可以使用安全CP15配置选项来防止正常世界和用户模式访问这些计数器。

调试控制

ARM系统调试解决方案是ARM Coresight™片上调试和跟踪技术。它为整个SOC提供了调试和跟踪解决方案,支持对多个处理器和其他系统组件进行调试。可以从设备外工具和设备内组件访问Coresight调试基础结构。

Coresight可供SOC硬件和软件访问的基础设施部分以APB外设形式实现。为了减少所需组件的数量,Coresight外围设备的设计不使用由AXI到APB桥接器提供的标准每外围设备保护机制;Coresight组件应可供非安全内存事务访问。

作为AXI-to-APB桥接器提供保护的替代方案,Coresight组件包括许多用于启用或禁用安全调试的控制信号。这些信号被称为Coresight身份验证接口,包括SPIDEN、SPNIDEN和DBGEN信号,这些信号与为处理器核心描述的相同名称的信号具有类似的作用。

如果外部调试硬件或目标板上的正常世界软件试图在SPIDEN解除断言时在安全地址上设置系统断点,CoreSight硬件将无法创建断点。对于检测解决方案,如果未断言SPNIDEN,外围设备将简单地丢弃安全跟踪信息。

注意

调试安全体系框架的一个结果是,当SPIDEN或SPNIDEN被断言时,正常世界的软件可以直接影响或监视系统中的安全世界执行。因此,只有当设备位于受信任的环境中时,才应启用安全调试。

第四章 TrustZone硬件库

本章概述了ARM提供的启用TrustZone的IP。

本章包括以下部分:

•第4-2页上的系统IP

•处理器IP,第4-8页

•第4-11页AMBA2 AHB IP的再利用

4.1系统IP

本节概述了ARM提供的一些系统IP,ARM内置了对安全扩展的支持。

注意

如果使用适当的AXI-to-APB桥接器,则可以使用安全扩展来保护任何APB外围设备。

4.1.1 PrimeCell® High-Performance Matrix - PL301

实现系统范围隔离的主要组件是AMBA3-AXI兼容总线矩阵,它将所有系统组件连接在一起。ARM在PrimeCell高性能矩阵产品PL301中提供了这一功能。

为了支持对现代SoC基础设施的需求,AXI总线生成器由一系列支持组件组成。用于定时隔离的寄存器片、用于将总线宽度减小到低带宽SoC区域的宽度缩放缩小器以及用于链接时钟域的同步或异步网桥都是可用的:

•PrimeCell Infrastructure AMB3 AXI寄存器片-BP130

•PrimeCell Infrastructure AMBA3 AXI降压器-BP131

•PrimeCell Infrastructure AMBA3 AXI到AXI桥-BP132-4

•PrimeCell Infrastructure AMBA3 AXI to APB Bridge - BP135

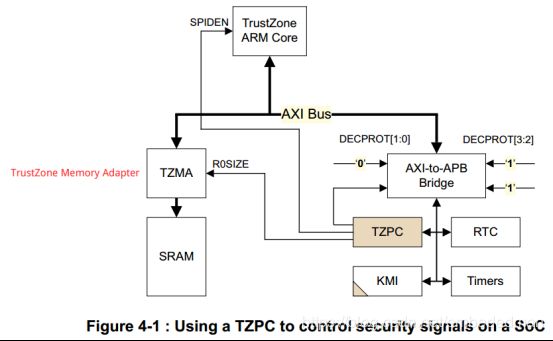

在典型的ARM系统中,大多数外围设备都连接到APB总线。APB是一种比主AXI总线更简单、功耗更低的总线。APB协议不携带与总线事务的TrustZone安全状态相关的位。这使得现有的外围设备设计可以在AMBA3 APB总线上使用,并将管理安全状态的责任放在AXI-to-APB桥上,该桥提供高速AXI域和低功耗APB域之间的接口。每个AXI-to-APB网桥提供一个AXI从机接口,并可在其本地APB总线上为多达16个外设进行中介访问。网桥包含基于传入的AXI事务生成APB外围选择的地址解码逻辑。桥接器包括总线上每个外围设备的单个TZPCDECPROT输入信号。此信号用于确定外设配置为安全还是非安全;网桥将拒绝非安全事务以保护外设地址范围。

这些桥输入信号可以在合成时持续绑定,也可以通过可信外围设备(如TrustZone保护控制器(TZPC))动态控制,以允许在运行时动态切换安全状态。

图4-1显示了控制4个外围设备的AXI到APB桥。TZPC配置为始终安全,计时器和实时时钟(RTC)配置为始终不安全,键盘和鼠标接口(KMI)在软件控制下具有可编程安全状态。安全世界软件可以在运行时对TZPC进行编程,将输入到AXI到APB桥的信号更改为将KMI从Secure切换到Non Secure或反之。

注意

图中的阴影块表示安全外围设备,带阴影角的块表示可以从安全切换到非安全的外围设备。

这种设计允许外设在正常世界中存在大部分时间,但允许它们在短时间内暂时切换到安全世界。KMI外设就是一个很好的例子;它通常被用作通用的普通世界键盘,但可能会被切换成一个短时间的安全输入设备,以允许在安全的环境中输入用户密码。如图所示,TZPC的加入允许动态控制SoC上的其他信号,例如ARM核心的SPIDEN调试控制输入。

AXI到AHB和AHB到AXI桥允许实现了AMBA3和AMBA2规范的两个子系统连接在一起。每个通信方向都需要一个单独的网桥;AXI-to-AHB网桥允许AXI事务在AHB总线上主控,AHB-to-AXI网桥允许AHB事务在AXI总线上主控。

AHB总线不提供任何机制来承载通过它的内存事务的安全状态,因此所有的安全实现都必须在网桥本身中进行管理。

•AXI-to-AHB网桥允许将整个AHB从机域设置为安全或非安全。

•AHB-to-AXI网桥允许整个AHB主机域变得安全或不安全。

如果设计需要安全和非安全AHB主设备和从设备的混合,建议不要将安全组件和非安全组件放在同一个网桥后面。

注意

AHB域内的安全完全由AHB配置管理,不在安全扩展的范围内。

4.1.2 PrimeCell Level 2 Cache Controller - PL310

随着处理器时钟频率的增加,越来越希望在核心和外部存储系统之间包含一个2级缓存。这减少了由于外部内存的访问延迟而导致的处理器管道暂停次数,在某些应用程序中实现显著更快的性能,并通常降低功耗。TrustZone系统中的每个缓存都需要用它所包含的数据的安全状态来标记每个缓存线,从而能够同时存储来自两个世界的数据。ARM1176JZ(F)-S处理器和Cortex-A9处理器可以使用单独的二级缓存控制器,该控制器必须实现对安全状态的适当标记。ARM高性能PrimeCell 2级缓存控制器可用于此目的。

注意

Cortex-A8处理器包括一个集成的二级缓存控制器。

4.1.3 PrimeCell DMA Controller - PL330

使用处理器在系统中移动数据可能是对功耗和处理器执行时间的低效利用。由于这个原因,许多系统包括一个直接内存访问控制器(DMAC),它是一个专用的引擎,用于在物理内存系统周围移动数据。

PrimeCell DMA控制器是一个多通道AXI引擎,带有一个微编码的作业描述,以支持复杂结构的传输。DMAC可以支持并发安全和非安全通道,每个通道都有独立的中断事件,并由专用的APB接口控制。试图对安全内存发起DMA传输的非安全事务将导致DMA传输失败。

4.1.4 PrimeCell TrustZone地址空间控制器 - PL380

TrustZone地址空间控制器(TZASC)是一个AXI组件,它将从机地址范围划分为多个内存区域。TZASC可通过安全软件编程,将这些区域配置为安全或非安全,并将拒绝对配置为安全的内存区域的非安全事务。

在综合设计时,可以配置内存区域的数量和TZASC-AXI接口的总线宽度。

使用TZASC的主要原因是将单个AXI从机(如SoC片外DRAM)划分为多个安全域。SoC片外RAM是一个很好的例子,存储器设备由于额外的pin输出、印刷电路板面积和存储器本身的成本而具有显著的相关成本。因此,系统需要对单个外部存储器进行分区,以便它可以同时包含安全区域和非安全区域;这通常比放置两个较小的存储器设备要便宜。

ARM AXI动态内存控制器(DMC)系列是一组内部不支持创建安全分区和非安全分区的高性能控制器。为了创建安全分区,可以在DMC和需要访问它的SoC主机之间放置一个TZASC。TZASC设计用于动态内存,允许突发访问以最小的内存延迟影响通过它。

注意

TZASC只能用于对内存映射设备进行分区;特别是不能用于对基于块的设备如NAND flash进行分区。

4.1.5 PrimeCell Infrastructure AMBA3 AXI TrustZone内存适配器 - BP141

TrustZone存储器适配器(TZMA)使设计能够保护片上静态存储器(例如ROM或SRAM)中的区域。与为每个世界提供单独的专用存储器相比,放置单个大型存储器设备并将其划分为安全和非安全区域的成本通常更低。TZMA允许将一个高达2MB的静态存储器分成两个区域,其中下部是安全的,上部是不安全的。

安全区域和非安全区域之间的分区的位置始终是4KB的倍数,并通过TZMA的R0SIZE输入信号进行控制。这些信号可以通过将信号连接到从TZPC外围设备输出的TZPCR0SIZE来动态配置,或者可以在合成时被绑定以固定方式分割存储器。

TZMA不能用于划分动态存储器或需要多个安全区域的存储器;对于这些设计,必须使用TZASC。

4.1.6 PrimeCell通用中断控制器-PL390

为了支持安全和非安全中断的健壮管理,底层中断控制器必须防止正常世界修改安全世界中断源的配置。这意味着一个中断控制器必须支持使用内部分区的TrustZone技术,或者必须在系统中放置两个中断控制器。

通用中断控制器(GIC)是支持安全和非安全优先级中断源的单一硬件设备。正常世界软件修改已设置为安全的中断源配置的尝试将被GIC硬件阻止。此外,非安全软件只能在优先级范围的下半部分配置中断,以防止拒绝服务攻击。

注意

ARM Cortex-A9MPCore集成了自己的中断控制器,与GIC具有相同的程序员模型,因此不需要外部中断控制器。有关集成中断控制器的更多详细信息,请参阅第3-15页的“中断处理”部分。

4.1.7 PrimeCell Infrastructure AMBA3 TrustZone 保护控制器 - BP147

如AXI-to-APB桥接部分所述,TrustZone保护控制器(TZPC)是一个可配置的信号控制模块,可放置在APB总线上,以向SoC上的其他组件提供控制信号。TZPC包括三个通用寄存器TZPCDECPROT{2:0},每个寄存器可以控制SoC中的8个信号。它还包括一个寄存器TZPCR0SIZE,可以用来为TrustZone内存适配器提供分区位置控制信号。TZPC的通电状态是将所有TZPCDECROT寄存器位设置为0(安全),将TZPCR0SIZE寄存器设置为0x200(使TZMA支持的整个2MB内存范围安全)。启动代码可以放松安全设置,使组件在需要时不安全。

4.2 Processor IP

有许多处理器实现了AMBA3 AXI内存接口,但并非所有处理器都实现相同的功能集。本节概述这些处理器的主要功能,以及它们在TrustZone系统中的使用方式。本节还介绍了ARM SecurCore系列智能卡处理器,它可以与启用TrustZone的SoC一起使用,以提供更高级别的物理安全性。

4.2.1 ARM1176JZ(F)-S处理器

ARM1176JZ(F)-S处理器是第一个TrustZone处理器。它实现了ARMv6Z体系结构,并使用ARM Artisan®Metro标准单元库提供了一个8级单发整型管道,在90nm制程中能够达到320MHz。当用这种硅工艺实现时,它消耗1平方毫米的模具面积,不包括缓存。

与TrustZone系统设计相关的功能:

•可选的紧耦合存储器(TCMs)

•可选外部2级缓存控制器(PL310)

4.2.2 Cortex-A8处理器

Cortex-A8处理器是第一款ARMV7 A-profile处理器。它实现一个13级双发整型管道和一个额外的10级NEON媒体SIMD管道。它能够使用ARM Artisan®Advantage库在65nm LP工艺中达到650MHz,消耗的模具面积小于3平方毫米,不包括NEON和高速缓存RAM。

与TrustZone系统设计相关的功能:

•没有TCMs

•集成2级缓存控制器。

4.2.3 Cortex-A9处理器和Cortex-A9 MPCore处理器

Cortex-A9是一款ARMV7 A-profile处理器,可作为单核和1-4路多核实现。它使用可选的向量浮点(VFP)或NEON管道实现无序、多发的超标量管道。

与TrustZone系统设计相关的功能:

•第一个实现ARM安全扩展的多处理器平台,在四核设计中总共提供八个虚拟处理器

•没有TCMs

•设计用于PrimeCell 2级缓存控制器(PL310)

设计用于通用中断控制器(PL390)。这只是对Cortex-A9的单处理器变体的一个要求;多处理器MPCore版本包括一个内置的中断控制器。

4.2.4 ARM1156T2(F)-S™ 处理器

ARM1156T2(F)-S处理器是一款ARMv6处理器,带有内存保护单元(MPU),专为嵌入式应用设计。该处理器本身并没有实现安全扩展,但它实现了一个AMBA3-AXI总线接口,使得它可以直接放置在一个支持TrustZone的SoC设计中,而无需额外的逻辑或桥。

在大多数设计中,ARM1156T2(F)-S将被静态绑定以生成安全内存事务或非安全内存事务,从而使ARM1156T2(F)-S作为非对称处理引擎与主应用处理器一起作为安全世界的一部分,或作为正常世界的一部分。

4.2.5 Cortex-R4处理器

Cortex-R4处理器是用于嵌入式应用的ARMV7 R配置处理器。与ARM1156T2(F)-S处理器类似,Cortex-R4处理器没有实现安全扩展,但它实现了一个AMBA3 AXI总线接口,使得它能够直接放置在一个支持TrustZone的SoC设计中,而无需额外的逻辑或桥。

4.2.6 SecurCore智能卡处理器

ARM SecurCore系列提供了一系列处理器IP,设计用于智能卡和防篡改集成电路部署。对于需要比TrustZone系统更高物理安全级别的安全应用,可以将基于SecurCore的智能卡与TrustZone系统一起使用。TrustZone系统可以提供智能卡无法提供的功能,例如安全的用户界面和能够处理高性能、不太敏感的安全任务的软件。

处理器功能摘要:

•SC100:支持ARM和Thumb®指令集

•SC200:支持ARM和Thumb指令集并集成Jazelle™加速JavaCard2.x应用技术

•SC300:基于Cortex™ -M3,SC300支持多种技术,包括Thumb®-2指令集,以减少内存需求和提高软件性能。

注:

Jazelle是ARM体系结构的一种相关技术,用于在处理器指令层次对JAVA加速

4.3 AMBA2 AHB IP的再利用

系统设计者可能需要在同时使用AMBA3和安全扩展的设计中重用传统AMBA2 AHB主设备和从设备。这些传统设备可以包括诸如DMA控制器的非处理器master设备和包括诸如ARM926EJ-S处理器这样的master设备的复杂子系统。

4.3.1 AHB masters的再利用

在这些设计中,任何AHB主机必须通过AHB-to-AXI网桥传递其事务来连接到AXI域,如第4-4页所述。这些网桥基于网桥配置信号实现AXI NS比特的简单映射。这允许从AXI域的角度将桥后面的整个AHB域设置为安全或非安全。

如果只需要单个网桥后面的AHB主机的一个子集作为AXI域中的安全主机可用,则需要额外的自定义逻辑来基于AHB主机ID生成决定NS位的网桥配置输入。

注意

每个AHB主机只能直接寻址4GB的物理内存。不可能在一个AHB主机的内存映射中寻址完整的8GB安全和非安全物理地址空间。

4.3.2 AHB slaves的再利用

ARM建议使用单独的AHB总线来包含安全和非安全的AHB slaves。这允许使用AXI-to-AHB网桥提供的单个NS位控制信号;网桥将拒绝具有无效安全权限的任何事务。

在不可能这样做的情况下,可以在AXI-to-AHB桥之前放置一个TrustZone地址空间控制器,从而能够对NS位执行基于地址的检查。

第五章 TrustZone软件架构

本章介绍一些可能使用ARM安全扩展的软件体系结构。

本章包括以下部分:

•第5-2页上的软件概述

•在第5-5页启动安全系统

•监控模式软件,第5-9页

•第5-13页上的安全软件和多处理器系统

•第5-16页上的TrustZone API

5.1软件概述

在SoC硬件中实现一个安全世界需要一些安全软件在其中运行并利用存储在其中的敏感资源。安全扩展是ARM体系结构的一个开放组件,因此任何开发人员都可以创建一个自定义的安全世界软件环境来满足他们的需求。本节介绍了软件架构师在设计安全世界软件堆栈时可能要考虑的一些可能性。

注意

这里列出的每个软件选项都对安全世界硬件提出了不同的要求。例如,一个具有独立的先发制人安全世界操作系统的设计将需要一个安全计时器和一个安全意识中断控制器。

5.1.1安全世界处理资源

软件架构的总体结构将受到可用安全世界处理资源性质的严重影响。系统可以提供启用TrustZone的核心,例如ARM1176JZ(F)-S处理器,或者可以为安全世界提供专用处理器,例如Cortex-R4处理器。双物理处理器设计是一种经典的嵌入式设计,不受安全扩展的影响。运行在安全世界处理器上的软件必须是自包含的,并提供自己的本地操作环境。预计大多数设计将选择使用启用TrustZone的处理器。这通常会给安全世界带来更高的软件性能,并且比专用安全处理器需要更少的硅面积。在本章的剩余部分,我们将重点讨论这个案例。

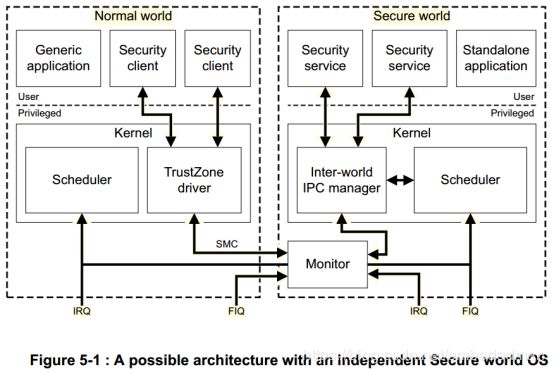

5.1.2软件架构

在启用TrustZone的处理器核心上,有许多可能的软件体系结构是安全世界软件堆栈可以实现的。最复杂的是一个专用的安全世界操作系统;最简单的是放置在安全世界中的同步代码库。在这两个极端之间有许多中间选择。

安全操作系统

安全世界中的专用操作系统是一个复杂但功能强大的设计。它可以模拟多个独立的安全世界应用的并发执行,新安全应用的运行时下载以及完全独立于正常世界环境的安全世界任务。

这些设计中最极端的版本与软件堆栈非常相似,在一个具有两个独立物理处理器的非对称多处理器(AMP)配置的SoC中可以看到这些软件堆栈。每个虚拟处理器上运行的软件是一个独立的操作系统,每个世界都使用硬件中断来抢占当前运行的世界并获取处理器时间。一个紧密集成的设计,它使用一个通信协议,将安全世界任务与请求它们的正常世界线程相关联,可以提供对称多处理(SMP)设计的许多好处。例如,在这些设计中,安全世界应用可以继承它正在协助的正常世界任务的优先级。这将为媒体应用程序提供某种形式的软实时响应。

基于操作系统原理的设计的优点之一是使用处理器MMU将安全的世界内存空间分成多个用户空间沙箱。只要安全世界内核软件得到正确实现,来自独立涉众的安全任务就可以同时执行,而无需相互信任。内核设计可以加强安全任务之间的逻辑隔离,防止一个安全任务篡改另一个安全任务的内存空间。

同步库

许多用例不需要安全世界操作系统的复杂性。在安全世界中,一个简单的代码库可以一次处理一个任务,对于许多应用来说已经足够了。这个代码库完全是使用来自普通世界操作系统的软件调用进行调度和管理的。这些系统中的安全世界是正常世界的slave,不能独立运行,但因此复杂程度要低得多。

中间选项

在这两个极端之间有一系列的选择。例如,安全世界多任务操作系统可以被设计为没有专用中断源,因此可以由正常世界提供虚拟中断。如果正常世界操作系统停止提供虚拟中断,此设计将容易受到拒绝服务攻击,但在许多情况下,这种攻击没什么问题。或者,MMU可以用于静态地分离另一个同步安全世界库的不同组件。

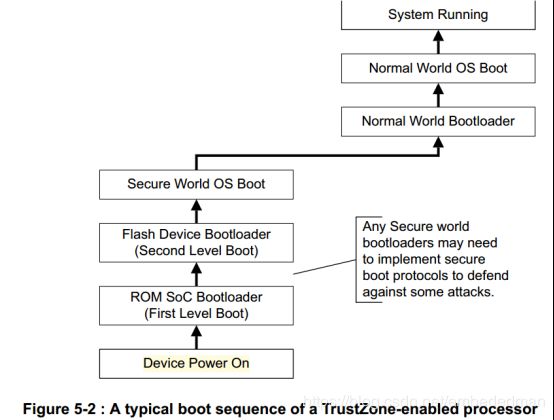

安全系统生命周期中的一个关键点是启动时。许多攻击者试图在设备关机时破坏软件,执行攻击,例如,用已被篡改的镜像替换flash中的安全世界软件镜像。如果系统从flash启动镜像而没有首先检查其真实性,则系统易受攻击。

这里应用的原则之一是为所有安全世界软件和潜在的正常世界软件生成一个信任链,该信任链是从不易被篡改的信任根建立的。这就是所谓的安全引导序列。参见第5-6页的安全引导。

开机时启用TrustZone的处理器在安全环境中启动。这使得任何敏感的安全检查都能在普通软件有机会修改系统的任何方面之前运行。

开机后,大多数SoC设计将开始执行基于ROM的引导加载程序,该程序负责初始化关键外围设备(如内存控制器),然后切换到位于外部非易失性存储器(如闪存)中的设备引导加载程序。然后,引导序列将经过安全世界操作环境初始化阶段,然后将控制权传递给正常世界引导加载程序。这将进展到启动正常的操作系统,此时系统可以被视为正在运行。

系统控制协处理器锁定

需要额外保护级别的系统可以使用输入到处理器核心的信号来锁定CP15中一些关键的安全世界配置选项。断言处理器输入信号CP15SDISABLE将导致某些安全世界CP15设置变得不可修改,即使安全世界特权软件尝试修改。

可以预期使用CP15SDISABLE的设计将在引导过程中配置敏感设置,并在将控制权传递给普通软件之前断言信号。

注意系统启动时必须将CP15SDISABLE设置为低,以启用安全世界启动代码来配置CP15寄存器将进行相应的设置。用于改变信号的方法应仅对安全世界可用,并且其他保护可能适用,例如使用只能通过设备复位重置为低状态的锁存信号发生器。

5.2.2 安全启动

安全启动方案将加密检查添加到安全世界启动进程的每个阶段。此过程旨在维护执行的所有安全世界软件映像的完整性,防止任何未经授权或恶意修改的软件运行。

密码签名协议

最符合逻辑的密码协议是基于公钥签名算法的协议,如RSA-PSS(Rivest、Shamir和Adleman-概率签名方案)。在这些协议中,受信任的供应商使用他们的私钥(PrK)生成要部署的代码的签名,并将其与软件二进制文件一起推送到设备上。设备包含供应商的公钥(PuK),该公钥可用于验证二进制文件是否未被修改,以及该二进制文件是否由相关的受信任供应商提供。

PuK不需要保密,但它确实需要以某种方式存储在设备中,这意味着它不能被属于攻击者的PuK替换。

信任链

安全启动过程实现一条信任链。从一个隐式可信组件开始,在执行之前,可以对每个其他组件进行身份验证。链的所有权在每个阶段都可能发生变化-属于设备OEM的PuK可能用于验证第一个引导加载程序,但安全世界操作系统二进制文件可能包含用于验证其加载的应用的辅助PuK。

除非一个设计可以屏蔽硬件shack攻击,否则安全引导过程的基础,即所谓的信任根,必须位于SoC片内ROM中。SoC片内ROM是系统中唯一不能被简单的重新编程攻击轻易修改或替换的组件。

为信任根存储PuK可能会有问题;将其嵌入到SoC片内ROM中意味着所有设备都使用相同的PuK,这使得一旦PrK被盗或成功反向工程他们容易受到类突破攻击。SoC片内一次性可编程(OTP)硬件(如多晶硅保险丝)可用于在器件制造期间在每个SoC中存储唯一值。这使得许多不同的PuK值可以存储在一类设备中,从而降低了类突破攻击的风险。

注意

OTP存储器可以消耗相当大的硅面积,因此可用的位数通常是有限的。一个RSA PuK的长度超过1024位,通常太大,无法放入可用的OTP存储。但是,由于PuK不是机密的,因此可以将其存储在SoC片外存储器中,前提是PuK的密码散列被存储在Soc片内OTP中。散列比PuK本身小得多(SHA256散列为256位),可用于在运行时验证PuK的值。

片内安全世界或片外安全世界

最简单的防御shack攻击的方法是将任何安全世界资源的执行放在SoC片内内存位置。如果代码和数据从未暴露在SoC封装之外,则很难窥探或修改数据值;对SoC封装的物理攻击比将逻辑探针连接到PCB track或封装管脚要困难得多。

安全启动代码通常负责将代码加载到SoC片内内存中,正确排序身份验证以避免为攻击者引入机会窗口至关重要。假设正在运行的代码和所需的加密散列已经在SoC片内内存中处于安全状态,则在使用加密方法进行身份验证之前,应将正在验证的二进制或PuK复制到安全位置。先对镜像进行身份验证,然后将其复制到安全内存位置的设计可能会受到攻击。攻击者可以在检查完成和复制发生之间的短窗口中修改镜像(先拷贝再验证比先验证再拷贝安全可靠)。

5.3监控模式软件

监控模式软件在设计中的作用是提供一个健壮的网关守卫,管理安全和非安全处理器状态之间的切换。在大多数设计中,它的功能将类似于传统的操作系统上下文切换,确保安全地保存处理器正在离开的世界的状态,并正确地恢复处理器正在切换到的世界的状态。

从正常世界进入监控模式是受到严格控制的。只有通过以下异常才能实现:中断、外部中止或通过SMC指令的显式调用。进入监控模式的安全世界入口稍微灵活一些,除了正常世界可用的异常机制外,还可以通过直接写入CPSR来实现。

监视器是一个安全关键组件,因为它提供了两个世界之间的接口。出于稳健性的原因,建议在禁用中断的情况下执行监视器代码;编写可重入监视器将增加复杂性,并且不太可能比更简单的设计提供显著的好处。

5.3.1上下文切换

如前所述,监视器的主要角色是上下文切换两个世界都需要的资源。监视器保存的任何安全状态都应该保存在安全内存的某个区域中,这样正常世界就不会对其进行篡改。

每次切换到底需要保存和恢复什么取决于硬件设计,以及用于世界间通信的软件模型。通常包括:

•所有ARM通用寄存器。

•任何协处理器寄存器,如NEON或VFP。

注意。只有在两个世界都使用协处理器时才需要。

•CP15中任何依赖于世界的处理器配置状态。

硬件异常:IRQ、FIQ、外部中止

当处理器硬件配置为捕获异常(IRQ、FIQ和外部中止)以进行监视时,中断上下文的状态是任意的。

这意味着需要对所有状态进行完全上下文切换,除非有些状态可以进行惰性上下文切换。有关更多详细信息,请参阅第5-10页的Lazy context switching。

软件异常SMC

在许多情况下,一个设计将使用SMC指令作为一个简单的inter-world yield,这将导致一个完整的上下文切换,其方式与上面描述的硬件异常类似。然而,在某些情况下,SMC驱动的世界切换在一些处理器寄存器中携带消息有效负载是有益的。在这种情况下,不需要完全的上下文切换。

使用SMC发起的上下文切换和世界共享内存,可以在两个世界之间建立有效的软件通信协议。

惰性上下文切换

一些连接到ARM协处理器接口的硬件协处理器,例如ARM VFP和NEON执行单元,可以支持一种称为惰性上下文切换的机制。这允许仅在必要时保存协处理器的上下文,而不是在每次操作系统上下文切换或TrustZone世界切换时都保存。与VFP和NEON单元相关联的状态可能相当大,所以惰性上下文切换可以显著降低平均切换开销。

为了在TrustZone系统中实现惰性上下文切换,安全世界可以使用CP15非安全访问控制寄存器(NSACR)中的位设置阻止对每个协处理器接口的正常世界访问。当正常世界或用户模式软件尝试使用已经在NSACR中配置为安全的协处理器时,将引发未定义的指令异常。异常必须被普通内核捕获,并且处理程序必须向监视器发出SMC以请求所需的协处理器上下文切换。一旦交换了协处理器上下文,monitor可以使用NSACR配置让非安全软件访问协处理器,并返回到正常世界的处理程序。

注意

许多安全世界的实现不需要浮点或SIMD操作。在安全世界不使用协处理器的设计中,系统引导代码可以使非安全软件访问所有协处理器。在这些情况下,协处理器中没有敏感数据,监视器代码不需要上下文切换它们的状态。

5.3.2中断模型-监视器要求

在第3-11页的安全中断中概述的中断模型中,IRQ被配置为正常世界中断,而FIQ被配置为安全世界中断,需要通过世界切换由监控软件进行一些核心配置。该模型提出,当发生中断时,如果处理器已经在正确的世界中执行,则硬件不会陷入到监视器模式并直接跳到本地世界的向量表。这避免了切换到监视器的开销,并使监视器软件设计更简单。

注意

在将异常捕获到监视器的设计中,您将陷入到监视器模式向量表中的相应条目;但是核心将处于监视器模式,而不是相应的异常模式。

CP15中的安全配置寄存器(SCR)包含了用于决定是否将IRQ、FIQ或外部中断捕获到监视器硬件的设置。为了实现本文提出的模型,监视器需要在每次进行世界切换时修改SCR的内容。切换到正常世界时,必须清除SCR IRQ位,并设置SCR FIQ位。切换到安全世界时,必须设置SCR IRQ位,并且必须清除SCR FIQ位。

注意

这只是在TrustZone处理器中使用中断的许多可能模型之一。

5.3.3中断延迟影响

在任何需要切换世界来处理中断的设计中,监视器都会成为定义系统最坏情况下中断延迟的关键路径的一部分。与ARM R-profile和M-profile处理器(通常部署在深度嵌入式系统中)不同,部署到ARM A-profile应用处理器上的软件通常不需要低中断延迟。然而,设计应该考虑到监视器软件引入的任何额外延迟,以确保最坏情况下的行为不会导致违反任何时间限制。

监视器模式增加的中断开销可能比单个世界中的中断上下文切换的成本要高。例如,如果处理器在发生中断时刚刚进入监视器,它将在处理中断之前通过监视器进行转换,如果处理器需要切换回另一个世界来处理中断,它将需要执行第二次监视器转换。

在希望将中断延迟影响最小化的设计中,监视器使用的代码和数据应该放在靠近核心的快速内存中。在使用ARM1176JZ(F)-S处理器的系统中,监视器可以放在TCM中。在不提供TCM的系统中,监视器可以放在锁定的二级缓存线中,也可以放在SoC片内SRAM上

中断延迟增加示例

一个简单的监视器模式压栈通用寄存器并执行本节前面描述的中断模型所需的SCR再配置可能会产生以下开销:

•ARM1176JZ(F)-S:

-监控位于TCM中的代码和数据。

-上限是每次切换200个时钟周期,或总共400个时钟周期。

-300兆赫时400个时钟周期为1.3 us。

•Cotex-A8:

-监控位于锁定的二级缓存中的代码和数据。

-每次切换的开销大约为1200个时钟周期,或者总共2400个时钟周期。

-600MHz下2400个周期为4us。

注意

总中断延迟将包括由正常世界软件、安全世界软件和系统设计方面(如外部存储器性能)引起的开销。这些间接开销未在本表中的数字中说明。

相比之下,运行在具有二级缓存且没有任何安全世界软件的ARM1176JZ(F)-S上的linux驱动看到的中断延迟大约是5000个时钟周期。这是由操作系统本身的开销引起的。

5.4安全软件和多处理器系统

一些希望利用安全执行环境的设计可能基于ARM多处理器设计,例如Cortex-A9 MPCore处理器。这些系统通过在多个硬件处理器上并发执行线程来实现更高的软件性能,这使得它们非常适合处理密集型任务,如软件媒体编解码器处理。

安全世界软件架构师需要做一个重要的决定-安全世界软件将如何利用多个处理器?

大多数安全系统的目标是使用简单的软件设计,因为简单意味着暴露安全漏洞的软件错误风险较小。真正的多线程增加了一层软件的复杂性,由于它引入了时间敏感性,因此通常很难测试。因此,许多安全世界软件实现可以选择实现一个单处理器安全世界,它很少或根本不使用SMP处理器特性,即使正常世界使用完全的SMP模式运行。

5.4.1安全世界处理器亲和力

如果选择实现一个不具备多处理能力的安全世界,则设计需要能够在支持SMP的正常世界和不支持SMP的安全世界之间进行同步通信。

一个设计可能会选择将安全世界的执行固定在一个特定的处理器上,这使得安全中断路由变得简单,但也意味着安全世界可能会降低正常世界线程调度的效率,因为它使用的是正常世界不易实现负载均衡的处理器时间。在这种设计中,与安全世界通信的正常世界驱动程序通常需要使用处理器间通信将使用安全世界的请求路由到正确的处理器。此外,安全世界不使用的处理器上的监控软件必须防止正常世界导致恶意的世界切换。该体系结构如第5-14页图5-3所示,其中安全世界软件仅使用CPU0。另一种设计可以选择让安全世界围绕系统中的多个处理器迁移,从而限制它,使它在任何单个时间点仅在一个处理器上执行。这使得安全世界变得更加高效,因为它可以与使用它的正常世界应用程序在同一个处理器上运行,并允许正常世界平衡其调度的负载,但这使得安全中断到必要处理器的路由更加复杂。

5.4.2安全世界中断的使用

在决定了安全世界将如何使用SMP处理器之后,开发人员必须选择如何将任何安全中断源集成到设计中。

在一个在单个固定处理器上执行安全世界的体系结构中,中断路由是直接的。每处理器中断控制器的处理器接口控制寄存器必须被适当地配置从而使得安全中断可以引发FIQ或IRQ异常,这取决于软件如何设计利用硬件功能。

多处理器系统中单个处理器的中断路由模型在第5-10页的中断模型-监视器要求中有更详细的描述。如该部分所示,必须处理安全或非安全中断的处理器的监控软件需要能够将它们路由到适当的世界,以便由正确的异常处理程序处理它们。

在一个SMP系统中,安全世界在集群内的一个固定的单处理器上执行,FIQ中断可供不运行安全世界软件的处理器上的非安全中断使用。为了防止硬件将这些中断路由到安全世界,在这些处理器上执行的安全引导加载程序或监视器软件必须确保CP15中的安全配置寄存器已正确编程。

注意

在安全世界只在一个处理器上执行的设计中,通常需要运行在其他处理器上的监控软件拒绝正常世界尝试使用SMC指令、中断或外部中止进行世界切换。

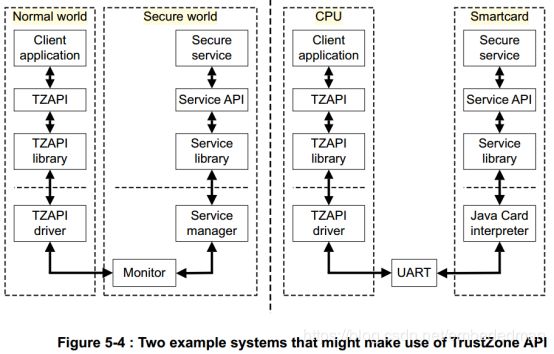

5.5 The TrustZone API

为了鼓励安全解决方案的开发,ARM开发了一个标准化的软件API,称为TrustZone API(TZAPI),它定义了一个软件接口,在富操作环境中运行的客户端应用可以使用该接口与安全环境交互。

该API主要是一个通信API,使客户端能够向安全服务发送命令请求,并使客户端能够有效地与所连接的服务交换数据。此通信接口旨在支持世界共享内存的原则,以实现高性能的大容量数据传输。

API的辅助功能允许普通客户端应用通过安全服务进行身份验证,查询已安装服务的属性,并允许受信任的普通客户端代码执行新安全服务的运行时下载。

注意

通信API支持同步和可选的异步调用约定,以支持在嵌入式设备上所有常见的正常操作系统。

尽管TrustZone API的目标是使用启用TrustZone的系统处理器,并试图利用可用的硬件功能,如世界共享内存,它被设计为可移植到几乎任何安全环境的实现。使用在智能卡上运行的可扩展安全框架的系统也将是TrustZone API实现的合适候选对象。在这些非TrustZone系统中,TZAPI世界共享内存结构的实现可能需要一个副本,但它们仍然应该是可移植的。

5.5.1 API可用性

ARM认识到,由于缺乏软件开发的共同标准,安全软件生态系统的开发受到了阻碍,因此它发布了TrustZone API作为公共规范,任何软件开发人员都可以免费下载和使用它作为其底层安全解决方案的接口。

TrustZone API可以从ARM网站免费下载。见有关详细信息,请访问:

http://www.arm.com/TrustZone。

第六章 TrustZone系统设计

略

第七章 设计checklists

略