数字ic知识点总结

目录

参考文章

问题:

时序逻辑电路分析

乒乓buffer

触发器

建立时间和保持时间(这个图画的很详细)

verilog 实现任意分频

计算机体系结构——流水线技术(Pipelining)

敏感列表

数字ic设计流程

长沟道器件电压和电流的关系

亚稳态

DMA(直接内存访问)

FIFO

Verilog整理笔记之SRAM篇

RAM家族

HDL语言的层次概念

verilog 关键字

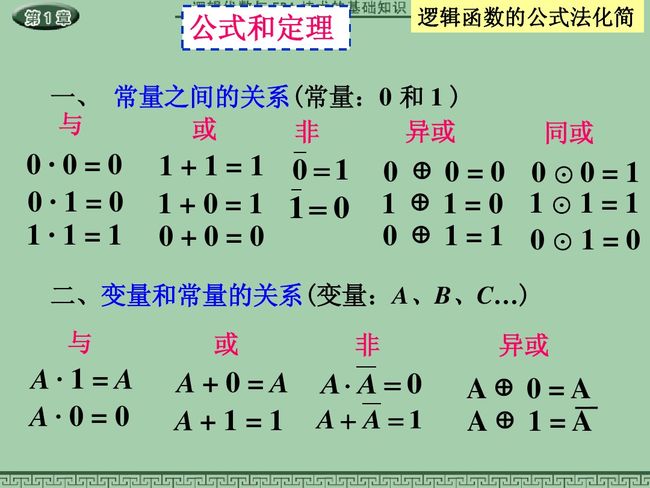

逻辑函数的公式化简

参考文章

华为面经:https://blog.csdn.net/u010368758/article/details/47911517

三种同步FIFO的实现方法(verilog实现)

数字IC设计工程师笔试面试经典100题

数字电路基础知识(一)

这里面流水线乘法器写的很好

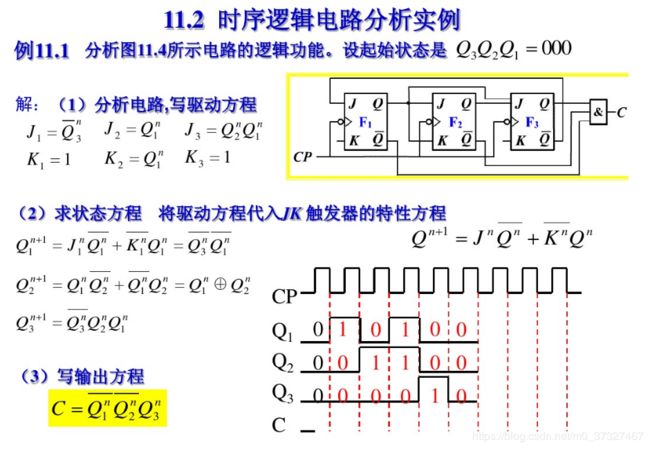

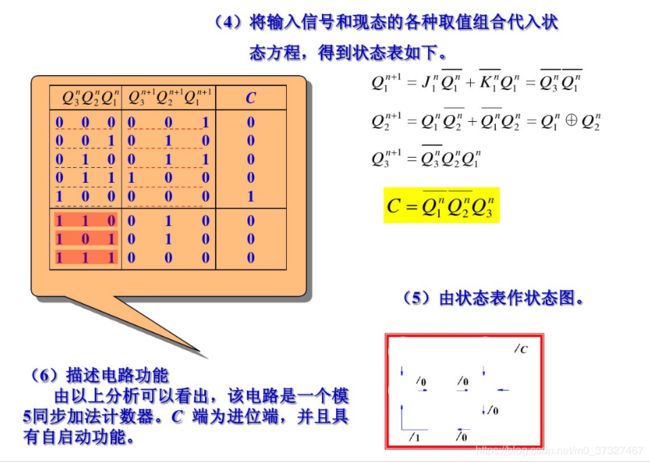

时序逻辑电路分析有几个步骤(同步时序逻辑电路的分析方法)

问题:

知识点:verilog基本语法、时序逻辑电路组合逻辑电路、是否能综合、setup/hold time分析、毛刺的成因(竞争冒险)、FSM(二段三段式)、FIFO(同步异步)、串并转换、分频电路(奇数分频,偶数分频)、流水线的实现、乒乓buffer,数电逻辑式计算。MUX实现乘法。

Always 中的变量都要设置为reg类型, always块内部的语句顺序执行,always块称为过程块,always块中的语句称为顺序语句。

同一Verilog模块中所有过程块(如initial/always)、连续赋值语句、实例引用语句都是并行的,前后次序没有关系。

always块内部的语句顺序执行,always块称为过程块,always块中的语句称为顺序语句

Fork join是并行的,所有的时钟信号都是基于刚开始的信号

二进制编码、格雷码编码

二进制编码、格雷码编码使用最少的触发器,消耗较多的组合逻辑,而独热码编码反之。独热码编码的最大优势在于状态比较时仅仅需要比较一个位,从而一定程度上简化了译码逻辑。虽然在需要表示同样的状态数时,独热编码占用较多的位,也就是消耗较多的触发器,但这些额外触发器占用的面积可与译码电路省下来的面积相抵消。

Binary(二进制编码)、gray-code(格雷码)编码使用最少的触发器,较多的组合逻辑,而one-hot(独热码)编码反之。one-hot 编码的最大优势在于状态比较时仅仅需要比较一个bit,一定程度上从而简化了比较逻辑,减少了毛刺产生的概率。由于CPLD更多地提供组合逻辑资源,而FPGA更多地提供触发器资源,所以CPLD多使用gray-code,而FPGA多使用one-hot编码。另一方面,对于小型设计使用gray-code和binary编码更有效,而大型状态机使用one-hot更高效。

双向三态数据总线

双向是指可以两个方向传输,可以A->B也可以A<-B

三态指 0, 1和第三态(tri-state)。tri-state既不是一也不是零,三态门的闭合无输出高阻状态。

================================

一般的门输出不是一就是零。 门单元里面有两个管子(n管和p管),一个接地(gnd),一个接电源(vdd)。选择将某个管子接通就可以输出1或者0。

三态门单元通常只有一个管子(出0或者1)。在关闭(tri-state)的状态下,管子被关上了,处于没有任何输出的状态。这种情况下,线路可以由接在线路上的其他驱动(包括上拉/下拉)控制。

比如A->B的时候,B的输出就会是tri-state,bus的状态由A决定。A<-B的时候,A的输出就是tri-state。这样可以防止一条线路上出现两个(或者多个)输出驱动(会形成对拉的局面)。

要是一根线路上接了N个驱动也可以这样做,只有一个输出,其他处于tri-state装台

时序逻辑电路分析

乒乓buffer

所谓ping-pong buffer,也就是定义两个buffer,当有数据进来的时候,负责写入buffer的进程就寻找第一个没有被占用而且可写的buffer,进行写入,写好之后,将占用flag释放,同时设置一个flag提示此buffer已经可读,然后再接下去找另外一个可写的buffer,写入新的数据。

而读入的进程也是一直对buffer状态进行检测,一旦发现没有被占用,而且已经可以被读,就把这个buffer的数据取出来,然后标志为可写。

触发器

建立时间和保持时间(这个图画的很详细)

Setup time, Tsu 建立时间 在时钟沿到来之前数据稳定不变的时间,如果建立的时间不满足,那么数据将不能在这个时钟上升沿被稳定的打入触发器

Hold time, Th 保持时间 时钟沿到来之后数据稳定不变的时间,如果保持时间不满足,那么数据同样也不能被稳定的打入触发器

Clock-to-Output Delay,Tco 数据输出延迟,输出响应时间 当时钟有效沿变化后,数据从输入端到输出端的最小时间间隔

verilog 实现任意分频

偶分频:clk 计数到 N/2 -1时反转一次

奇分频:clk 上升沿计数到 (N-1)/2, clk反转一次,计数到N-1再反转一次,和计数到下降沿的结果相或就好了。

计算机体系结构——流水线技术(Pipelining)

敏感列表

敏感信号(表达式)又称事件表达式或敏感表,当其值改变时,则执行一遍块内语句; 在敏感信号表达式中应列出影响块内取值的

敏感信号列表出现在always块中,其典型行为级的含义为:只要敏感信号列表内的信号发生电平变化,则always模块中的语句就执行一次,因此设计人员必须将所有的输入信号和条件判断信号都列在信号列表中。有时不完整的信号列表会造成不同的仿真和综合结果,因此需要保证敏感信号的完备性。在实际的PLD 器件开发中,EDA 工具都会默认将所有的输入信号和条件判断语句作为触发信号,增减敏感信号列表中的信号不会对最终的执行结果产生影响,因此如果期望在设计中通过修改敏感信号来得到不同的逻辑,那就大错特错了。当敏感信号不完备时,会使得仿真结果不一样,这是因为仿真器在工作时不会自动补充敏感信号表。如果缺少信号,则无法触发和该信号相关的仿真进程,也就得不到正确的仿真结果。

数字ic设计流程

设计相应功能

设计相应模块

verilog HDL硬件描述语言设计

后端验证

综合仿真

静态时序验证

行为验证

长沟道器件电压和电流的关系

截止区 线性区 饱和区

动态功耗:对负载电容充电和放电造成的功耗

短路功耗:开关过程中电源和地之间顺吉纳的直流通路造成的功耗

静态功耗:稳定输出高电平或低电平时的直流功耗,漏电流造成

亚稳态

亚稳态指的是触发器在规定的时间内还没有达到一个确定的状态

DMA(直接内存访问)

他可以直接让硬件访问内存,而不需要cpu的终端

FIFO

https://www.cnblogs.com/ant2012/archive/2012/02/22/2362328.html,介绍了FIFO的verilog代码

1):能够实现缓存的作用,防止数据丢失

2):数据集中起来进行处理,不需要频繁的总线操作

3):允许进行DMA的操作,提高系统的传输速率

Verilog整理笔记之SRAM篇

RAM家族

理解FPGA中的RAM、ROM和CAM;ROM、RAM、DRAM、SRAM、FLASH

DRAM:dynamical random memory,动态随机存储器,需要每隔一段时间刷新一下

ROM:只读存储器,停止供电之后任然可以保存数据,一般用在计算机指令集的存储

PROM:可编程的,但是只能编程一次

EPROM:可擦写,可编程,用紫外线擦除

RAM:随机访问存储器,通常都是停止供电之后数据消失,典型的RAM是计算机的内存

SRAM:静态存储器,访问速度快,但是价格昂贵

DRAM: 保留数据的时间很短,但是便宜,不过比任何的ROM都要快,计算机内存就是DRAM

FLASH:结合了RAM和ROM的优点

1.可擦除,可编程

2.断电不丢失数据

3.快速读取数据

HDL语言的层次概念

算法级 语言级 RTL级 门级

verilog 关键字

buf:缓冲器,只有一个输入, 可以有多个输出

event: 事件,当满足某些条件之后进行触发

initial:在仿真中使用,进行初始化,假如有多个initial,则多个initial中的语句并行处理。

逻辑函数的公式化简

1. Y=AB'+A'CD+B+C'+D'

= A + B + A'CD + C' + D'

= A + B + CD + C' + D'

= A + B + C + D + C'

= 1

Y=B+BCD+B'CD+AB+A'B+B'C

= B + B'CD + AB + A'B + B'C

= B + CD + A + B'C

= C + B + CD + A

= C + B + A

Y=ABC+A'B+ABC'

= AB + A'B

= B