【微机原理与接口技术】学习笔记9 DMA控制器8237A

文章目录

- 9.1 8237A 的组成与工作原理

- 9.1.1 DMA传送

- 9.1.2 8237A的内部结构

- 9.1.3 8237A的引脚功能

- 9.1.4 8237A的内部寄存器

- 9.2 8237A的时序

- 9.3 8237A的编程和应用举例

- 9.3.1 DMA系统组成

- 9.3.2 DMA系统有效地址的生成

- 1. 74LS670工作原理

- 2. DMA系统有效地址的生成

- 3. IBM-PC微机的DMA系统

- 4. DMA系统的初始化

- 5. DMA传送的应用

9.1 8237A 的组成与工作原理

9.1.1 DMA传送

用 DMA 方式传送数据时,传送过程完全由 DMA 控制器(DMAC)控制。其基本功能:

DMAC能向CPU的HOLD脚发出DMA请求信号。- CPU响应

DMA请求后,DMAC获得总线控制权,由它控制数据的传送,CPU则暂停工作。 - 能提供读/写存储器或I/O设备的各种控制命令。

- 确定数据传输的始址和数据长度(CPU配置的),每传送1个数据便自动修改地址(

+1或-1),数据长度-1。 - 传送完毕,能发出结束

DMA传送的信号。 - CPU在每个非锁定时钟周期结束后,都会检测

HOLD脚上有无DMA请求?若有,便转入DMA传送周期。

8237A 是高性能可编程 DMA 控制器,主要特点:

- 含

4个通道,每通道有64K地址(16位)和字节计数能力(16位)。 - 有

4种传送方式:单字节传送、数据块传送、请求传送、级联传送。 - 每个通道的

DMA请求可被允许或禁止。4个通道的DMA请求有不同优先级,优先级可以是固定的,也可以是循环的。 - 任一通道完成数据传送后,会自动产生过程结束信号

EOP(End of Process,不常用),结束DMA传送;还可从外界输入EOP信号,中止正执行的DMA传送。

8237A 的两种工作状态

1)从态方式

开始 DMA 传送前,8237A 是系统总线的从属设备,由CPU对它进行编程,如指定通道、传送方式和类型、内存单元起始地址、地址是递增还是递减以及要传送的总字节数等等;CPU也可读取 DMAC 的状态。

2)主态方式

当 8237A 取得总线控制权后,它就完全控制了系统,使I/O设备和存储器之间或者存储器与存储器之间进行直接的数据传送。

8237A 芯片的内部结构和外部连接与这两种工作状态密切相关。

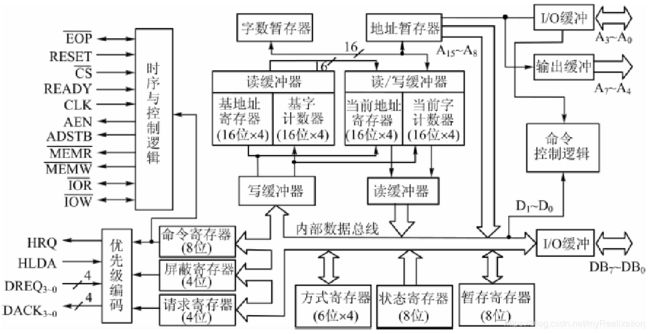

9.1.2 8237A的内部结构

-

时序与控制逻辑

从态时,接收系统时钟、复位、片选和读/写等信号,完成相应控制操作;主态时, 向系统发控制信号。

其中与设备相连的是 IOR ‾ , IOW ‾ \overline {\text{IOR}},\overline {\text{IOW}} IOR,IOW ,其他的要么和CPU相连,要么和系统总线相连。

MEMR ‾ , MEMW ‾ \overline {\text {MEMR}},\overline {\text{MEMW}} MEMR,MEMW 是主态时进行内存读写的命令。 -

优先级编码电路

对同时提出DMA请求HRQ(Hold Request)的多个通道进行排队判优,决定哪个通道优先级最高,然后进行响应HLDA(Hold Acknowledge)。

可选固定或循环优先级。某个优先级高的设备服务时,禁止其它通道请求。 -

数据和地址缓冲器组

8237A的A7~A4(单向输出)、A3~A0(双向:从态时A3-A0输入有4根线,说明占了16个端口地址;主态时:A3-A0、A7-A4、DB7-DB0共16根地址线往内存输出,读或写数据) 为地址线;

DB7~DB0在从态时传输(CPU配置或读取DMA的)数据,主态时传送地址。它们都与三态缓冲器相连,便于接管或释放。 -

命令控制逻辑

从态时接收CPU送来的寄存器选择信号(A3~A0),选择寄存器;主态时译码方式字的D1D0,以确定操作类型。A3~A0与 IOR \text{IOR} IOR 、 IOW \text{IOW} IOW 配合组成各种操作命令。 -

内部寄存器组

每通道有16位基址寄存器、基字计数器、当前地址寄存器、当前字计数器以及6位工作方式寄存器。

片内还有命令寄存器、屏蔽寄存器、请求寄存器、状态寄存器和暂存寄存器。

不可编程的字数暂存器和地址暂存器。

9.1.3 8237A的引脚功能

CLK时钟信号,输入

8237A时钟频率3MHz,8237A-5为5MHz。- CS ‾ \overline \text{CS} CS 片选信号,输入,低电平有效。

从态方式下选中8237A,接受CPU对它的编程等。 READY准备好,输入,高电平有效

慢速I/O设备或存储器参与DMA传送时,可使READY变低,让8237A在DMA周期中插入等待周期TW;当它们准备就绪时READY变高。A3~A0低4位地址线

从态为输入,寻址8237A内部寄存器,实现编程;主态时输出要访问内存的低4位地址。A7-A4高4位地址线

始终是输出或浮空,主态时输出4位地址信息A7-A4。DB7-DB08位数据线,与系统数据总线相连。- 从态时,CPU经过数据线读取各有关寄存器内容,并对各寄存器编程。

- 主态时,由它们输出高

8位地址A15-A8,并由ADSTB信号将它们锁存到外部的高8位地址寄存器中,与A7-A0输出的低8位地址构成16位地址。 - 存储器-存储器传送方式下,源存储器读出的数据,经它们送暂存寄存器,暂存器中数据再经它们写到目的存储单元中。

AEN地址允许信号,输出,高电平有效

送出锁存的高8位地址,与芯片输出的低8位地址一起构成16位内存偏址。同时使连到CPU的地址锁存器无效,保证地址线上的信号来自DMAC。ADSTB地址选通信号,输出,高电平有效

选通外部地址锁存器,将DB7~DB0上的高8位地址送到外部的地址锁存器。- IOR ‾ \overline {\text{IOR}} IOR

I/O读信号,双向。

从态时,控制CPU读取8237A内部寄存器。

主态时,与 MEMW ‾ \overline {\text{MEMW}} MEMW 配合,控制数据由外设传到存储器中。 DREQ3~DREQ0通道3~0的DMA请求信号,输入

外设请求DMA服务时,向这些引脚发请求信号,有效极性由编程确定。固定优先级时,DREQ0的优先级最高,编程可改变优先级。HRQ保持请求信号,输出,高电平有效

向CPU的HOLD端发出的DMA请求信号,可从8237A任一个未被屏蔽的通道发出。HLDA保持响应信号,输入,高电平有效

与CPU的HLDA相连,CPU收到HRQ信号后,至少经过1个时钟周期后,使HLDA变高,表示已让出总线控制权,8237A收到HLDA信号后,便开始DMA传送。DACK3~DACK0通道3~0的DMA响应信号,输出

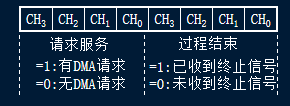

其有效电平极性由编程确定。相应通道开始DMA传送后,DACKi有效,通知外部电路现已进入DMA周期。- EOP ‾ \overline {\text{EOP}} EOP 传输过程结束信号,双向,低电平有效

DMA传送中,任一通道的字计数器减为0,再由0减为FFFFH而终止计数时,会在 EOP ‾ \overline {\text{EOP}} EOP 引脚上输出低电平信号,表示DMA传输结束。

也可在 EOP ‾ \overline {\text{EOP}} EOP 脚上输入低电平信号来终止DMA传送。

若通道设置成自动预置状态,该通道完成一次DMA传送,出现 EOP ‾ \overline {\text{EOP}} EOP 信号后,又能自动恢复有关寄存器的初值,继续执行另一次DMA传送。

9.1.4 8237A的内部寄存器

8237A的内部可编程寄存器主要有 10 种:

-

当前地址寄存器

16位,每通道1个,存放DMA传送的存储器地址值。每传送1个数据,地址值自动+1或-1,指向下个单元。

编程时可写入初值,也可被读出,但每次只能读/写8位,所以读/写要两次完成。

自动预置操作方式,在 EOP \text{EOP} EOP 有效时,会重装入基地址值。 -

当前字计数寄存器

16位,每通道1个,编程时置其初值为实际传送字节数少1。每传送1字节,自动-1。由0~FFFFH时,将产生终止计数信号TC。

自动预置操作方式,在 EOP \text{EOP} EOP 有效时,会重装入基字计数寄存器的内容。 -

基地址寄存器

16位,每通道1个,存放通道当前地址寄存器初值,与当前地址寄存器地址一样,编程时写入相同值。

其内容不能读出和修改。用在自动预置操作时,使当前地址寄存器恢复到初值。 -

基字计数寄存器

16位,每通道1个,存放通道当前字计数器初值,该值也是编程时与当前字计数器一起写入的。

其内容不能读出和修改,用于自动预置操作时,使当前字计数器恢复到初值。 -

命令寄存器

全局,8位,控制8237A的操作。由CPU编程来设置8327A操作方式, 复位时清除。

D0位:能否进行存储器到存储器传送,D0=1允许。并规定先用通道0从源单元读入1字节放入暂存器,然后由通道1把该字节写到目的单元,接着两通道的地址分别+1或-1,通道1的字计数器-1,它减为0时产生终止计数信号TC,并输出 EOP \text{EOP} EOP 信号,终止DMA服务。D1位:存储器到存储器传送时,通道0地址能否保持不变。D1=1,通道0在传送中保持同一地址,从而可把该单元中的数写入一组存储单元。D1=0禁止。当D0=0时这种方法无效。D2位:允许或禁止8237A工作,D2=0允许,D2=1则禁止。D4位 优先权控制。D4=0为固定优先权,通道0优先级最高;D4=1为循环优先权,刚服务过的通道i优先权最低,而通道i+1优先权最高。随着DMA操作不断进行优先权不断循环,防止某通道长时间占用总线。D6位:决定DREQ的有效电平,0高电平有效,1则低电平有效。D7位:决定DACK的有效电平,1高电平有效,0则低电平有效。D3位和D5位:有关时序的操作,见后面时序讨论。

-

工作方式寄存器

6位,每通道1个,选择DMA的传送方式和类型等,格式:

-

D1D0位:选择通道,并进一步由D2-D7指定选定通道的工作方式。这样4个通道可合用1个方式寄存器。 -

D3D2位:决定所选通道的DMA操作类型。从3种DMA传送类型中选定一种:

10:读传送,存储器->I/O设备, 发 MEMR ‾ , IOW ‾ \overline {\text{MEMR}},\overline {\text{IOW}} MEMR,IOW ,

01:写传送,存储器<-I/O设备, 发 MEMW ‾ , IOR ‾ \overline {\text{MEMW}},\overline {\text{IOR}} MEMW,IOR ,

00:校验传送,伪传送,8237A会产生地址信息和

EOP \text{EOP} EOP 信号,不会发出读写控制信号,用于测试。 -

D4位:所选通道是否进行自动预置操作。如果D4=1,则选择自动预置。 -

D5位:方向控制位。D5=0数据传送由低址向高址方向进行,每传送1字节,地址+1。D5=1时传送方向相反。 -

D7D6位:定义所选通道操作方式。有4种传送方式:

1) 单字节传送方式(常用于软盘)

每次DMA操作只传送1字节。之后字计数器-1,地址寄存器+1或-1,HRQ无效,释放系统总线。当字计数器由0减为FFFFH时,产生终止信号TC。

此后即使DREQ继续有效,8237A的HRQ输出仍进入无效状态并让出总线,由CPU控制至少一个总线周期。2) 数据块传输方式

进入DMA服务后,可连续传输一批数据,直到字计数器由0减为FFFFH产生TC信号,或从外部送来 EOP \text{EOP} EOP 信号时,才释放总线,结束DMA传输。3)请求传送方式

也连续传送数据,直到字计数器由0减为FFFFH产生TC,或外界送来 EOP \text{EOP} EOP 信号。但每传送1字节后,都要测试DREQ端,一旦发现此信号无效,马上停止。

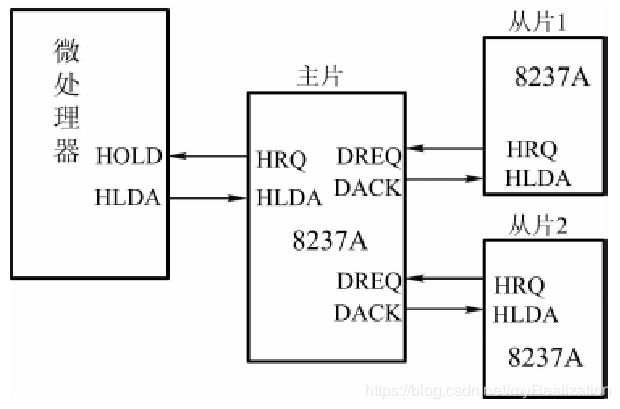

地址和字计数器的中间值会被保存在通道的现行地址和字计数器中,外设准备好新数据时,可使DREQ再变为有效,又从断点处继续进行传输。4)级联传送方式

连接多个8237A以扩充DMA通道,连线见图11.5。

主片DREQ—从片HRQ,主片DACK—从片HLDA,主片HRQ和HLDA与CPU的HOLD和HLDA相连。1块主片可连4块从片。主片置为级联传送,从片设成其它三种方式。主片不输出地址和读写信号。

-

-

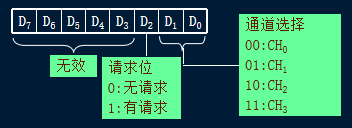

请求寄存器

相应请求位置1时,对应通道可产生DMA请求。相应位可由DREQ信号置1,也可写入通道请求字来置1或清0。

D1D0位选通道号,D2位为请求位。请求位不能屏蔽,其优先权受优先权逻辑控制,TC或外部的 EOP \text{EOP} EOP 信号能将相应的请求位清0,RESET信号则使整个请求寄存器清0。

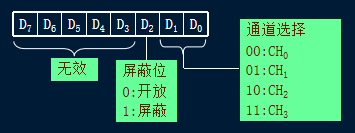

-

屏蔽寄存器

4位,1个/通道。禁止/允许对应通道的DREQ请求进入请求寄存器。有两种屏蔽字,端口地址不同。

1)通道屏蔽字

可对该寄存器写入通道屏蔽字来对单个屏蔽位置1/复位。通道屏蔽字格式与通道请求字格式类似:

2)主屏蔽字

还允许用主屏蔽命令设置通道的屏蔽触发器。D3~D0位对应通道3~0的屏蔽位,1屏蔽,0清除屏蔽。可写入主屏蔽字,一次完成4个通道的屏蔽位设置。可用软件同时清除4个通道的屏蔽位。

-

状态寄存器

8位状态寄存器存放状态信息,供CPU读出。如D3~D0中置1的通道,已达计数终点TC或外部送来了 EOP \text{EOP} EOP 信号。D7-D4中置1的通道,DMA请求还未处理。复位或被读出后,相应状态位被清除。状态字格式:

-

暂存寄存器

在存储器->存储器传送时,保存所传送的数据。其中始终保存着最后1个传送的字节,RESET信号会将其清除。编程状态下,可由CPU读出这个字节。 -

软件命令

编程状态下,8237A可执行3个附加的特殊软件命令,只要对特定端口进行一次写操作,命令就会生效。

1)清除先/后触发器

8237A仅8根数据线,而地址寄存器和字计数器均为16位,CPU要分两次读写。先/后触发器控制高低字节读写次序。清0读写低8位,随后自动置1,读写高8位。接着又清0,… 。对该触发器所在的寄存器执行一次写操作便清0,复位和 EOP \text{EOP} EOP 信号有效也将它清为0。

2)主清命令

主清命令也称为复位命令,功能与RESET信号同,它可使命令寄存器、状态寄存器、请求寄存器、暂存寄存器和内部先/后触发器均清0,而把屏蔽寄存器置1。复位后,8237A进入空闲状态。

3)清除屏蔽寄存器

该命令能清除4个通道的全部屏蔽位,允许各通道接受DMA请求。 -

各寄存器的端口地址

对8237A内部寄存器读写时, CS ‾ \overline {\text{CS}} CS 端必须为低电平,该信号由高位地址经I/O译码后产生。

A3~A0线选择不同寄存器,共占16个I/O端口地址。常将它们与地址总线低4位A3~A0相连,选择各寄存器。

例如,PC/XT机中,地址A9~A4=000000时,经I/O译码电路选中8237A,使其有效。 地址A3~A0与8237A的A3~A0脚连接实现片内寻址。因此基地址=00H,记为DMA=00H。由此可得其他寄存器的地址,如DMA+00H为通道0基地址与当前地址寄存器地址,DMA+08H为状态寄存器地址等:

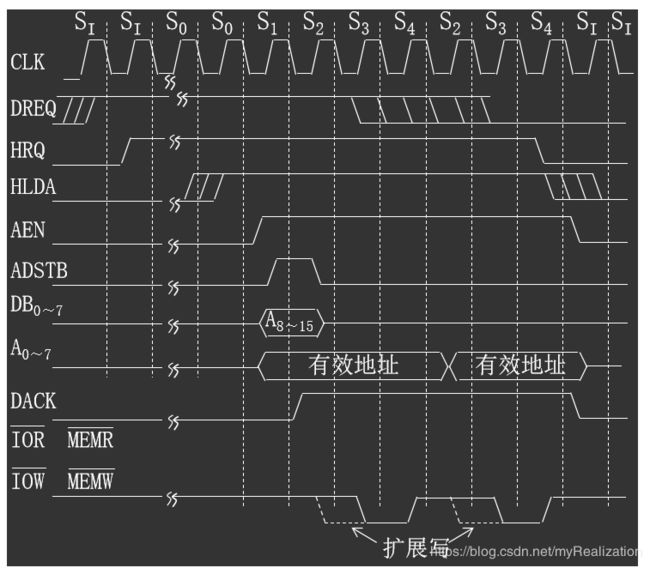

9.2 8237A的时序

空闲周期 SI :未发生 DMA 请求时

- 检测

CS:CPU是否对其操作 - 检测

DREQ:外设是否有请求

过渡状态 S0 :DMAC 发出 HRQ 之后,收到 HLDA 之前。

有效周期:DMAC 收到 HLDA 之后,接管总线:

包括 4 个状态周期(S1、S2、S3、S4),慢速I/O或M还可通过令 READY=0 申请插入 SW ,8237A-5 在 S3 中检测 READY ,SW 中的操作同 S3 :

S1:更新高8位地址,AEN、ADSTB有效,DMAC将M的A8~15放到DB0~7上;只有当A8~15有变化时才出现S2:选中两个介质,输出16位地址选中M:低8位由A0~7直接输出;高8位由DB0~7经外部锁存器(由ADSTB下降沿锁存)输出;发出有效的DACK选中I/OS3:读周期。发出IOR(DMA写)或MEMR(DMA读),从源读数据到DB0~7,等待写周期。S4:写周期。发出MEMW(DMA写)或IOW(DMA读),将DB0~7上的数据写到目标中。

扩展写:写提前到与读同时开始(S3),与读一样扩展到 2 个时钟周期。

压缩时序:去掉 S3 ,读与写同为 1 个时钟周期。

SW :慢速I/O或M传送时,在 S3 和 S4 间插入 SW 。

9.3 8237A的编程和应用举例

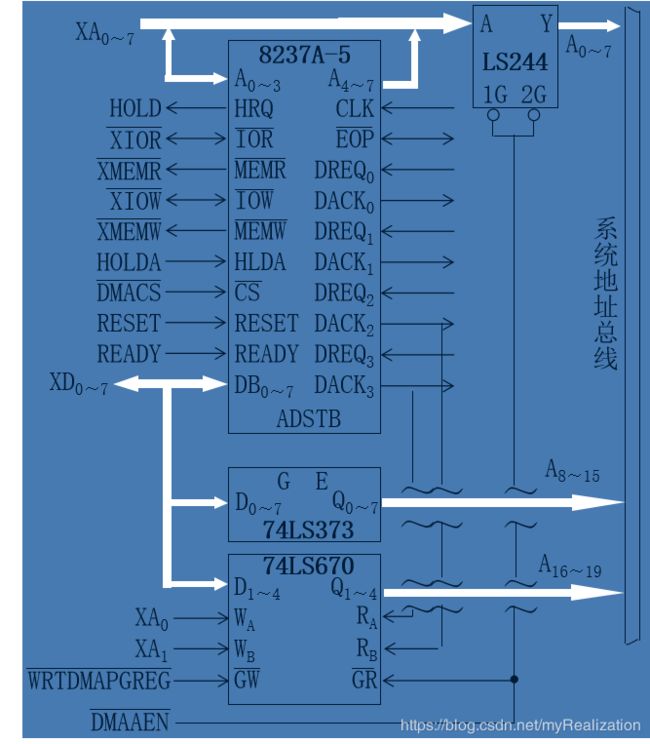

9.3.1 DMA系统组成

PC机的DMA系统:

- 8237A-5

- 页面地址寄存器

- 总线裁决逻辑

9.3.2 DMA系统有效地址的生成

第一代PC机中的地址是 20 位的,而 8237A 是 16 位的。为此需要一个 74LS670 扩展地址。

1. 74LS670工作原理

74LS670 的 RA,RB 和 DACK2,DACK3 连接,内有 4 个 4 位寄存器。读写分开控制:

- 写: GW ‾ = 0 \overline {\text{GW}}=0 GW=0;

WA、WB:写入寄存器选择;D1~4:数据输入 - 读: GR ‾ = 0 \overline {\text{GR}}=0 GR=0;

RA、RB:读出寄存器选择;Q1~4:数据输出

2. DMA系统有效地址的生成

如何提供存储器的地址:

A16~19:由74LS670提供;A8~15:由8237A-5的DB0~7经74LS373提供;A0~7:由8237A-5的A0~7直接提供;

如何对I/O设备寻址,用 DACK 信号取代芯片选择和片内端口选择:

3. IBM-PC微机的DMA系统

单片 DMAC 的 DMA 系统:4 个通道;8 位传送;1MB 寻址;64KB 计数

双片DMAC的DMA系统:

如果我们打开设备管理器,可以在直接内存访问控制器中看到上图双片DMAC结构中,出现的端口地址。

4. DMA系统的初始化

注意事项:

- 初始化前要对芯片检测

- 初始化前禁止工作或屏蔽通道

- 所有通道的方式寄存器均加载

- 要初始化页面地址寄存器

初始化编程:

① PC机检测芯片(8 个 16 位寄存器全 1 、全 0 的读写)及加载校验方式:

MOV AL, 04H ;0000_0100:前4位默认配置,正常时序,禁止工作,CR0地址不保持,禁止内存到内存

OUT DMA+08H, AL ;写入命令寄存器

OUT DMA+OCH, AL ;清先后触发器

MOV AL, 0FFH ;1111_1111:全1的读写测试

C16: MOV BL, AL ;全1或全0

MOV BH, AL ;全1或全0

...

...

MOV CX, 8 ;对8个寄存器做读写测试

MOV DX, DMA ;从DMA开始测试

C17: OUT DX, AL ;全1或全0写入DX

OUT DX, AL ;再写一次,16位写两次,先写低八位,再写高八位

IN AL, DX ;读出低八位

MOV AH, AL ;

IN AL, DX ;读出高八位,放入AX中

CMP BX, AX ;和之前保存的AL对比

JE C18 ;如果相同,证明该寄存器没有出错

HLT ;不相同则停机

C18: INC DX ;DX端口号+1

LOOP C17 ;再重复循环

...

INC AL ;AL+1=全0

JE C16 ;为0,跳转回C16,做全0测试

...

...

...

...

...

...

SUB AL, AL ;AL清0

OUT DMA+08H, AL ;写入命令寄存器,高4位按照默认配置,低4位正常时序,允许工作,其他位默认;启用芯片

;下面将40H,41H,42H,43H先后写入工作方式寄存器,,即对全部的通道写入同样的工作方式

MOV AL, 40H ;0100_0000针对0号通道

OUT DMA+0BH, AL ;单字节方式,地址递增,禁止地址预置,校验方式

MOV AL, 41H ;0100_0001针对1号通道

OUT DMA+0BH, AL ;单字节方式,地址递增,禁止地址预置,校验方式

MOV AL, 42H ;0100_0010针对2号通道

OUT DMA+0BH, AL ;单字节方式,地址递增,禁止地址预置,校验方式

MOV AL, 43H ;0100_0011针对3号通道

OUT DMA+0BH, AL ;单字节方式,地址递增,禁止地址预置,校验方式

5. DMA传送的应用

例:利用级联的 IBM PC/AT 的 8237 主片通道 5 ,将内存其始地址为 80000H 的280H 字节的内容直接输出到外部设备。

MOV AL, 04H ;命令字, 禁止82C37工作

OUT 0D0H, AL ;写命令寄存器

MOV AL, 0

OUT 0D8H, AL ;清除先/后触发器

OUT 0C4H, AL ;写低位地址

OUT 0C4H, AL ;写高位地址

MOV AL,04H ;页面地址为8

OUT 08BH, AL ;写页面寄存器

MOV AX, 280H ;传输字节数

DEC AX

OUT 0C6H, AL ;写字节数低位

MOV AL, AH

OUT 0C6H, AL ;写字节数高位

MOV AL, 89H ;方式字: 单字节读, 地址加1

OUT 0D6H, AL

MOV AL, 05H ;写请求寄存器

OUT 0D2H, AL

DMA控制器与I/O设备的连接:DMAEN 是 DMA 申请允许信号;软盘接口中的数据输出寄存器(3F2H)的 D3 位控制,高有效

ROM-BIOS 中软盘 DMA_SETUP:

AL——方式字(CH2,单一传送,非自动预置,地址增量)42H:DMA校验(软盘校验)46H:DMA写(读软盘)4AH:DMA读(写软盘)ES:BX——内存首址DH——要传送的扇段数

字节数/扇段在磁盘基址区 DISK_BASE 的 3 号单元

0:128字节/扇段1:256字节/扇段2:512字节/扇段3:1024字节/扇段

DMA_SETUP PROC

PUSH CX ;保护现场

CLI

OUT DMA+12, AL ;清先/后触发器

OUT DMA+11, AL ;设置方式

;形成物理地址

MOV AX, ES

MOV CL, 4

ROL AX, CL

MOV CH, AL

AND AL, 0F0H

ADD AX, BX

JNC J33

INC CH

J33: PUSH AX ;低16位地址入栈

...

;设置地址寄存器及页面地址

OUT DMA+4, AL ;写低16位地址

MOV AL, AH

OUT DMA+4, AL

MOV AL, CH

AND AL, 0FH ;写高4位地址

OUT 81H, AL

;设置字节计数器

MOV BX, 6

CALL GET_PAM ;取DISK_BASE的3号单元作为移位次数

MOV CL, AH

MOV AH, DH

SUB AL, AL

SHR AX, 1

SHL AX, CL

DEC AX

PUSH AX ;N-1入栈保护

...

OUT DMA+5, AL

MOV AL, AH

OUT DMA+5, AL

STI

;判DMA是否超界

POP CX ;用低16位地址与N-1相加设置CF

POP AX

ADD AX, CX

POP CX ;恢复现场

MOV AL, 02H

OUT DMA+10, AL

RET

DMA_SETUP ENDP