解读 8 位移位寄存器的设计

8 位移位寄存器的设计

先了解下 8 位移位寄存器的设计的原理,先从基础开始:要求掌握 8 位移位寄存器原理,并根据原理设计 8 位移位寄存器模块以及设计相关testbench,最后在 Robei 可视化仿真软件进行功能实现和仿真验证。

首先:有一个 8 比特的数据(初值设为 10011100)和一个移位设置数据 s,根据 s 的值不同,产生不同的移位。这里规定移位的方向是向右,由于是 8 比特,因此 s 的变化范围为 0 到 7。

****第一步shift 模型设计

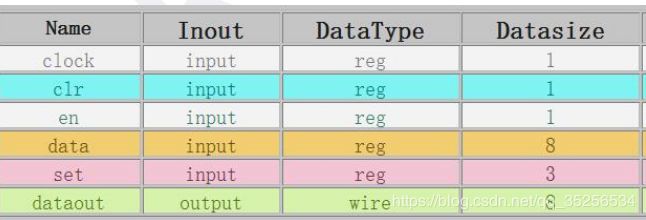

(1)新建一个模型命名为 shift,类型为 module,同时具备 5 个输入和 1 个输出,每个引脚的属性和名称进行对应的修改

(2)添加代码。点击模型下方的 Code 添加代码。

always@(posedge clk or negedge clr)

begin: shift_reg

if(clr)

data_out <= 8'b0;

else if(en)

begin

case(set[2:0])

3'b0: data_out <= data_in[7:0];

3'b1: data_out <= {data_in[0],data_in[7:1]};

3'd2: data_out <= {data_in[1:0],data_in[7:2]};

3'd3: data_out <= {data_in[2:0],data_in[7:3]};

3'd4: data_out <= {data_in[3:0],data_in[7:4]};

3'd5: data_out <= {data_in[4:0],data_in[7:5]};

3'd6: data_out <= {data_in[5:0],data_in[7:6]};

3'd7: data_out <= {data_in[6:0],data_in[7]};

default: data_out <= data_in[7:0];

endcase

end

end

(3)保存模型到一个文件夹(文件夹路径不能有空格和中文)中,编译并检查有无错误输出。

Robei软件中保存文件的时候文件名不能有空格河中文,同时要把设计文件和测试文件一起保存到一个文件夹。

第二步: shift_test 测试文件设计

1、新建一个具有 5 个输入和 1 个 输出的 shift_test 测试文件,记得将 Module Type 设置为“testbench”,各个引脚配置。

2、另存为测试文件。将测试文件保存到上面创建的模型所在的文件夹下。

3、加入模型。在 Toolbox 工具箱的 Current 栏里会出现模型,单击该模型并在 shift _test上添加,并连接引脚

(4)输入激励。点击测试模块下方的“Code”,输入激励算法。激励代码在结束的时候要用**$finish** 结束。

测试代码:

initial begin

clock=0;

clr=0;

en=1;

data=8'b10011100;

set=0;

#1 clr=1;

#2 clr=0;

#40 $finish;

end

always #1 clock=~clock;

always #2 set=set+1;

5、执行仿真并查看波形。查看输出信息。

检查没有错误之后查看波形。点击右侧 Workspace 中的信号,进行添加并查看分析仿真结果。

第三步:shift_constrain 测试文件的设计

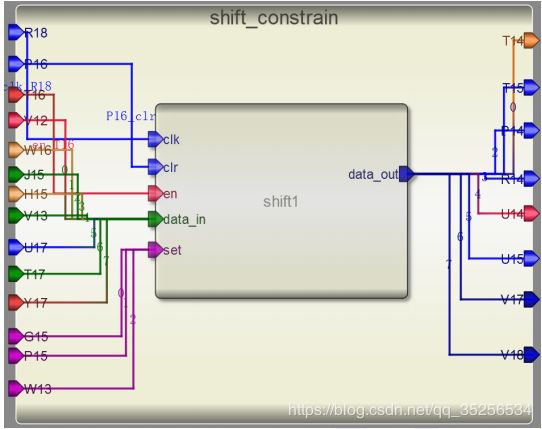

(1)新建一个模块,命名为 shift_constrain,模块类型选择为 constrain,具有 14 个输入和 8个输出

(2)修改端口名称并进行连线。其中,shift 模块的输入 data_in 和输出 data_out 分别对应 8

个端口,输入 set 对应 3 个端口。本设计中,各个端口对应的开发板引脚如下所示:

clk 对应开发板按键开关 R18;

clr 对应开发板按键开关 P16;

en 对应开发板拨码开关 T16;

set[0],set[1],set[2]对应 G15,P15,W13;

data_in[0]——data_in[7]分别对应 V12,W16,J15,H15,V13,U17,T17,Y17;

data_out[0]——data_out[7]分别对应 T14,T15,P14,R14,U14,U15,V17,V18;

输入 data_in 对应的连线名称需要改成 0——7,set 的连线名称则要改成 0,1,2。修改后的约束模块

(3)保存并执行,如果软件显示“Generate constrain file complete”,说明约束文件已经成功生成。

接下来将通过视频讲解怎样设计:

怎样快速设计移位寄存器

板级验证

为了测试所设计 shift 的工作特性,选择开发板搭载 XILINX 公司的 Z-7010 芯片,选用VIVADO 设计平台进行 SynthesisImplementation 和 Generate Bitstream,最终将生成的数据流文件下载到开发板内,并进行验证。

- VIVADO 设计平台进行后端设计

1.1 启动 Vivado 软件并选择设备 XC7Z010CLG400-1(ZYBO)作为硬件对象,设计语言选用 Verilog,建立新的工程,添加通过 Robei 设计的文件 shift.v。

(1)打开 Vivado,选择开始>所有程序>Xilinx Design Tools> Vivado2013.4> Vivado2013.4; (2)单击创建新项目 Create New Project 启动向导。你将看到创建一个新的 Vivado 项目对话框,单击 Next; (3)在弹出的对话框中输入工程名shift及工程保存的位置,并确保Create project subdirectory复选框被选中,单击 Next;

(4)选择项目类型表单的 RTL Project 选项,不勾选 Do not specify sources at this time 复选框,然后单击 Next;

(5)使用下拉按钮,选中 Verilog 作为目标文件和仿真语言;

(6)点击添加 Add Files 按钮,浏览到刚刚我们 Robei 项目的目录下打开 Verilog 文件夹,选择 shift.v,单击 Open,然后单击 Next 去添加现有的 IP 模型;

(7)由于我们没有任何的 IP 添加,跳过这一步,直接单击 Next 去添加约束形成;

(8)点击添加 Add Files 按钮,浏览到刚刚建立约束模块目录下的 constrain 文件夹,选择shift_constrain.xdc,单击 Open 进行添加,然后单击 Next;

(9)在默认窗口中,按照图,设置 Filer 中的选项,然后在 Parts 中选择对应的

XC7Z010CLG400-1,单击 Next;

(10)单击 Finish,本 Vivado 项目创建成功。

打开 shift_constrain.xdc 文件,查看引脚约束源代码。

(1)在资源窗口 sources 中,展开约束文件夹,然后双击即可打开uart_led_pins.xdc 进入文本编辑模式;

(2)Xilinx 设计约束文件分配 FPGA 位于主板上的开关和指示灯的物理 IO 地址,这些信息可以通过主板的原理图或电路板的用户手册来获得。本次设计的约束文件代码是通过 Robei 软件自动生成,但是,Robei 软件目前生成的约束代码只有对输入输出端口的分配,在这个设计中,我们使用了一个通过开关控制的模拟时钟 clk,而非系统时钟,这种电路在综合的时候一般都会报错,所以,在约束文件最后,我们需要手动添加一句命令:

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets clk_IBUF]

来保证流程中不会出错。

约束代码:

#This file is generated by Robei!

#Pin Assignment for Xilinx FPGA with Software Vivado.

set_property PACKAGE_PIN R18 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property PACKAGE_PIN P16 [get_ports clr]

set_property IOSTANDARD LVCMOS33 [get_ports clr]

set_property PACKAGE_PIN T16 [get_ports en]

set_property IOSTANDARD LVCMOS33 [get_ports en]

set_property PACKAGE_PIN V12 [get_ports data_in[0]]

set_property IOSTANDARD LVCMOS33 [get_ports data_in[0]]

set_property PACKAGE_PIN W16 [get_ports data_in[1]]

set_property IOSTANDARD LVCMOS33 [get_ports data_in[1]]

set_property PACKAGE_PIN J15 [get_ports data_in[2]]

set_property IOSTANDARD LVCMOS33 [get_ports data_in[2]]

set_property PACKAGE_PIN H15 [get_ports data_in[3]]

set_property IOSTANDARD LVCMOS33 [get_ports data_in[3]]

set_property PACKAGE_PIN V13 [get_ports data_in[4]]

set_property IOSTANDARD LVCMOS33 [get_ports data_in[4]]

set_property PACKAGE_PIN U17 [get_ports data_in[5]]

set_property IOSTANDARD LVCMOS33 [get_ports data_in[5]]

set_property PACKAGE_PIN T17 [get_ports data_in[6]]

set_property IOSTANDARD LVCMOS33 [get_ports data_in[6]]

set_property PACKAGE_PIN Y17 [get_ports data_in[7]]

set_property IOSTANDARD LVCMOS33 [get_ports data_in[7]]

set_property PACKAGE_PIN G15 [get_ports set[0]]

set_property IOSTANDARD LVCMOS33 [get_ports set[0]]

set_property PACKAGE_PIN P15 [get_ports set[1]]

set_property IOSTANDARD LVCMOS33 [get_ports set[1]]

set_property PACKAGE_PIN W13 [get_ports set[2]]

set_property IOSTANDARD LVCMOS33 [get_ports set[2]]

set_property PACKAGE_PIN T14 [get_ports data_out[0]]

set_property IOSTANDARD LVCMOS33 [get_ports data_out[0]]

set_property PACKAGE_PIN T15 [get_ports data_out[1]]

set_property IOSTANDARD LVCMOS33 [get_ports data_out[1]]

set_property PACKAGE_PIN P14 [get_ports data_out[2]]

set_property IOSTANDARD LVCMOS33 [get_ports data_out[2]]

set_property PACKAGE_PIN R14 [get_ports data_out[3]]

set_property IOSTANDARD LVCMOS33 [get_ports data_out[3]]

set_property PACKAGE_PIN U14 [get_ports data_out[4]]

set_property IOSTANDARD LVCMOS33 [get_ports data_out[4]]

set_property PACKAGE_PIN U15 [get_ports data_out[5]]

set_property IOSTANDARD LVCMOS33 [get_ports data_out[5]]

set_property PACKAGE_PIN V17 [get_ports data_out[6]]

set_property IOSTANDARD LVCMOS33 [get_ports data_out[6]]

set_property PACKAGE_PIN V18 [get_ports data_out[7]]

set_property IOSTANDARD LVCMOS33 [get_ports data_out[7]]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets clk_IBUF]

(3)点击 File—>Save File 保存文件。

1.3 使用 Vivado 综合工具来综合设计,并进行 Implementation 任务实现。

(1)单击综合任务下拉菜单中的 Run Synthesis,综合过程将分析 shift.v 文件并生成网表文件。当综合过程完成了,且没有错误信息,将会弹出带有三个选项的完成对话框;

(2)如果有错误,根据错误信息提示进行修改,直至综合没有错误成功完成。然后选择 RunImplementation 选项,执行任务实现,然后单击 OK;

(3)任务实现过程将在综合后的设计上运行。当这个过程完成,且没有错误信息,将会弹出带有三个选项的任务实现完成对话框;

(4)如果有错误,根据错误信息提示修改,直至综合没有错误。

1.4 将开发板上的电源开关拨到 ON,生成比特流并打开硬件会话,对 FPGA 进行编程。

(1)确保微型 USB 电缆连接到 PROG UART 接口;

(2)确保 JP7 设置为 USB 提供电源;

(3)接通电源板上的开关;

(4)点击任务实现完成弹出的对话框中 Generate Bitstream 或者点击导航窗口中编程和调试任务中的 Generate Bitstream。当完成比特流生成后会弹出有三个选项的完成对话框;

(5)这一过程将已经生成的 shift.bit 文件放在 shift.runs 目录下的 impl_1 目录下;

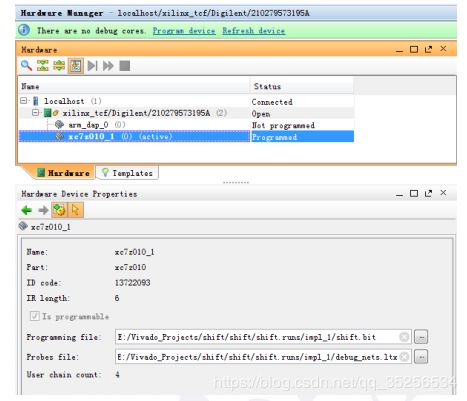

(6)选择打开硬件管理器 Open Hardware Manager 选项,然后单击确定。硬件管理器窗口将打开并显示“未连接”状态;

(7)点击 Open a new hardware target。如果之前已经配置过开发板你也可以点击最近打开目标链接 Open recent target;

(8)单击 Next 看 Vivado 自定义搜索引擎服务器名称的形式;

(9)单击 Next 以选择本地主机端口;

(10)单击两次 Next,然后单击 Finish。未连接硬件会话状态更改为服务器名称并且器件被高亮显示。还要注意,该状态表明它还没有被编程;

(11)选择器件,并验证 shift.bit 被选为常规选项卡中的程序文件;

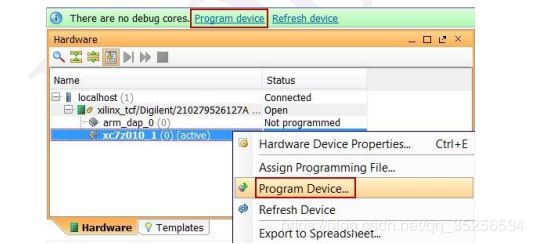

(12)在器件上单击鼠标右键,选择 Program device 或单击窗口上方弹出的 Program device-> XC7z010_1 链接到目标 FPGA 器件进行编程,

(13)单击确定对 FPGA 进行编程。开发板上 Done 指示灯亮时,器件编程结束;

(14)通过控制拨动和按键开关的开闭来观察 LED(请参考前面的逻辑图)验证输出结果。

2. 开发板验证

首先,按住 clr(BTN1)不放,按 1 到 2 次 clk(BTN0),进行复位操作。然后,将 en(SW3)设置为高电平,设置输入数据 data_in[0~7] (Sw[0~7])和位移控制信号 set[0~3] (SW0~1),这里选择输入数据为 00110111,位移控制信号分别为 000,010,100,

111 进行验证;

Led[0~7]),验证移位寄存器功能是否正确。

set = 000 时,data_out 应为 00110111;set = 010 时,data_out 应为 11001101;set = 100 时,data_out 应为 01110011;set = 111 时,data_out 应为 01101110;

通过验证结果证明该 8 位移位寄存器符合设计的要求。