FPGA 之 SOPC 系列(四)NIOS II 外围设备--标准系统搭建

今天给大侠带来今天带来FPGA 之 SOPC 系列第四篇,NIOS II 外围设备--标准系统搭建,希望对各位大侠的学习有参考价值,话不多说,上货。

![]()

本篇主要以一个标准硬件平台的搭建为例,介绍了Nios II处理器常用外围设备(Peripherals)内核的特点、配置,供读者在使用这些外设定制Nios II系统时查阅。这些外设都是以IP核的形式提供给用户的,用户可以根据实际需要把这些IP核集成到Nios II系统中去。

主要介绍:硬件结构;内核的特性核接口;SOPC Builder中各内核的配置选项。

以下为本篇的目录简介:

4.1 并行输入/输出(PIO)内核

4.2 SDRAM控制器内核

4.3 ram/rom片上存储

4.4 EPCS控制器内核

4.5 定时器内核

4.6 UART内核

4.7 JTAG_UART内核

4.8 lcd控制器

4.9 System ID内核

4.10 实战训练

![]()

4.1 并行输入/输出(PIO)内核

+

并行输入/输出内核(PIO内核①)提供Avalon从控制器端口和通用I/O口②间的存储器映射接口。PIO内核提供简单的I/O访问用户逻辑或外部设备,例如:

-

控制LED

-

读取开关量

-

控制显示设备

-

配置并且与片外设备通信

说明:

SOPC Builder中提供了PIO内核,可以很容易将PIO内核集成到SOPC Builder生成的系统中。

通用I/O端口既连接到片内逻辑又连接到外部设备的FPGA I/O管脚。

PIO内核简介

每个Avalon接口的PIO内核可提供32个I/O端口且端口数可设置,用户可以添加一个或多个PIO内核。CPU通过I/O寄存器控制I/O端口的行为。I/O口可以配置为输入、输出和三态,还可以用来检测电平事件和边沿事件。

PIO内核结构框图

PIO内核寄存器描述:

注:

① 该寄存器是否存在取决于硬件的配置。如果该寄存器不存在,那么读寄存器将返回未定义的值,写寄存器无效。该寄存器是否存在取决于硬件的配置。如果该寄存器不存在,那么读寄存器将返回未定义的值,写寄存器无效。

② 写任意值到边沿捕获寄存器将清除所有位为0。

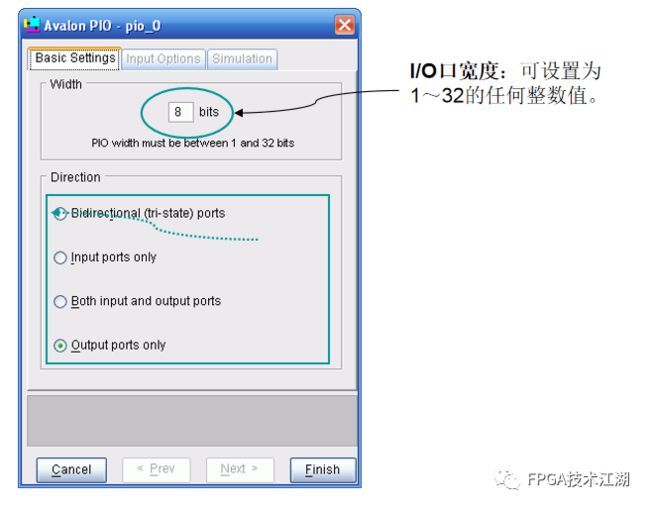

PIO内核配置选项操作如下:

Basic Settings 选项卡:

各个端口描述:

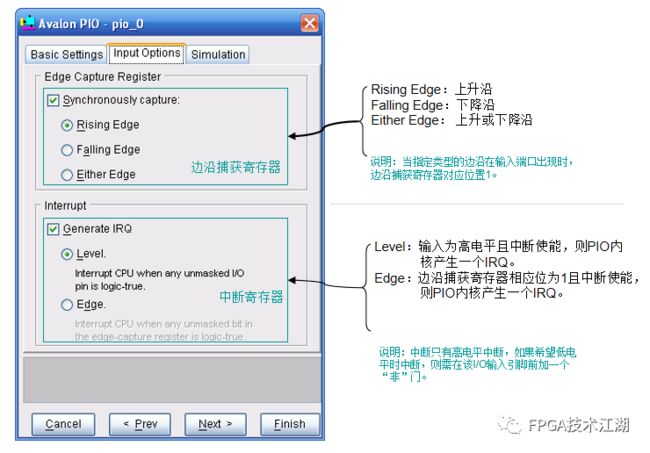

Input Options 选项卡:

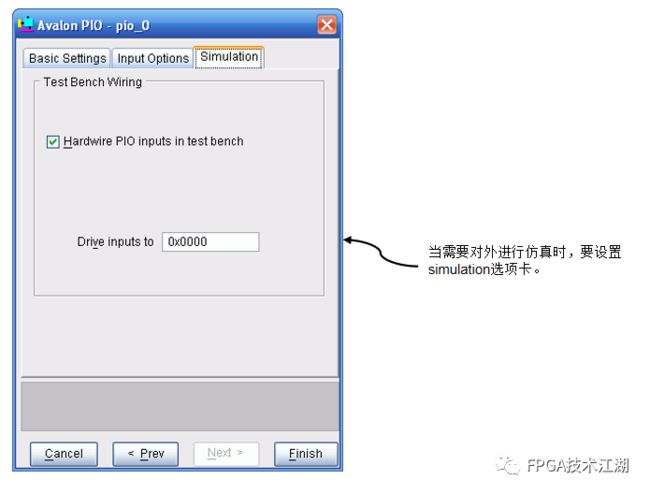

Simulation 选项卡:

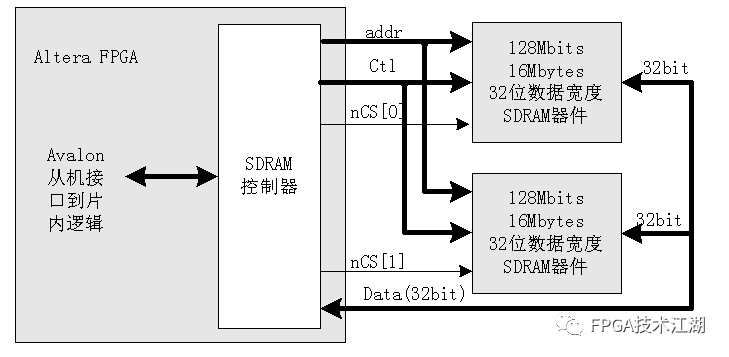

4.2 SDRAM控制器内核

+

-

SDRAM控制器内核概述

SDRAM控制器内核提供一个连接片外SDRAM芯片的Avalon接口,并可以同时连接多个SDRAM芯片。

SDRAM控制器内核具有不同数据宽度(8、16、32或64位)、不同内存容量和多片选择等设置。

SDRAM控制器不支持禁能的时钟模式。SDRAM控制器使cke引脚永久地有效。

PPL(片内锁相环):通常用于调整SDRAM控制器内核与SDRAM芯片之间的相位差。

Avalon三态桥:SDRAM控制器可与现有三态桥共用引脚,这能减少I/O引脚使用,但将降低性能。

fMAX(最高时钟频率):目标FPGA的系列和整个硬件设计都会影响硬件设计可实现的最高时钟频率。

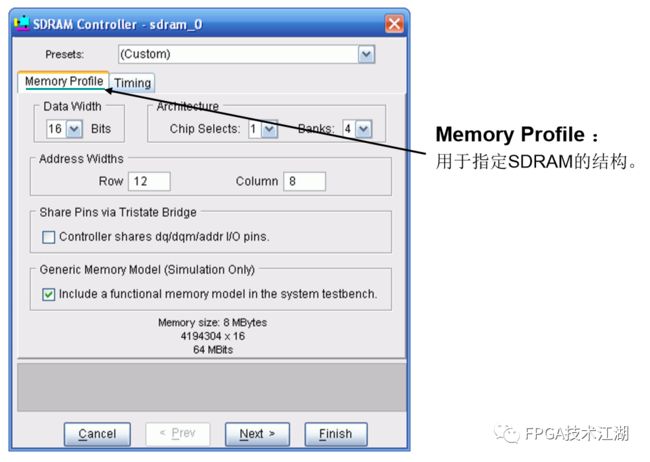

SDRAM内核配置选项操作如下:

SDRAM芯片型号:

Memory Profile:

数据宽度:

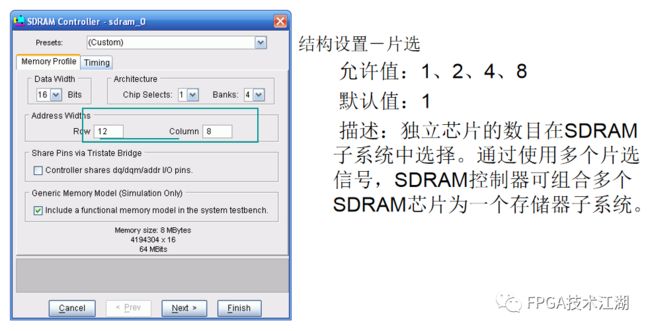

结构设置--片选:

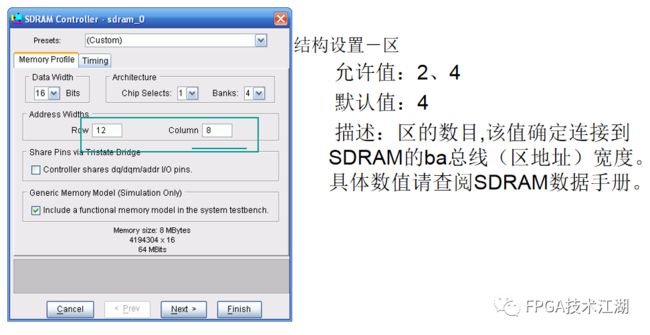

结构设置--区:

地址宽度设计--行:

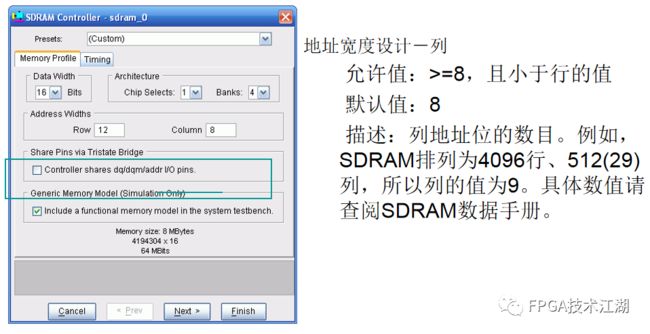

地址宽度设计--列:

通过三态桥共用管脚:

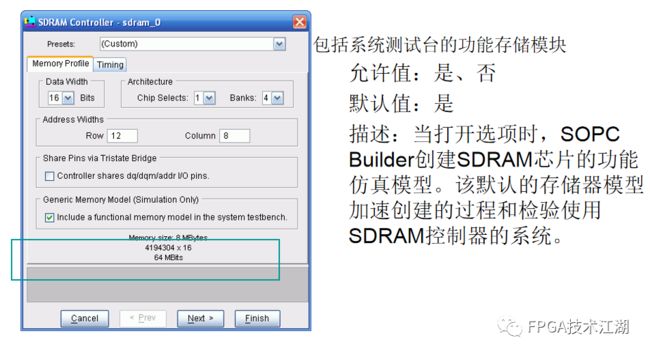

包括系统测试台的功能存储模块:

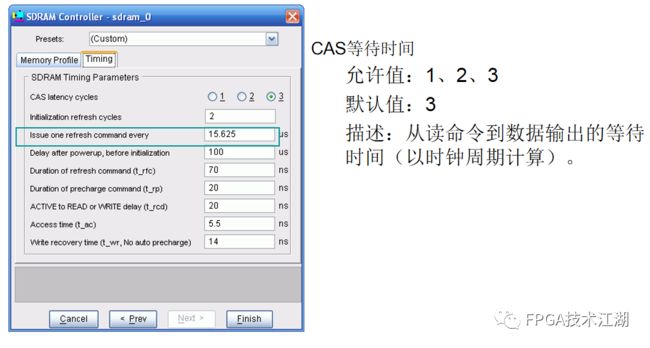

Timing:

CAS等待时间:

初始化刷新周期:

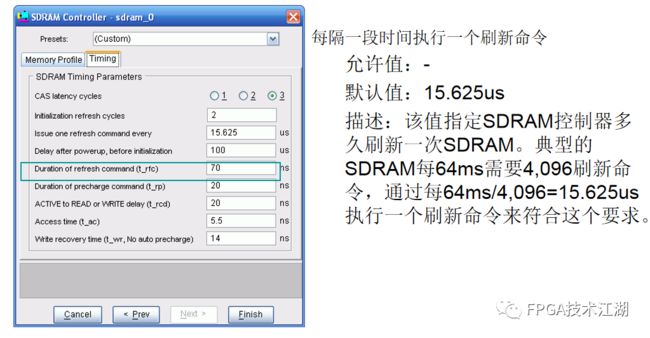

每隔一段时间执行一个刷新命令:

在初始化前、上电后延时:

刷新命令(t_rfc)的持续时间:

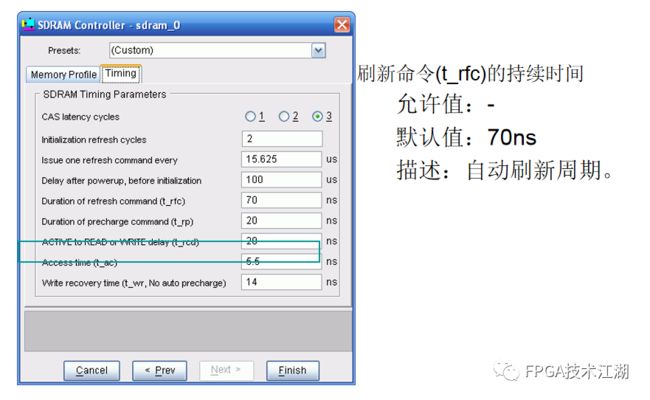

预充电命令(t_rp)的持续时间:

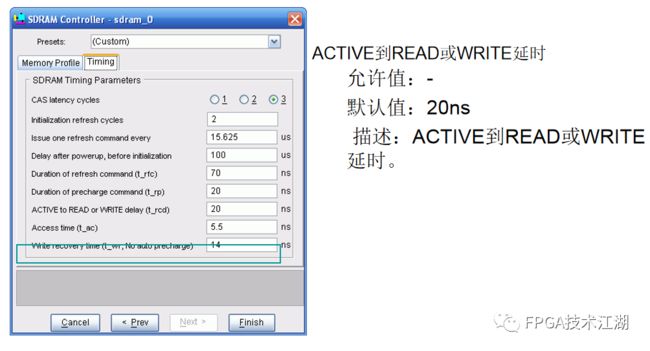

ACTIVE到READ或WRITE延时:

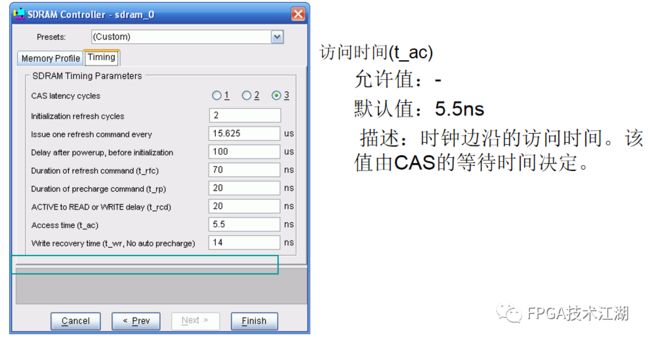

访问时间(t_ac):

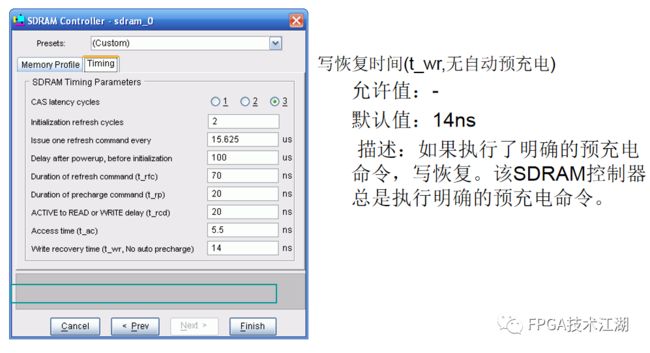

写恢复时间(t_wr,无自动预充电):

-

SDRAM应用

一个带32位数据总线的128Mbit SDRAM芯片:

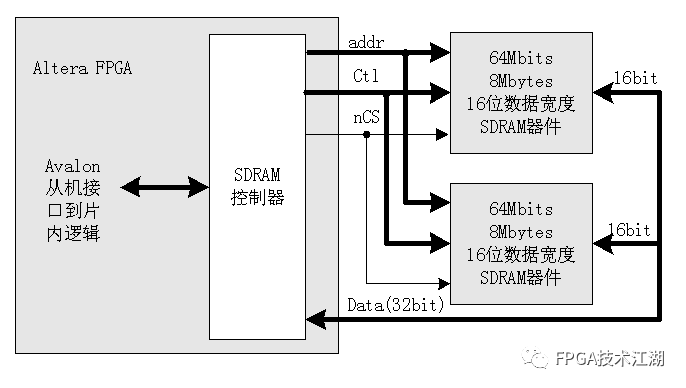

两个带16位数据总线的64Mbit SDRAM芯片:

两个带32位数据总线的128Mbit SDRAM芯片:

-

添加外部sdram

-

通常的系统都需要用户指定一个空间,这个是指ram可以使片上的,也可以使片外的sdram或sram等。如果用户程序较大,超出了所能定制的最大片上ram容量,则也可以将程序放在sdram中运行。

4.3 ram/rom片上存储

+

使用FPGA内部RAM资源,可以构成RAM或ROM,速度快,特别在调试时因为很少受外部连线等因素的限制很有用。组件栏中选择Legacy Components->On-Chip Memory打开界面,如图:

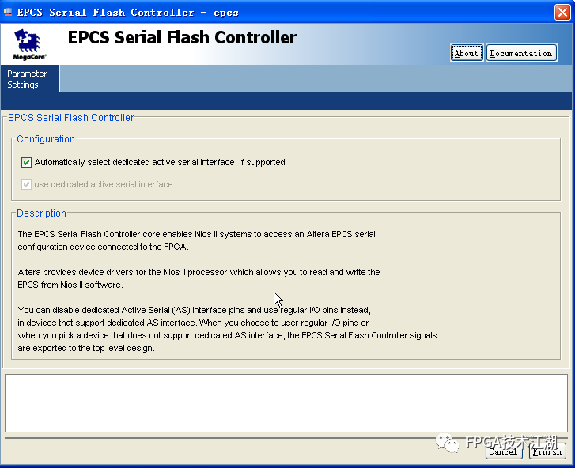

4.4 EPCS控制器内核

+

EPCS控制器内核综述

Altera EPCS 串行配置器件(EPCS1和EPCS4),它可用于存储程序代码、非易失性程序数据和FPGA配置数据。

带Avalon接口的EPCS设备控制器内核(“EPCS控制器”)允许NiosII系统访问Altera EPCS串行配置器件。Altera提供集成到NiosII硬件抽象层(HAL)系统库的驱动程序,允许用户使用HAL应用程序接口(API)来读取和编写EPCS器件。

EPCS控制器可用于:

-

在EPCS器件中存储程序代码。

-

存储非易失性数据。

-

管理FPGA配置数据。

EPCS控制器结构框图如下:

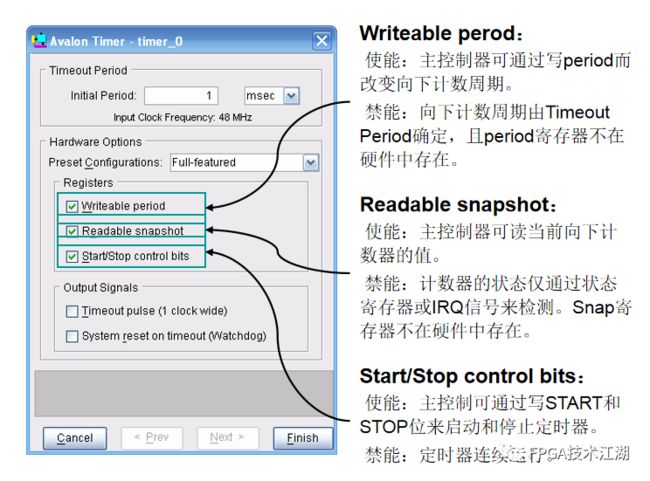

4.5 定时器内核

+

-

定时器内核综述:

定时器是挂载在Avanlon总线上的32位定时器,特性如下:

-

两种计数模式:单次减1和连续减1计数模式

-

定时器到达0时产生中断请求(IRQ);

-

可选择设定为看门狗定时器,计算到达0时复位系统;

-

可选择输出周期性脉冲,在定时器计算到达0时输出脉冲;

-

可由软件启动、停止或复位定时器;

-

可由软件使能或屏蔽定时器中断。

EPCS控制器结构框图如下:

EPCS控制器结构框图

-

定时器可进行的基本操作如下所述:

Avalon主控制器通过对控制寄存器执行不同的写操作来控制:

-

启动和停止定时器

-

使能/禁能IRQ

-

指定单次减1计数或连续减1计数模式

-

处理器读状态寄存器获取当前定时器的运行信息。

-

处理器可通过写数据到periodl和periodh寄存器来设定定时器周期。

-

定时器可进行的基本操作如下所述:

-

内部计数器计数减到0,立即从周期寄存器开始重新装载。

-

处理器可以通过写snapl或snaph获取计数器的当前值。

-

当计数器计数到达0时:

-

如果IRQ被使能,则产生一个IRQ

-

(可选的)脉冲发生器输出有效持续一个时钟周期

-

(可选的)看门狗输出复位系统

-

定时器寄存器描述:

EPCS控制器结构框图

注:*表示该位保留,读取值未定义。

-

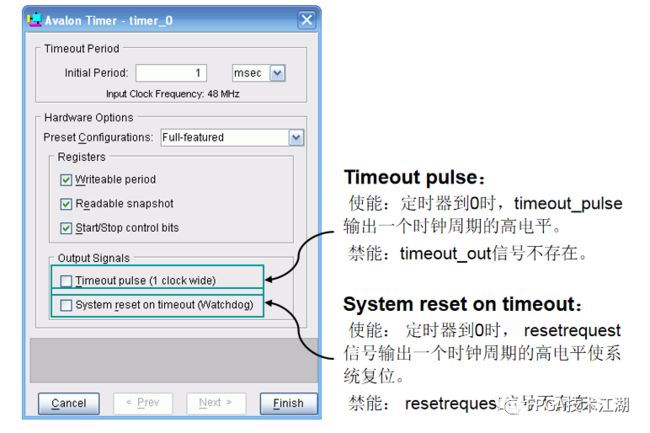

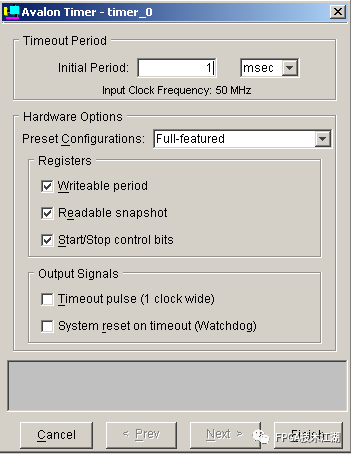

定时器内核配置选项操作如下:

CFI控制器框图如下:

Initial perod:

CFI控制器框图

Preset Configurations:

Writeable perod、Readable snapshot及Start/Stop control bits:

Timeout pulse 和 System reset on timeout:

在组件栏中双击选择Other->Interval timer进入配置界面,我们选用Full feature,1ms一次溢出事件。

4.6 UART内核

+

-

UART内核综述

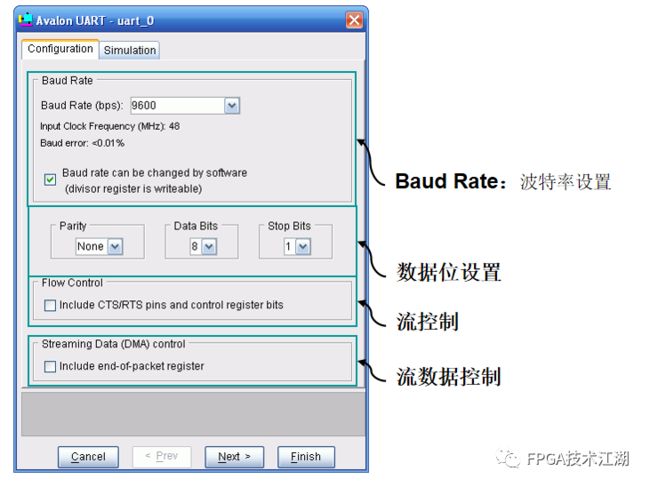

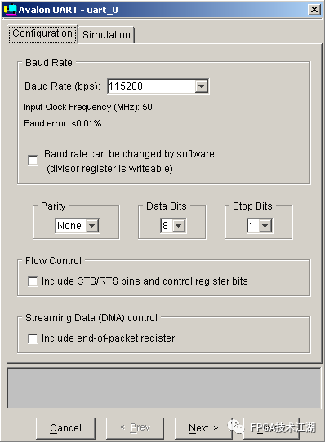

UART内核(通用异步接收器/发送器内核)执行RS-232协议时序,并提供可调整的波特率。用户可配置奇偶校验位、停止位和数据位,以及可选的RTS/CTS流控制信号。

内核提供一个简单的Avalon从控制器接口,该接口允许Avalon主控制器(例如NiosII处理器)通过读写寄存器与UART内核进行通讯。

UART内核的结构框图如下图所示:

UART内核的结构框图

-

RS-232接口

-

发送逻辑

-

接收逻辑

-

波特率生成

-

UART内核的寄存器描述:

UART内核寄存器映射

UART内核配置页:

在组件选择栏中选择Communication->UART(RS232 series port)配置UART:

4.7 JTAG_UART内核

+

-

JTAG_UART内核综述

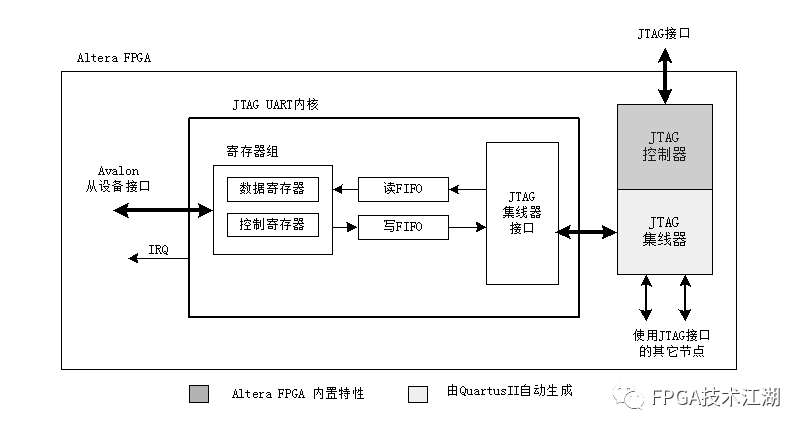

JTAG UART内核通过Avalon从控制器接口连接到Avalon总线。JTAG UART内核包含2个32位寄存器(数据和控制),它们可通过Avalon从控制器端口进行存取。Avalon主控制器访问寄存器来控制内核并在JTAG连接上传输数据。JTAG UART内核提供高电平有效的中断输出,该输出在读FIFO几乎为满或写FIFO几乎为空时申请一个中断。

有读写FIFO也是JTAG UART内核与UART内核的不同点之一。FIFO可以改善JTAG连接的带宽。FIFO深度可由用户设置。

UART内核寄存器映射

-

JTAG-UART配置选项卡:

在组件栏中选择Communication->JTAG UART,弹出JTAG UART配置界面如下:

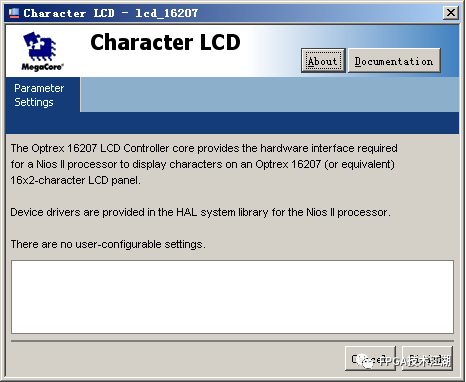

4.8 lcd控制器

+

The LCD controller core consists of two user-visible components:

-

Eleven signals that connect to pins on the Optrex 16207 LCD panel—These signals are defined in the Optrex 16207 data sheet.

-

E—Enable (output)

-

RS—Register Select (output)

-

R/W—Read or Write (output)

-

DB0 through DB7—Data Bus (bidirectional)

-

An Avalon Memory-Mapped (Avalon-MM) slave interface that provides access to 4 registers.

使用标准16027字符型液晶显示器,在display->character lcd,如图:

4.9 System ID内核

+

System ID寄存器描述:

系统ID内核提供只读的Avalon从控制器接口。

系统ID内核寄存器映射

使用系统ID内核有两种基本的方法:

-

其一,在下载新的软件到系统之前验证系统ID。

-

其二,复位后检查系统ID。

添加SYSTEM ID:

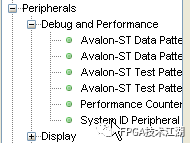

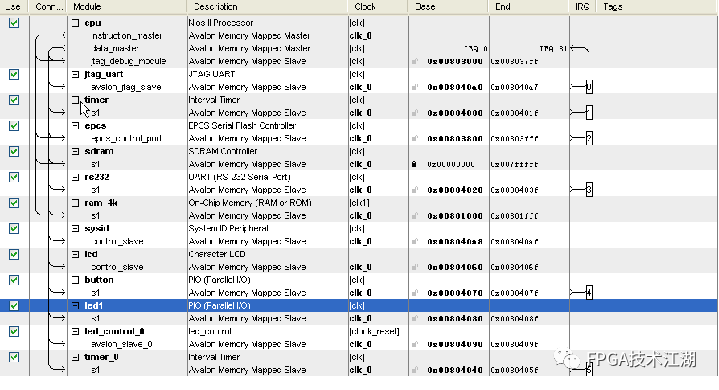

4.10 实战训练

+

完成一个包含以下外设的标准硬件平台:

-

PIO(BUTTON、LED)

-

Sdram

-

片上存储

-

EPCS

-

定时器

-

UART内核

-

JTAG_UART内核

-

lcd控制器

-

System ID内核

实现步骤:

-

建立工程

-

添加NIOS系统(nios选择E型)

-

添加系统到工程

-

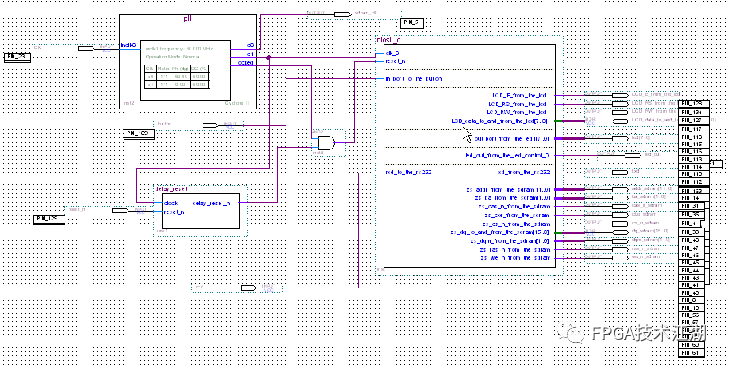

配置管脚综合

系统结果:

平台结果:

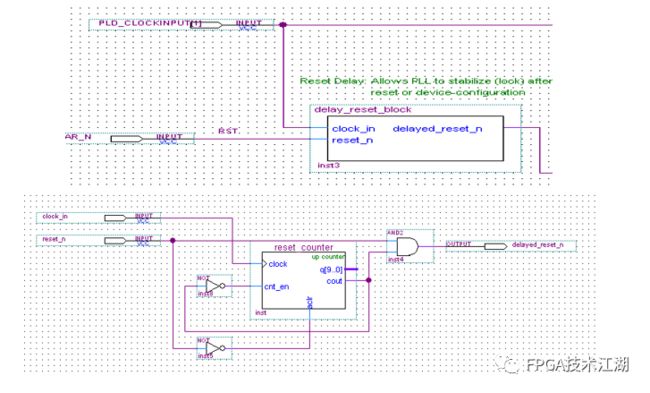

注意这里有一个复位延时模块,如下所示:

![]()

FPGA 之 SOPC 系列第四篇就到这里结束,下一篇将带来第五篇,Nios II软件使用与程序开发(一)等相关内容。各位大侠,明天见!