- 数据的流动——计算机是如何显示一个像素的

一尾66

基础知识图形渲染其他

在计算机内部是怎么把一张照片显示到屏幕上的呢?对于这个问题一直很好奇,这应该是也是图形学的一个最基础的问题吧。没上过计算机组成原理课,只好自行百度谷歌~发现网上的答案大多不完整,前段时间顺着问题一直搜索,从计算机的发明到显示器成像后来又到了电路,后来甚至工业革命的发展史,根本停不下来,有了一个主题后看历史也是真挺有意思的。在这里将我的理解大概记下来,不求细节精确,只求完整易懂。一个从编程/输入设备

- 计算机组成原理:总线技术深度解析

努力编程的阿伟

网络计算机组成

目录1.总线技术概述1.1什么是总线?1.2总线的基本功能2.总线的类型2.1内部总线2.2外部总线3.总线的标准与协议3.1常见的总线标准3.2总线协议4.总线的性能考量4.1带宽4.2延迟4.3可扩展性5.总线的未来趋势6.结语在计算机科学的浩瀚宇宙中,总线技术扮演着至关重要的角色。它是连接计算机硬件组件的神经网络,负责协调数据、指令和电源的流动。今天,我们将深入探讨总线的概念、类型、标准以及

- 计算机组成原理ioe,1614010102曹妍计算机组成原理实验报告7

weixin_39918145

计算机组成原理ioe

1614010102曹妍计算机组成原理实验报告7(6页)本资源提供全文预览,点击全文预览即可全文预览,如果喜欢文档就下载吧,查找使用更方便哦!9.9积分哈余虞理工大学钦件与微电子学院实验报告(2017-2018第一学期)课程名称:班级:学号:姓名:实验名称CPU与存储器的连接V业软件工程姓名曹妍学号1614010102班级软件16-1班一、实验目的:1.模拟一台完整的计算机,了解计算机硕件设计过程

- 电脑操作从零到精通:全方位入门资源包

马屿人

本文还有配套的精品资源,点击获取简介:电脑快速入门资源下载提供了一系列教程,帮助初学者迅速掌握计算机基础知识和操作技能。教程涵盖了计算机组成部分、操作系统选择、文件管理、网络连接、办公软件应用、安全与维护、进阶技能等关键领域。资源包括详细的《电脑快速入门.PDF》教程和《***说明.txt》,初学者可借此逐步提升电脑操作技能,适应数字世界。1.计算机基础知识和组成部分1.1计算机硬件与软件概述计算

- 华东理工815计算机真题百度云,华东理工大学计算机815专业课介绍 (1).pdf

weixin_39942785

华东理工815计算机真题百度云

华东理工大学计算机815专业课介绍1,招生专业(1)计算机科学与技术(学硕)(2)计算机技术(专硕)(3)软件工程(非全)2,考试科目华理计算机专硕学硕非全都是:数一英一815计算机专业基础综合815计算机专业基础综合包括:1数据结构2操作系统3计算机组成与设计参考书目:407233425群研3,历年分数线考计算机技术计算机科学与技术机20202693212019302302算2018260318

- 计算机组成原理2——一个字是多少字节(切忌默认为一个字等于2字节

蓝莓味柯基

一个字等于多少个字节,与系统硬件(总线、cpu命令字位数等)有关,不应该毫无前提地说一个字等于多少位。正确的说法:①:1字节(byte)=8位(bit)②:在16位的系统中(比如8086微机)1字(word)=2字节(byte)=16(bit)在32位的系统中(比如win32)1字(word)=4字节(byte)=32(bit)在64位的系统中(比如win64)1字(word)=8字节(byte)

- 计算机组成原理01

XXXJessie

计算机组成原理笔记

第一章计算机系统概述1.1本章大纲要求与核心考点1.1.1大纲内容(一)计算机系统层次结构计算机系统的基本组成计算机硬件的基本结构计算机软件和硬件的关系计算机系统的工作原理“存储程序"工作方式,高级语言程序与机器语言程序之间的转换,程序和指令的执行过程。(二)计算机性能指标吞吐量、响应时间;CPU时钟周期、主频、CPI、CPU执行时间;MIPS、MFLOPS、GFLOPS、TFLOPS、PFLOP

- 计算机组成原理02

XXXJessie

计算机组成原理笔记

1.3计算机系统的层次结构1.3.1计算机系统的基本组成(一)计算机硬件冯·诺依曼计算机冯·诺依曼在研究EDVAC计算机时提出了“存储程序”的概念,“存储程序”的思想奠定了现代计算机的基本结构,以此概念为基础的各类计算机通称为冯•诺依曼计算机,其特点如下:采用“存储程序”的工作方式。计算机硬件系统由运算器、存储器、控制器、输入设备和输出设备5大部件组成。指令和数据以同等地位存储在存储器中,形式上没

- 【计算机组成原理】3.2.1 SRAM和DRAM

Skywalker玄默冲虚

考研学习方法面试

3.2.1SRAM和DRAM00:00各位同学大家好,在上个小节中我们认识了存储芯片的基本原理,如何存储二进制的0和1,如何根据一个地址来访问某一个存储字,这是上一小节学习的内容。在这个小节当中我们会介绍两种特定类型的存储芯片,一种叫SRAM(StaticRandomAccessMemory),一种叫DRAM(DynamicRandomAccessMemory)。之前我们提到过RAM这个缩写,它指

- 我的大二上

龙渊客

这一学期结束了,今天晚上就回家自己盘一下这学期的得失:学习上:计算机网络、计算机组成原理、数据库、线性代数、马克思原理基本概述、大学物理二都来了,感觉这一学期的任务是比上一学期加大,且沉重的。这些课程,要么专业课,要么必修课,自己认为对于这些课程,我并没有丝毫的放松,基本上都能全力以赴。但有些东西,还是我不能及的。有些人能在一周之内学完所有课程,耗费的是休息时间和取消平时的享乐。我则是慢热行的,慢

- 【计算机组成原理】2.3.2 浮点数的加减运算

Skywalker玄默冲虚

考研学习方法面试

2.3.2浮点数的加减运算00:00各位同学大家好。通过之前几个小节的学习,我们已经知道了浮点数在计算机里边如何表示,它的表示规则是什么。那基于浮点数的这个表示规则和原理,又要如何实现浮点数的运算呢?所以这个小节我们要探讨的是浮点数如何实现加减运算。除了加减运算的实现之外,我们还会探讨浮点数还有定点数之间的一个强制类型转换的问题。00:24好,首先来看加减运算怎么实现,分为这样的几个步骤,对阶、尾

- 【计算机组成原理】2.3.1_1 浮点数的表示

Skywalker玄默冲虚

考研面试学习方法

2.3.1_1浮点数的表示00:00各位同学大家好。通过之前几个小节的学习,我们已经知道了定点数怎么在计算机里表示,包括定点整数和定点小数。从这个小节开始,我们要学习浮点数在计算机里的表示和运算。这个小节中我们先介绍浮点数如何表示,我们会介绍浮点数它有什么作用,还有一个基本的原理。另外考试中常考的一个问题是浮点数的规格化,之后我们还会简单的介绍浮点数的表示范围相关的问题,这方面的内容其实已经从考研

- SOC学习历程概述

weixin_30376509

操作系统嵌入式运维

从开始接触soc到现在大概有两年半左右的时间了,经历了ORSOC到minsoc再到mkg-soc的搭建,以及现在的大小核系统的搭建首先先讲下学习的前期需要具备的知识,前面3点是必须,后面3点可以中间学习的过程再学习。之所以有这些要求主要是以防中间的学习过程中,有些东西看不懂而走弯路。学习的前期准备:1、学过数电,有一定的电路基础。2、熟练掌握verilog语言。3、对于计算机组成原理,体系结构有一

- 计算机组成原理数据的表示和运算,计算机组成原理 No4 数据的表示和运算

朝辞暮归

《计算机组成原理No4数据的表示和运算》由会员分享,可在线阅读,更多相关《计算机组成原理No4数据的表示和运算(39页珍藏版)》请在人人文库网上搜索。1、计算机组成原理,PrinciplesofComputerComposition,2,第二部分数据的表示和运算,2.1数制与编码2.2定点数表示和运算2.3浮点数表示和运算2.4算术逻辑单元ALU,3,2.2定点数表示和运算,2.2.1定点数的表示

- 【计算机组成原理】2.2.1_4 算数逻辑单元ALU

Skywalker玄默冲虚

考研学习方法面试

2.2.1_4算数逻辑单元ALU00:00各位同学大家好,在这个视频中我们会学习什么是算术逻辑单元ALU。首先我们会介绍ALU在计算机内部的一个作用,以及它需要支持哪些功能。紧接着我们会介绍ALU具体的实现原理,当然这个部分简要了解即可,考试不太可能考它的实现原理。最后我们会教大家怎么看懂ALU的图示。在考研真题当中有可能会给大家一个电路图作为题目的信息,在电路图当中可能会包含ALU这个部件。00

- 计算机组成原理—运算器

ITS_Oaij

考研

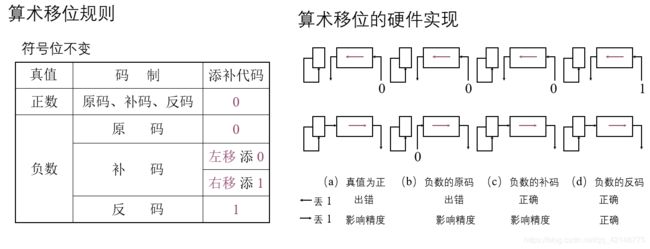

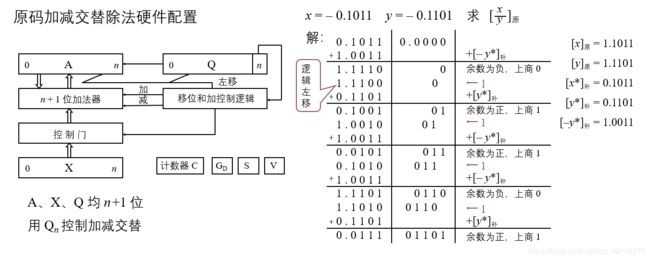

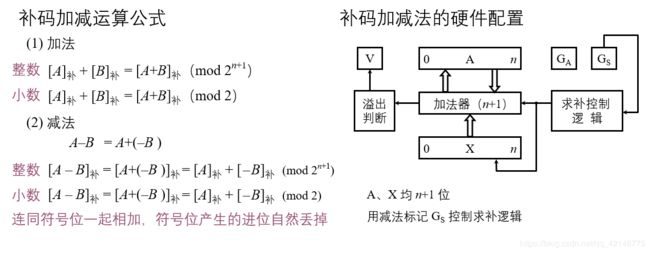

第二章数据的表示和运算2.1数制与编码2.1.1进位计数制及其相互转换2.1.2*BCD编码2.1.3定点数的编码表示⚫️定点数VS浮点数⚫️无符号数的表示⚫️有符号数的表示(原码、反码、补码、移码)⚫️原码、反码、补码、移码的作用2.1.4整数的表示2.2运算方法和运算电路2.2.1基本运算部件⚫️一位全加器⚫️串行进位加法器⚫️并行进位加法器⚫️算数逻辑单元ALU2.2.2定点数的移位运算⚫️

- 【计算机组成原理】2.2.2 定点数的移位运算

Skywalker玄默冲虚

考研学习方法面试

2.2.2定点数的移位运算00:00这一小节中我们来学习定点数的移位运算怎么实现。移位运算又可以进一步的划分为算术移位、逻辑移位还有循环移位。我们会按从上至下的顺序依次讲解。00:13好,首先来认识一下什么叫做算术移位。我们从大家熟悉的十进制数出发,假设这儿有这样的一个十进制数985.211,那么我们从小经常做的一个事情是让小数点后移一位或者后移两位,那小数点每后移一位相当于我们对整个数值乘以了一

- 山东大学计算机组成原理实验4移位器(含原理图,引脚分配,实验结果输入输出)

Star223333

计算机组成原理山东大学计算机组成原理计算机组成与设计实验移位器

实验内容及说明本实验要求采用传送方式实现二进制数的移位电路。图4给出了可对四位二进制数实现左移1位(×2),右移1位(÷2)和直接传送功能的移位线路,这也是运算器的主要功能。在LM(左移)的控制下可实现左移1位,空位补0。在RM(右移)的控制下可实现右移1位,空位补0。在DM(直送)的控制下可实现直接传送。实验步骤(1)用图形输入法完成图4逻辑电路输入。图4移位器电路原理图(2)管脚锁定:平台工作

- 408-计算机组成原理-注意点

猫毛已经快要掉光的小猫

系统架构

数据的表示IEEE754标准的特殊情况:阶码全为0,尾数不全为0表示非规格化的数值,0.M×2^(-126)阶码全为0,尾数也全为0,表示±0阶码全为1,尾数全为0,表示正负无穷大阶码全为1,尾数不全为0,表示非数符Nan存储器Cache:多少组相联指的是一组有多少个。LRU标记为一组有n个,就需要用logn表示区分计算cache数据区与cache容量,cache容量需要包括标志位。标志位大体包括

- 计算机组成原理 第三章(存储器)—第一节(概述)

Zevalin爱灰灰

计算机组成原理笔记计算机组成原理

写在前面:本系列笔记主要以《计算机组成原理(唐朔飞)》为参考,大部分内容出于此书,笔者的工作主要是挑其重点展示,另外配合下方视频链接的教程展开思路,在笔记中一些比较难懂的地方加以自己的一点点理解(重点基本都会有标注,没有任何标注的难懂文字应该是笔者因为强迫症而加进来的,可选择性地忽略)。视频链接:计算机组成原理(哈工大刘宏伟)135讲(全)高清_哔哩哔哩_bilibili一、存储器的功能存储器是计

- 分布式概念

独木人生

后端分布式

分布式是一种计算机系统架构,它由多台计算机组成,这些计算机通过网络互相连接并协作工作。在分布式系统中,不同的计算机被称为节点,它们通过消息传递或者远程过程调用等方式进行通信和协作,共同完成任务。这种方式可以使得系统具有更高的性能和可靠性。分布式系统的特点包括:可扩展性:可以通过增加更多的节点来扩展系统的处理能力。高可用性:当一个节点发生故障时,其他节点可以继续工作,保证系统的可用性。容错性:系统可

- 【软考中级备考笔记】数据的表示和校验码

lyx7762

软考软考

2024/2/18–数据的表示和校验码天气:阴雨春节假期结束后第一个工作日,开始备考中级软件工程师。希望在今年5月底的软考中取得中级证书视频地址:https://www.bilibili.com/video/BV1Qc411G7fB1.计算机的总体架构从下图中可以看出,计算机中包含了一下三个层次最底层的为计算机的硬件部分,对应的知识主要是计算机组成原理其次是操作系统这一个最大的系统软件,对应了操作

- 软考中级软件设计笔记

HoPE_st

设计模式软件工程网络程序人生

为备考2022上半年软考所做的笔记,祝愿自己顺利通过!软考笔记知识点速记操作系统1.CUP中的寄存器2.中断&DMA3.系统可靠地计算4.存储器4.1Cache4.2存储器划分4.3存储器构成5.页面逻辑地址&物理地址6.指令6.1流水线和吞吐率6.2指令寻址7.移臂调度算法8.总线基础知识9.PV操作、信号量计算机组成原理1.逻辑运算2数据校验2.1海明码&海明校验2.2循环冗余校验3.浮点数运

- 世界顶级名校计算机专业,都在用哪些书当教材?(文末送书)

小尘要自信

java开发语言数据库算法赠书计算机组成

目录01《深入理解计算机系统》02《算法导论》03《计算机程序的构造和解释》04《数据库系统概念》05《计算机组成与设计:硬件/软件接口》06《离散数学及其应用》07《组合数学》08《斯坦福算法博弈论二十讲》参与规则清华、北大、MIT、CMU、斯坦福的学霸们在新学期里要学什么?今天我们来盘点一下那些世界名校计算机专业采用的教材。01《深入理解计算机系统》原书第3版)作者:兰德尔E.布莱恩特大卫R.

- 软考学习--计算机组成原理与体系结构

CYing丶

学习软件设计师

计算机组成原理与体系结构数据的表示进制转换R进制转换为10进制–按权展开法10进制转换为2进制原码反码补码移码原码:数字的二进制表示反码:正数的反码等于原码,负数的反码等于原码取反补码:正数的补码等于原码,负数的补码等于原码取反+1移码:浮点运算中的阶,最高位取反浮点数运算浮点数表示:N=M*Rⁿ(科学计数法)M为尾数,R为基数,n为指数对阶->尾数运算=>结果格式化计算机结构Flynn分类法计算

- 浅谈分布式缓存解决方案!

肥肥技术宅

java缓存分布式java

接口高并发的解决思路:加缓存数据静态化集群分布式同步转异步限流、降级适合加缓存的场景:读多写少的数据,不经常需要修改的数据、一致性要求不高(数据只能保持最终一致性,不能保证数据同步一致性)缓存的概念1)外存外存储器是指除计算机内存及CPU缓存以外的存储器,断电后仍然能保存数据。常用的有硬盘、u盘等。2)内存内存是计算机组成部分。被称为内存存储器,其作用是暂时存放CPU运算数据,以及与外存之间交互的

- 计算机组成原理 2 数据表示

Sanchez·J

计算机组成原理电脑

机器数研究机器内的数据表示,目的在于组织数据,方便计算机硬件直接使用。需要考虑:支持的数据类型;能表示的数据精度;是否有利于软件的移植能表示的数据范围;存储和处理的代价;...真值:符号用“+”、“-”表示的数据表示方法。机器数:符号数值化的数据表示方法,用0、1表示符号。三种常见的机器数:(设定点数的形式为)原码表示简单运算复杂:符号位不参加运算,要设置加法、减法器。0的表示不唯一[X]原+[Y

- 《计算机组成与设计 RSIC-V版》阅读笔记——计算机抽象及相关技术

hhh_YangGe

RSIC-V架构

第一章:计算机抽象及相关技术介绍相关概念和定义;介绍软件和硬件的组成部分;介绍如何评估性能和功耗;介绍技术发展方向;打基础似的一章引言:计算应用分类个人计算机PC-->个人移动设备(PerisonalMobileDevice,PMD)服务器(更强调可靠性,故障的代价高)-->云计算(软件即服务,SaaS)嵌入式计算机(特定的需求,通常人们对故障的容忍度较低)软件开发思维:减少程序占用的内容空间以加

- 《计算机组成与设计 RSIC-V版》阅读笔记——前言、目录

hhh_YangGe

RSIC-V架构

前言阅读重点展示硬件和软件之间的关系,并关注现代计算机的基本概念做硬件的人,设计出更适合跑软件的硬件做软件的人,设计出更适应硬件的软件把程序改造成并行的。让程序员尽可能不知道他们正在使用的底层硬件的并行属性?导读方案(这还蛮好的,可惜正文小标题上没有单独标记推荐阅读方式)

- 180天Linux小白到大神-Linux快速入门

给小李三分薄面

Linux小白成长之路linux运维运维开发定时任务

01.Linux快速入门01.Linux快速入门1.计算机组成原理1.1什么是计算机1.2为什么要有计算机1.3计算机五大组成部分1.3.1CPU1.3.2内存/硬盘1.3.3输入设备1.3.4输出设备1.3.5五大组件总结1.4计算机三大核心硬件1.5操作系统基本概念1.5.1操作系统由来1.5.2什么是操作系统1.5.3为什么需要操作系统2.Linux系统基本介绍2.1什么是Linux2.2L

- JVM StackMapTable 属性的作用及理解

lijingyao8206

jvm字节码Class文件StackMapTable

在Java 6版本之后JVM引入了栈图(Stack Map Table)概念。为了提高验证过程的效率,在字节码规范中添加了Stack Map Table属性,以下简称栈图,其方法的code属性中存储了局部变量和操作数的类型验证以及字节码的偏移量。也就是一个method需要且仅对应一个Stack Map Table。在Java 7版

- 回调函数调用方法

百合不是茶

java

最近在看大神写的代码时,.发现其中使用了很多的回调 ,以前只是在学习的时候经常用到 ,现在写个笔记 记录一下

代码很简单:

MainDemo :调用方法 得到方法的返回结果

- [时间机器]制造时间机器需要一些材料

comsci

制造

根据我的计算和推测,要完全实现制造一台时间机器,需要某些我们这个世界不存在的物质

和材料...

甚至可以这样说,这种材料和物质,我们在反应堆中也无法获得......

- 开口埋怨不如闭口做事

邓集海

邓集海 做人 做事 工作

“开口埋怨,不如闭口做事。”不是名人名言,而是一个普通父亲对儿子的训导。但是,因为这句训导,这位普通父亲却造就了一个名人儿子。这位普通父亲造就的名人儿子,叫张明正。 张明正出身贫寒,读书时成绩差,常挨老师批评。高中毕业,张明正连普通大学的分数线都没上。高考成绩出来后,平时开口怨这怨那的张明正,不从自身找原因,而是不停地埋怨自己家庭条件不好、埋怨父母没有给他创造良好的学习环境。

- jQuery插件开发全解析,类级别与对象级别开发

IT独行者

jquery开发插件 函数

jQuery插件的开发包括两种: 一种是类级别的插件开发,即给

jQuery添加新的全局函数,相当于给

jQuery类本身添加方法。

jQuery的全局函数就是属于

jQuery命名空间的函数,另一种是对象级别的插件开发,即给

jQuery对象添加方法。下面就两种函数的开发做详细的说明。

1

、类级别的插件开发 类级别的插件开发最直接的理解就是给jQuer

- Rome解析Rss

413277409

Rome解析Rss

import java.net.URL;

import java.util.List;

import org.junit.Test;

import com.sun.syndication.feed.synd.SyndCategory;

import com.sun.syndication.feed.synd.S

- RSA加密解密

无量

加密解密rsa

RSA加密解密代码

代码有待整理

package com.tongbanjie.commons.util;

import java.security.Key;

import java.security.KeyFactory;

import java.security.KeyPair;

import java.security.KeyPairGenerat

- linux 软件安装遇到的问题

aichenglong

linux遇到的问题ftp

1 ftp配置中遇到的问题

500 OOPS: cannot change directory

出现该问题的原因:是SELinux安装机制的问题.只要disable SELinux就可以了

修改方法:1 修改/etc/selinux/config 中SELINUX=disabled

2 source /etc

- 面试心得

alafqq

面试

最近面试了好几家公司。记录下;

支付宝,面试我的人胖胖的,看着人挺好的;博彦外包的职位,面试失败;

阿里金融,面试官人也挺和善,只不过我让他吐血了。。。

由于印象比较深,记录下;

1,自我介绍

2,说下八种基本类型;(算上string。楼主才答了3种,哈哈,string其实不是基本类型,是引用类型)

3,什么是包装类,包装类的优点;

4,平时看过什么书?NND,什么书都没看过。。照样

- java的多态性探讨

百合不是茶

java

java的多态性是指main方法在调用属性的时候类可以对这一属性做出反应的情况

//package 1;

class A{

public void test(){

System.out.println("A");

}

}

class D extends A{

public void test(){

S

- 网络编程基础篇之JavaScript-学习笔记

bijian1013

JavaScript

1.documentWrite

<html>

<head>

<script language="JavaScript">

document.write("这是电脑网络学校");

document.close();

</script>

</h

- 探索JUnit4扩展:深入Rule

bijian1013

JUnitRule单元测试

本文将进一步探究Rule的应用,展示如何使用Rule来替代@BeforeClass,@AfterClass,@Before和@After的功能。

在上一篇中提到,可以使用Rule替代现有的大部分Runner扩展,而且也不提倡对Runner中的withBefores(),withAfte

- [CSS]CSS浮动十五条规则

bit1129

css

这些浮动规则,主要是参考CSS权威指南关于浮动规则的总结,然后添加一些简单的例子以验证和理解这些规则。

1. 所有的页面元素都可以浮动 2. 一个元素浮动后,会成为块级元素,比如<span>,a, strong等都会变成块级元素 3.一个元素左浮动,会向最近的块级父元素的左上角移动,直到浮动元素的左外边界碰到块级父元素的左内边界;如果这个块级父元素已经有浮动元素停靠了

- 【Kafka六】Kafka Producer和Consumer多Broker、多Partition场景

bit1129

partition

0.Kafka服务器配置

3个broker

1个topic,6个partition,副本因子是2

2个consumer,每个consumer三个线程并发读取

1. Producer

package kafka.examples.multibrokers.producers;

import java.util.Properties;

import java.util.

- zabbix_agentd.conf配置文件详解

ronin47

zabbix 配置文件

Aliaskey的别名,例如 Alias=ttlsa.userid:vfs.file.regexp[/etc/passwd,^ttlsa:.:([0-9]+),,,,\1], 或者ttlsa的用户ID。你可以使用key:vfs.file.regexp[/etc/passwd,^ttlsa:.: ([0-9]+),,,,\1],也可以使用ttlsa.userid。备注: 别名不能重复,但是可以有多个

- java--19.用矩阵求Fibonacci数列的第N项

bylijinnan

fibonacci

参考了网上的思路,写了个Java版的:

public class Fibonacci {

final static int[] A={1,1,1,0};

public static void main(String[] args) {

int n=7;

for(int i=0;i<=n;i++){

int f=fibonac

- Netty源码学习-LengthFieldBasedFrameDecoder

bylijinnan

javanetty

先看看LengthFieldBasedFrameDecoder的官方API

http://docs.jboss.org/netty/3.1/api/org/jboss/netty/handler/codec/frame/LengthFieldBasedFrameDecoder.html

API举例说明了LengthFieldBasedFrameDecoder的解析机制,如下:

实

- AES加密解密

chicony

加密解密

AES加解密算法,使用Base64做转码以及辅助加密:

package com.wintv.common;

import javax.crypto.Cipher;

import javax.crypto.spec.IvParameterSpec;

import javax.crypto.spec.SecretKeySpec;

import sun.misc.BASE64Decod

- 文件编码格式转换

ctrain

编码格式

package com.test;

import java.io.File;

import java.io.FileInputStream;

import java.io.FileOutputStream;

import java.io.IOException;

import java.io.InputStream;

import java.io.OutputStream;

- mysql 在linux客户端插入数据中文乱码

daizj

mysql中文乱码

1、查看系统客户端,数据库,连接层的编码

查看方法: http://daizj.iteye.com/blog/2174993

进入mysql,通过如下命令查看数据库编码方式: mysql> show variables like 'character_set_%'; +--------------------------+------

- 好代码是廉价的代码

dcj3sjt126com

程序员读书

长久以来我一直主张:好代码是廉价的代码。

当我跟做开发的同事说出这话时,他们的第一反应是一种惊愕,然后是将近一个星期的嘲笑,把它当作一个笑话来讲。 当他们走近看我的表情、知道我是认真的时,才收敛一点。

当最初的惊愕消退后,他们会用一些这样的话来反驳: “好代码不廉价,好代码是采用经过数十年计算机科学研究和积累得出的最佳实践设计模式和方法论建立起来的精心制作的程序代码。”

我只

- Android网络请求库——android-async-http

dcj3sjt126com

android

在iOS开发中有大名鼎鼎的ASIHttpRequest库,用来处理网络请求操作,今天要介绍的是一个在Android上同样强大的网络请求库android-async-http,目前非常火的应用Instagram和Pinterest的Android版就是用的这个网络请求库。这个网络请求库是基于Apache HttpClient库之上的一个异步网络请求处理库,网络处理均基于Android的非UI线程,通

- ORACLE 复习笔记之SQL语句的优化

eksliang

SQL优化Oracle sql语句优化SQL语句的优化

转载请出自出处:http://eksliang.iteye.com/blog/2097999

SQL语句的优化总结如下

sql语句的优化可以按照如下六个步骤进行:

合理使用索引

避免或者简化排序

消除对大表的扫描

避免复杂的通配符匹配

调整子查询的性能

EXISTS和IN运算符

下面我就按照上面这六个步骤分别进行总结:

- 浅析:Android 嵌套滑动机制(NestedScrolling)

gg163

android移动开发滑动机制嵌套

谷歌在发布安卓 Lollipop版本之后,为了更好的用户体验,Google为Android的滑动机制提供了NestedScrolling特性

NestedScrolling的特性可以体现在哪里呢?<!--[if !supportLineBreakNewLine]--><!--[endif]-->

比如你使用了Toolbar,下面一个ScrollView,向上滚

- 使用hovertree菜单作为后台导航

hvt

JavaScriptjquery.nethovertreeasp.net

hovertree是一个jquery菜单插件,官方网址:http://keleyi.com/jq/hovertree/ ,可以登录该网址体验效果。

0.1.3版本:http://keleyi.com/jq/hovertree/demo/demo.0.1.3.htm

hovertree插件包含文件:

http://keleyi.com/jq/hovertree/css

- SVG 教程 (二)矩形

天梯梦

svg

SVG <rect> SVG Shapes

SVG有一些预定义的形状元素,可被开发者使用和操作:

矩形 <rect>

圆形 <circle>

椭圆 <ellipse>

线 <line>

折线 <polyline>

多边形 <polygon>

路径 <path>

- 一个简单的队列

luyulong

java数据结构队列

public class MyQueue {

private long[] arr;

private int front;

private int end;

// 有效数据的大小

private int elements;

public MyQueue() {

arr = new long[10];

elements = 0;

front

- 基础数据结构和算法九:Binary Search Tree

sunwinner

Algorithm

A binary search tree (BST) is a binary tree where each node has a Comparable key (and an associated value) and satisfies the restriction that the key in any node is larger than the keys in all

- 项目出现的一些问题和体会

Steven-Walker

DAOWebservlet

第一篇博客不知道要写点什么,就先来点近阶段的感悟吧。

这几天学了servlet和数据库等知识,就参照老方的视频写了一个简单的增删改查的,完成了最简单的一些功能,使用了三层架构。

dao层完成的是对数据库具体的功能实现,service层调用了dao层的实现方法,具体对servlet提供支持。

&

- 高手问答:Java老A带你全面提升Java单兵作战能力!

ITeye管理员

java

本期特邀《Java特种兵》作者:谢宇,CSDN论坛ID: xieyuooo 针对JAVA问题给予大家解答,欢迎网友积极提问,与专家一起讨论!

作者简介:

淘宝网资深Java工程师,CSDN超人气博主,人称“胖哥”。

CSDN博客地址:

http://blog.csdn.net/xieyuooo

作者在进入大学前是一个不折不扣的计算机白痴,曾经被人笑话过不懂鼠标是什么,