计算机组成原理

https://blog.csdn.net/KysonLai/article/details/81625797

【例 6.1】 假设指令字长为 16 位,操作数的地址码为 6 位,指令有零地址和一地址两种格式。

(1)设操作码固定,零地址指令有 512 种,则一地址指令最多有几种?

(2)采用扩展操作码技术,零地址指令有 512 种,则一地址指令最多有几种?

解:

(1)对于一地址指令,操作码长度=16-6=10,这 10 位操作码可有 210=1024 种操作。由于操作码固定,也就是说零地址和一地址的操作码长度均为 10 位,则除去零地址指令 512种,剩下一地址指令最多 1024-512=512 种。

(2)采用扩展操作码技术,操作码位数可变,则一地址和零地址的操作码长度分别为10 和 16 位。可见一地址指令操作码每减少一种,就可多构成 26种零地址指令操作码。

设一地址指令有 X 种,则零地址指令最多有(2^10-X)×2^6种,依题意:

(2^10-X)×2^6=512

所以,X=1016,即此种情况下,一地址指令最多有 1016 种。

以下不属于立即寻址特点的是_。D

A.该类型指令在执行阶段不需要访问内存

B.取回指令既同时取回操作数

C.操作数的范围受指令长度限制

D.指令中的形式地址就是操作数的真实地址

【例】用1K x 4的存储芯片组成4kb存储器,需要几片这样的芯片?

4k=半个字节,所以需要8片

【例】下列说法中正确的是____C__。

A:虚拟存储器技术提高了计算机的速度。

B:若主存由两部分组成,容量分别为2n和2m,则主存地址需要n+m位

C:闪速存储器是一种高密度、非易失性的读/写半导体存储器

D:存取时间是指连续两次读操作所需间隔的最小时间

【例】下列关于闪存的叙述中,错误的是( )

A: 信息可读可写,并且读、写速度一样快

B: 存储元由MOS管组成,是一种半导体存储器

C: 掉电后信息不丢失,是一种非易失性存储器

D:采用随机访问方式,可替代计算机外部存储器

答案:A

【例】主存中的块可以放入Cache中的唯一的位置,这种Cache是 的。

A:全相联

B:组相联

C:块相联

D:直接映象

答案:D

【例】下列说法不正确的是( )

A:硬连线控制器比微程序控制器设计复杂

B:硬连线控制器不便于实现复杂指令的控制

C:微程序控制器比硬连线控制器速度要快

D:微程序控制器将指令执行所需要的控制信号存放在存储器中

答案:C

【例】17、 DMA访问内存时让CPU进入等待状态,等待DMA的批数据访存结束后再恢复工作,这种情况称为() 。

A: 透明的DMA

B:交替访问

C: CPU等待

D:周期挪用

【例】______是构成控制信号序列的最小单位。

A:微程序

B:微命令

C:微指令

D:机器指令

答案:B

【例】以下说法错误的是______ 。

A:硬盘是外围设备

B:软件的功能与硬件的功能在逻辑上是等效的

C:硬件实现的功能一般比软件实现具有更高的执行速度

D:软件的功能不能用硬件取代

答案:D

【例】22、 在CPU中,程序计数器PC用来存放( )

A:现行指令

B:下条指令

C:操作数的地址

D:下条指令的地址

答案:D

【例】下列元件中存取速度最快的是______。

A:Cache

B:寄存器

C:内存

D:外存

答案:B

&随机存取存储器(random access memory,RAM)又称作“随机存储器”,是与CPU直接交换数据的内部存储器,也叫主存(内存)。它可以随时读写,而且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储媒介。

【例】

动态RAM存储信息依靠的是( )

A:磁场

B:双稳态触发器

C:晶体管

D:电容

答案:D

【例】所谓三总线结构的计算机是指______。

A:地址线、数据线和控制线三组传输线

B:I/O总线、主存总统和DMA总线三组传输线

C:I/O总线、主存总线和系统总线三组传输线

D:设备总线、主存总线和控制总线三组传输线

答案:B

【例】

在浮点数编码表示中,______在机器数中不出现,是隐含的。

A:阶码

B:符号

C:尾数

D:基数

答案:D

【例】 Cache是内存的一部分,它可由指令直接访问。

答案:×

【例】

双端口存储器之所以能高速读写,是因为采用了流水技术。

答案:×

是因为:采用了两套相互独立的读写电路

【例】49、 浮点机器数由阶码E和尾数M两部分构成,阶码是(A)数,尾数是(B)数。

答案:A 定点整数 B 定点小数

【例】

什么是RISC?RISC指令系统的特点是什么?

答案:

RISC是精简指令系统计算机,它有以下特点:

(1) 选取使用频率最高的一些简单指令,以及很有用但不复杂的指令。

(2) 指令长度固定,指令格式种类少,寻址方式种类少。

(3) 只有取数/存数指令访问存储器,其余指令的操作都在寄存器之间进行。

(4) 大部分指令在一个机器周期内完成。

(5) CPU中通用寄存器数量相当多。

(6) 以硬布线控制为主,不用或少用微指令码控制。

一般用高级语言编程,特别重视编译优化工作,以减少程序执行时间.

【例】 一台计算机的主存容量为1MB,字长为32位,Cache的容量为512字,确定下列情况下主存和Cache的地址格式:

(1)直接映像的Cache,块长8字

(2)组相联映像的Cache,块长4字,组内4块

解:(1)主存容量为1MB=1M*8=256K*32=256K字 256K字/8字=2^15块

Cache的容量为512字 512字/8字=64块=2^6块

主存地址格式:

| 标记 |

块号 |

块内地址 |

| 9 |

6 |

3 |

Cache地址格式:

| 块号 |

块内地址 |

| 6 |

3 |

- 1.主存块号就是cache的块号,因为是直接映像

- 主存标记就是主存分几块=总的主存位数/一块的位数

- 块内地址的单位是字,块长8字代表有3位

(2))主存容量为1MB=1M*8=256K*32=256K字 256K字/4字=2^16块

Cache的容量为512字 512字/4字=128块=2^7块

1组=4块=2^2块

主存地址格式:

| 标记 |

组号 |

块内地址 |

| 11 |

5 |

2 |

Cache地址格式:

| 组号 |

块内地址 |

| 5 |

2 |

组相联:

1:主存的组号就是cache的组号,cache容量是2^7块,一组要2^2块,那么一共要2^5组,所以组号就是5

2:块内地址就是块长4也就是2^2

3:标记就是主存的位数-组号了

【例】 某8位微型机地址码为20位,若使用8K×4位的RAM芯片组成模块板结构的存储器,试问:

(1)该机所允许的最大主存空间是多少?

(2)若每个模块板为16K×8位,共需几个模块板?

(3)每个模块板内共有几片RAM芯片?

(4)共有多少片RAM?

解:(1)该机所允许的最大主存空间是2^20*8=1MB

(2)若每个模块板为16K×8位,共需2^20*8/16K*8=2^6=64个模块板。

(3)每个模块板内共有16K*8/8K*4=4片RAM芯片。

(4)共有2^20*8/8K*4=256片RAM

【例】

设主存容量为2MB,采用直接映射方式的Cache容量为8KB,块长为4,每字16位。试问主存地址为12345H的存储单元在Cache中的哪一个块的哪一个单元?

解:主存容量为2MB =2M*8/4*16=2^18块

Cache容量为8KB=8K*8/4*16=2^10块

主存地址格式:

| 标记 |

块号 |

块内地址 |

| 8 |

10 |

2 |

12345H=0001 0010 0011 0100 0101=0001 0010 00 1101 0001 01

12345H在cache的0D1H块的01单元

1:0D1H就是获取到对应的块号,然后补齐,这里就是 0000 1101 0001

【例】

5、 某计算机系统的内存系统中,已知cache存取周期为45ns,主存存取周期为200ns。 CPU执行一段程序时,CPU访问内存系统共5000次,其中访问主存的次数为500次,问:

- Cache 命中率H是多少?

- CPU访问内存的平均访问时间Ta是多少?

- Cache/主存系统的访问效率e是多少?

解:(1)Cache 命中率H=(5000-500)/5000=95%

- CPU访问内存的平均访问时间Ta=H*Tc+(1-H)*Tm=0.95*45+0.05*200=52.75ns

(命中率*cache存取周期+不命中率*主存存取周期)

- Cache/主存系统的访问效率e=Tc/Ta=45/52.75=85.3%

(cache存取周期/CPU访问内存的平均访问时间)

【例】

6、 有一个64K×16位的存储器,由16K×4位的DRAM芯片(芯片内是256×256结构)构成,存储器读/写周期为500ns。试问:

(1)需要多少DRAM芯片?

(2)采用异步刷新方式,如果单元刷新间隔不超过8ms,则刷新信号周期是多少?

(3)如果采用集中式刷新,存储器刷新一遍最少要用多少时间?

(4)进行字扩展时需要选用什么样的译码器来实现对地址线的扩展?

(5)请写出该存储器的最大地址,假设最小地址从0000H开始。

解:(1)需要64K*16/16K*4=16片DRAM芯片

- 采用异步刷新方式,单元刷新间隔不超过8ms,8ms/256=31.25us

- 如果采用集中式刷新,存储器刷新一遍最少要用256*500ns=128us

- 进行字扩展时64K/16K=4片芯片进行字扩展,要采用2:4译码器

- 最小地址从0000H开始,64K*16的存储器,该存储器的最大地址是0FFFFH

F代表的是15,从0开始就是有16,所以64K=2^16

【例】

10、设某机主存容量为4MB ,Cache 容量为16KB ,每块包含8 个字,每字32 位,设计一个四路组相联映像(即Cache 每组内共有四个块)的Cache 组织,要求:

(1) 画出主存地址字段中各段的位数。

(2) 设Cache 的初态为空,CPU 依次从主存第0 、1 、2 、⋯ 、99 号单元读出100 个字(主存一次读出一个字) ,并重复按此次序读8 次,问命中率是多少?

(3) 若Cache 的速度是主存的6倍,试问有Cache 和无Cache 相比,速度提高多少倍?

解:(1)主存容量为4MB =4M*8 4M*8/8*32=2^17块

Cache 容量为16KB=16K*8 16K*8/8*32=2^9块

1组=4块

主存地址格式:

| 标记 |

组号 |

块内地址 |

| 10 |

7 |

3() |

(2)主存第0 、1 、2 、⋯ 、99 号单元,共100个单元,100/8=12.25,分布于13个块,因此刚开始每个块的第1个单元都不命中,其它单元都命中,其后7次所有块都命中,因此

命中率=(800-13)/800=98.375%

(3)假设Cache的访问时间为 Tc=t,主存的访问时间为Tm=6t,

Ta=HTc+(1-H)Tm=0.98375*t+0.01625*6t=1.08125t(CPU访问内存的平均访问时间)

6t/1.08125t-1=4.45

速度大约提高4.45倍。

【例】

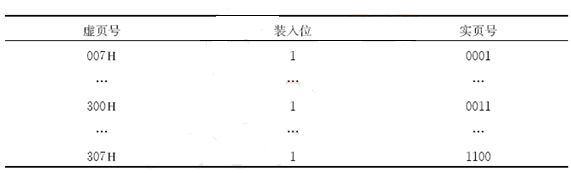

11、已知采用页式虚拟存储器, 某程序中一条指令的虚地址是:000001111111100000 。该程序的页表起始地址是0011 ,页面大小1K ,页表中有关单元最末四位(实页号)见下表:

请指出指令地址(虚地址)变换后的主存实地址。

解:虚拟地址格式

| 虚业号 |

页内地址 |

|

|

10位 |

00000111 11 1110 0000

虚页号为0000 0111(根据页内地址有10位可以得出)

页面起始地址为0011

两个组合后虚页号为 0011 0000 0111=307H

307H对应的实页号为1100,所以实地址为1100 11 1110 0000

实地址=实页号+页内地址

【例】

- 指令字长16位,每个操作数的地址码长6位,指令分为无操作数、单操作数和双操作数三类。若双操作数指令有K条,无操作数指令有L条,问单操作数最多可能有多少条?

解:

| op |

A1 |

A2 |

| 4 |

6 |

6 |

假设双操作数指令有K条,则4位二进制位最多可以扩展16条,还剩下16-K的空间可以扩展,每一次扩展一个地址码6位,假设单操作数指令为X条,则[(16-K)*2^6-X]*2^6为余下的零地址码可扩展的指令。

[(16-K)*2^6-X]*2^6>=L

X<=(16-K)*26-L*2-6

双操作数就是占了两个操作数的地址位,一共12位

【例】

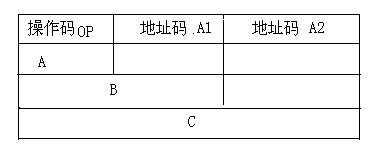

- 某机器字长16位,采用单字长指令,每个地址码6位。试采用操作码扩展技术,设计14条二地址指令,80条单地址指令,60条零地址指令。下图为指令的编码示意图。

(1)请分别计算出OP、A1、A2的各占多少位二进制位。

(2)假设A作为二地址指令的操作码编码,请计算出A的范围,假设A从0开始,请用二进制数进行表示A的起止范围。

(3)假设B作为一地址指令的操作码编码,请计算出B的范围,假设B承接A的编码,请用二进制数进行表示B的起止范围。

(4)假设C作为零地址指令的操作码编码,请计算出C的范围,假设C承接B的编码,请用二进制数进行表示C的起止范围。

(5)如果地址码A2用来表示内存地址,请问它的地址范围是多少,假设地址从0开始,请用十六进制表示。

解:

- OP=16-2*6=4 A1=6 A2=6

- 二地址有14条,操作码占了4位,所以 0000—1101

- 一共80条,操作吗占了10位,所以1110 0000000—1111001111

- 一共60位,1111010000000000--1111010000111011

【例】

假设相对寻址的转移指令占两个字节,第一个字节是操作码和寻址方式,第二个字节是相对偏移量,用补码表示。若当前转移指令的第一个字节所在地址为0019H,且CPU每取出一个字节指令便会自动执行(PC)+1->PC操作。试问:(1)若转移的目标地址分别为0006H时,转移指令第二个字节的内容是什么?(2)若转移的目标地址分别为00025H时,转移指令第二个字节的内容是什么?

解:

| 内存地址 |

内存内容 |

| 0019H |

OP |

| 001AH |

A |

1:Ea=(PC)+A=0019+2+A=0006(因为移动了两个字节,所以要加2)

A=0006-001B=FFEBH

2: EA=(PC)+A=0019+2+A=0025H

A=0025-001B=000AH

【例】

6、 已知某机器字长16位,主存按字编址,其双操作数指令格式为:

| OP |

R |

D |

| 6位 |

2位 |

8位 |

其中OP为操作码,R为通用寄存器地址,试问下列寻址方式能访问的最大主存区为多少机器字?

- D为立即数

- D为主存直接地址

- D为主存间接地址

- D为变址形式地址,变址寄存器为R1(字长16位)

- D为基址形式地址,基址寄存器的Rb(字长16位)

- D为相对寻址的偏移量

解:

- D为立即数 2^0

- D为主存直接地址 2^8

- D为主存间接地址 2^16

- D为变址形式地址,变址寄存器为R1(字长16位) 2^16

- D为基址形式地址,基址寄存器的Rb(字长16位)2^16

- D为相对寻址的偏移量 2^16

【例】

设主存容量为512K字,Cache容量为32K字,块长为8,假设相联存储器由主存标记和4个控制位构成。

(1)Cache中可装入多少块数据,主存有多少块数据?

(2)在直接映射方式下,请分别计算各部分的二进制位,并计算出相联存储器的容量。

(3)在四路组相联映射方式下,请分别计算各部分的二进制位数,并计算出相联存储器的容量。

(4)在全相联映射方式下,请分别计算各部分的二进制位数,并计算出相联存储器的容量。

答案:

(1)212块数据

(2)直接映射的情况下,主存地址格式如下,主存标记4位,块地址12位,块内地址3位

| T=4 |

C=12 |

B=3 |

(3)四路组相联的情况下,主存地址格式如下,主存标记6位,组地址10位,块内地址3位

| T+r=6 |

C-r=10 |

B=3 |

(4)全相联的地址格式如下,主存标记16位,块内地址3位

| T=16 |

B=3 |

就是块地址为0

【例】

77、

参见图1,这是一个二维中断系统,请问:

① 在中断情况下,CPU和设备的优先级如何考虑?请按降序排列各设备的中断优先级。

② 若CPU现执行设备C的中断服务程序,IM2,IM1,IM0的状态是什么?如果CPU执行设备H的中断服务程序,IM2,IM1,IM0的状态又是什么?

③ 每一级的IM能否对某个优先级的个别设备单独进行屏蔽?如果不能,采取什么方法可达到目的?

④ 若设备C一提出中断请求,CPU立即进行响应,如何调整才能满足此要求?

答案:

① ABCDEFGHI

② 111 001

③ 不可,将EI清零。

④ 将C单独取出来放在第3级上,使第3级最高,让IM3=0.

【例】

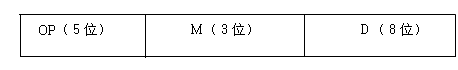

某机型16位字长指令格式如下:

其中,D是形式地址,采用补码表示(包括一位符号位),M是寻址方式:

M=0 立即寻址;

M=1 直接寻址(这是D为地址,无符号数);

M=2 间接寻址;

M=3 变址寻址(变址寄存器Ri,16位);

M=4 基址寻址(基址寄存器Rb,16位);

M=5 相对寻址。

(1)该指令格式最多可以定义多少种不同的操作?

(2)立即数寻址操作数的范围是什么?

(3)写出各种寻址方式的操作数的计算表达式。

(4)各种寻址方式能访问的最大主存范围是多少?

答案:

解:由于操作码占5位,因此可以进行32种不同的操作,由于形式地址占8位,采用补码表示,因此立即数的操作数范围从-128到127

寻址方式的有效地址的计算;

M=0 立即寻址;无EA data=D

M=1 直接寻址(这是D为地址,无符号数);EA=D data=(D)

M=2 间接寻址;EA=(D) data=((D))

M=3 变址寻址(变址寄存器Ri,16位);EA=(Ri)+D data=((Ri)+D)

M=4 基址寻址(基址寄存器Rb,16位);EA=(Rb)+D data=((Rb)+D)

M=5 相对寻址。EA=(PC)+D data=((PC)+D)

寻址方式能访问的最大主存范围

M=0 立即寻址;无有效地址,不用计算

M=1 直接寻址(这是D为地址,无符号数);0-255

M=2 间接寻址;0-216-1

M=3 变址寻址(变址寄存器Ri,16位);0-216-1

M=4 基址寻址(基址寄存器Rb,16位);0-216-1

M=5 相对寻址。0-216-1

【例】

4.某机字长16位,问在下列几种情况下所能表示数值的范围:

- 无符号整数;

- 用原码表示定点小数;

- 用补码表示定点小数;

- 用原码表示定点整数;

- 用补码表示定点整数。

解:

(1) 无符号整数;

0~2^16-1

(2) 用原码表示定点小数;

-1+2^(-15)~1-2^(-15)

(3) 用补码表示定点小数;

-1~1-2^(-15)

(4) 用原码表示定点整数;

-2^15+1~ 2^15-1

(5) 用补码表示定点整数。

-2^15~2^15-1

【例】

10.设浮点数的阶码和尾数部分均用补码表示,按照浮点数的运算规则,计算下列各题:

(1)X=2101×(-0.100010),Y=2100×(-0.111110)

(2)X=2-101×0.101100,Y=2-100×(-0.101000)

注:此题中阶码用二进制表示。

求:X+Y,X-Y

解:(1)X=0101 1.011110

Y=0100 1.000010

阶差=1

Y=0101 1.100001(向右移动一位,开头补1)

Mx+My= 11.011110 +11.100001=10.111111

规格化

Mx+My=1.011111 阶码+1=0110

X+Y= 0110 1.011111