嵌入式相关知识点

嵌入式中小端模式为 低字节存储在低地址,高字节存储在高地址。大端模式为低字节存储在高地址,高字节存储在低地址。

如何判断一个系统为大端模式还是小端模式? 小端模式的数据如何转换为大端模式的数据?

#include

#include

using namespace std;

bool IsLittleEndian()//判断是否是小端模式。是小端则返回true

{

typedef union

{

int a;

char b;

}Type;

Type test;

test.a=1;

return test.b==1;

}

bool IsLittleEndian2()

{

int a=1;

return *((char*)(&a))==1;

}

int LittleEndianToBigEndian(int number)//小端转大端

{

int temp=0;

char *p=(char*)&number;

temp=((*p)<<24)+(*(p+1)<<16)+(*(p+2)<<8)+*(p+3);

return temp;

}

int LittleEndianToBigEndian2(int number)

{

return (number&0x000000ff)<<24|(number&0x0000ff00)<<16|(number&0x00ff0000)<<8|(number&0xff000000);

}

int main()

{

if(IsLittleEndian()&&IsLittleEndian2())

{

cout<<"系统是小端模式"< 哈弗结构和冯诺依曼结构

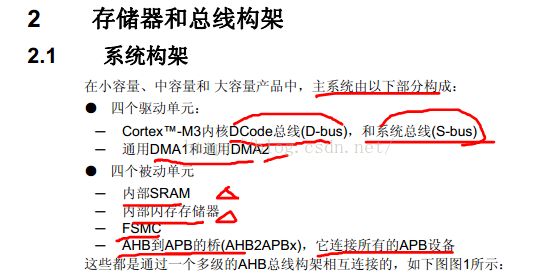

哈佛结构是一种存储器结构。使用哈弗结构的处理器有AVR ARM9 ARM10 ARM cortex m3 等

哈佛结构是一种将程序指令存储和数据存储分开的存储器结构,数据总线和地址总线分开 数据和指令的储存可以同时进行,可以使指令和数据有不同的数据宽度

哈佛结构的微处理器通常具有较高的执行效率。其程序指令和数据指令分开组织和储存的,执行时可以预先读取下一条指令

以下转自:http://blog.sina.com.cn/s/blog_a44094ea01016s09.html

哈佛结构

![]()

(英语:Harvard architecture)是一种将程序指令储存和数据储存分开的存储器结构。中央处理器首先到程序指令储存器中读取程序指令内容,解码后得到数据地址,再到相应的数据储存器中读取数据,并进行下一步的操作(通常是执行)。程序指令储存和数据储存分开,数据和指令的储存可以同时进行,可以使指令和数据有不同的数据宽度,如Microchip公司的PIC16芯片的程序指令是14位宽度,而数据是8位宽度。

与冯.诺曼结构处理器比较,哈佛结构处理器有两个明显的特点:

1、使用两个独立的存储器模块,分别存储指令和数据,每个存储模块都不允许指令和数据并存;

2、使用独立的两条总线,分别作为CPU与每个存储器之间的专用通信路径,而这两条总线之间毫无关联。

改进的哈佛结构,其结构特点为:

1、使用两个独立的存储器模块,分别存储指令和数据,每个存储模块都不允许指令和数据并存,以便实现并行处理;

2、具有一条独立的地址总线和一条独立的数据总线,利用公用地址总线访问两个存储模块(程序存储模块和数据存储模块),公用数据总线则被用来完成程序存储模块或数据存储模块与CPU之间的数据传输;

哈佛结构的微处理器通常具有较高的执行效率。其程序指令和数据指令分开组织和储存的,执行时可以预先读取下一条指令。目前使用哈佛结构的中央处理器和微控制器有很多,除了上面提到的Microchip公司的PIC系列芯片,还有摩托罗拉公司的MC68系列、Zilog公司的Z8系列、ATMEL公司的AVR系列和安谋公司的ARM9、ARM10和ARM11。

冯·诺伊曼结构

![]()

(von Neumann architecture),也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一起的电脑设计概念结构。本词描述的是一种实作通用图灵机的计算装置,以及一种相对于平行计算的序列式结构参考模型(referential model)。

本结构隐约指导了将储存装置与中央处理器分开的概念,因此依本结构设计出的计算机又称储存程式型电脑。

冯.诺曼结构处理器具有以下几个特点:

必须有一个存储器;

必须有一个控制器;

必须有一个运算器,用于完成算术运算和逻辑运算;

必须有输入和输出设备,用于进行人机通信。

ARM有7个基本工作模式:

用户模式(user)、系统模式(system) 特权模式(SVC) 快速中断模式(FIQ)、 中断模式(IRQ)、、数据访问中止模式(abort)、未定义指令中止模式(undef)、

1)ARM有哪几个异常类型?

7种异常类型。

复位异常 数据访问中止异常 未定义指令异常 指令预取中止

软件中断 FIQ(快速中断请求) IRQ(中断请求)

2)ARM核有多少个寄存器?

3) ARM处理器共有37个寄存器,被分为若干个组(BANK),这些寄存器包括:

4) 31个通用寄存器,包括程序计数器(PC指针),均为32位的寄存器。

5) 6个状态寄存器,用以标识CPU的工作状态及程序的运行状态,均为32位,只使用了其中的一部分。

6)什么寄存器用于存储PC和LR寄存器?

R15(PC)、R14(LR)

R14 LR 为链接寄存器当调用一个函数时,返回地址被自动保存到链接寄存器,在函数返回时有效 如果函数是分支的一部分(即函数中又调用另一个函数),则链接寄存器必须入栈(R13)

7)R13通常用来存储什么?

ARM处理器中通常将寄存器R13作为堆栈指针(SP)。ARM处理器针对不同的模式,共有6 个堆栈指针(SP),其中用户模式和系统模式共用一个SP,每种异常模式都有各自专用的R13寄存器(SP)。它们通常指向各模式所对应的专用堆栈,也就是ARM处理器允许用户程序有六个不同的堆栈空间哪种模式使用的寄存器最少?

用户模式/系统模式(不用SPSR)

8)在Thumb指令集中,哪些寄存器处于lowgroup?

R0-R7属于低位寄存器。

9)CPSR的哪一个位反映了处理器的状态?

第5位(从0开始),T状态位。

1表示运行在Thumb状态,0表示运行在ARM状态。

10) 所有的Thumb指令采取什么对齐方式?

半字对齐(2个字节)

为什么FIQ的服务程序地址要位于0X1C?

尽可能快,省去跳转指令(FIQ的向量地址是异常中断向量表的最高地址,而异常中断向量表后跟的是程序代码,FIQ的中断服务程序紧接中断向量表存放,中断过程可以节省一条跳转指令)

11)在复位后,ARM处理器处于何种模式、何种状态?

特权模式(SVC)、ARM状态

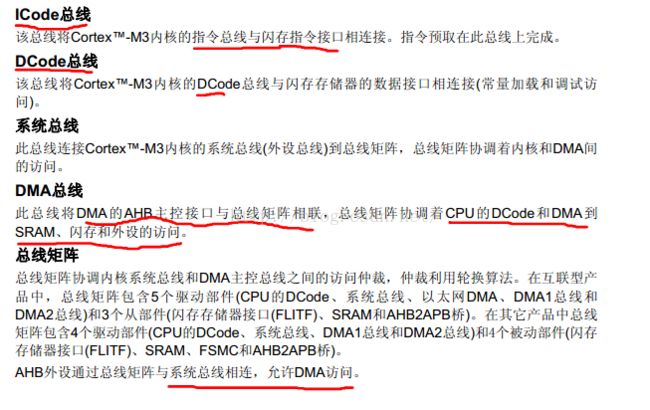

AMBA 由ARM公司研发推出的AMBA(Advanced Microcontroller Bus Architecture)片上总线

AHB( Advanced High-performance Bus)高性能总线 APB(Advanced Peripheral Bus)外设总线

AMBA标准定义了三组总线:AHB(AMBA高性能总线)、ASB(AMBA系统总线)、和APB(AMBA外设总线)。

以下转自:http://blog.sina.com.cn/s/blog_a5b8978f0101f39i.html

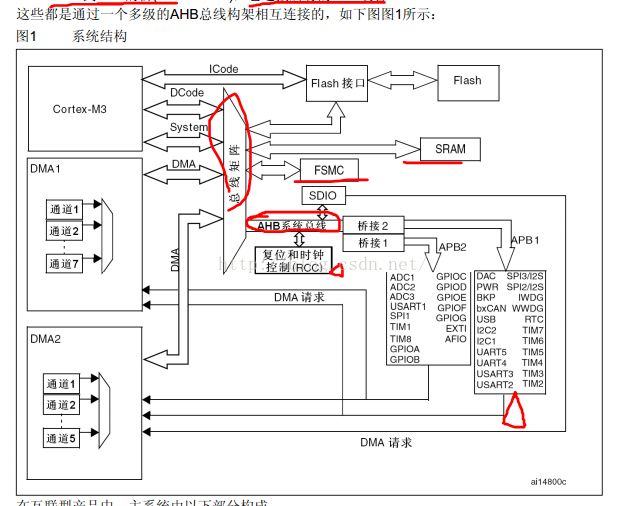

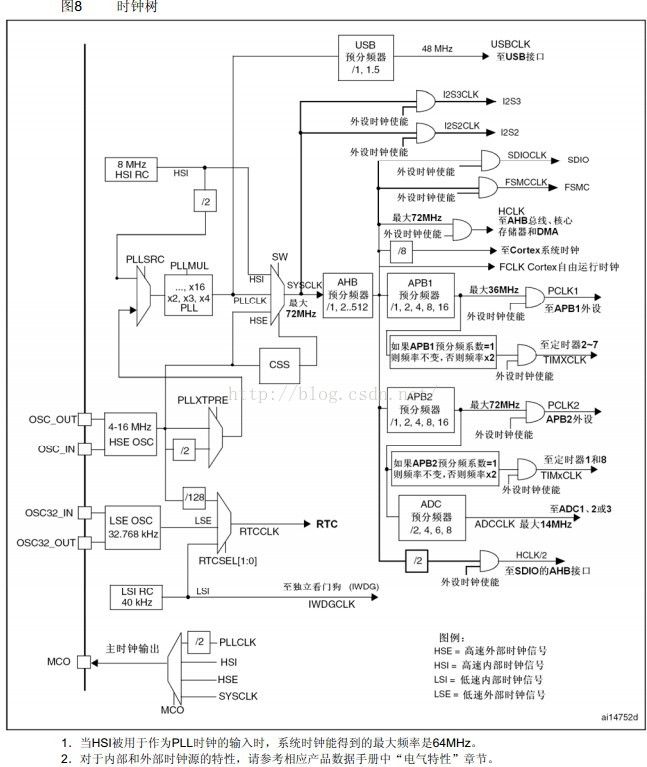

STM32时钟系统

在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。

①HSI是高速内部时钟,RC振荡器,频率为8MHz。

②HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

③LSI是低速内部时钟,RC振荡器,频率为40kHz。

④LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

⑤PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

用户可通过多个预分频器配置AHB总线、高速APB2总线和低速APB1总线的频率。AHB和APB2域的最大频率是72MHZ。APB1域的最大允许频率是36MHZ。SDIO接口的时钟频率固定为HCLK/2。

40kHz的LSI供独立看门狗IWDG使用,另外它还可以被选择为实时时钟RTC的时钟源。另外,实时时钟RTC的时钟源还可以选择LSE,或者是HSE的128分频。RTC的时钟源通过RTCSEL[1:0]来选择。

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,PLL必须使能,并且时钟频率配置为48MHz或72MHz。

另外,STM32还可以选择一个PLL输出的2分频、HSI、HSE、或者系统时钟SYSCLK输出到MCO脚(PA8)上。系统时钟SYSCLK,是供STM32中绝大部分部件工作的时钟源,它可选择为PLL输出、HSI或者HSE,(一般程序中采用PLL倍频到72Mhz)在选择时钟源前注意要判断目标时钟源是否已经稳定振荡。Max=72MHz,它分为2路,1路送给I2S2、I2S3使用的I2S2CLK,I2S3CLK;另外1路通过AHB分频器分频(1/2/4/8/16/64/128/256/512)分频后送给以下8大模块使用:

① 送给SDIO使用的SDIOCLK时钟。

② 送给FSMC使用的FSMCCLK时钟。

③ 送给AHB总线、内核、内存和DMA使用的HCLK时钟。

④ 通过8分频后送给Cortex的系统定时器时钟(SysTick)。

⑤ 直接送给Cortex的空闲运行时钟FCLK。

⑥ 送给APB1分频器。APB1分频器可选择1、2、4、8、16分频,其输出一路供APB1外设使用(PCLK1,最大频率36MHz),另一路送给定时器(Timer2-7)2、3、4倍频器使用。该倍频器可选择1或者2倍频,时钟输出供定时器2、3、4、5、6、7使用。

⑦ 送给APB2分频器。APB2分频器可选择1、2、4、8、16分频,其输出一路供APB2外设使用(PCLK2,最大频率72MHz),另一路送给定时器(Timer1、Timer8)1、2倍频器使用。该倍频器可选择1或者2倍频,时钟输出供定时器1和定时器8使用。另外,APB2分频器还有一路输出供ADC分频器使用,分频后得到ADCCLK时钟送给ADC模块使用。ADC分频器可选择为2、4、6、8分频。

⑧ 2分频后送给SDIO AHB接口使用(HCLK/2)。

时钟输出的使能控制

在以上的时钟输出中有很多是带使能控制的,如AHB总线时钟、内核时钟、各种APB1外设、APB2外设等。

当需要使用某模块时,必需先使能对应的时钟。需要注意的是定时器的倍频器,当APB的分频为1时,它的倍频值为1,否则它的倍频值就为2。

连接在APB1(低速外设)上的设备有:电源接口、备份接口、CAN、USB、I2C1、I2C2、UART2、UART3、SPI2、窗口看门狗、 Timer2、Timer3、Timer4。注意USB模块虽然需要一个单独的48MHz时钟信号,但它应该不是供USB模块工作的时钟,而只是提供给串行接口引擎(SIE)使用的时钟。USB模块工作的时钟应该是由APB1提供的。

连接在APB2(高速外设)上的设备有:GPIO_A-E、USART1、ADC1、ADC2、ADC3、TIM1、TIM8、SPI1、AFIO