intel manual: EPT Translatin Mechanism

继续接着理解并且翻译,这部分算是EPT翻译机制最核心部分了,的确有一些难理解,我看了好几遍也不敢说完全掌握所以翻译留着继续看,每次体会都不同,索性这次直接翻译过来放这了,方便自己后面再来看。如果下面哪儿有错误欢迎留言区指出,谢谢。

EPT转换机制仅使用每个客户物理地址的Bit 47:0. 它使用4的页表遍历长度,也就是说访问最多4个EPT分页结构项去翻译一个客户机物理地址(GPA)。这48位由逻辑处理器划分以遍历EPT分页结构。

- 一个4 KB自然对齐的EPT PML4表位于扩展页表指针(EPTP)的Bit 51:12中指定的物理地址,该指针是VM执行控制字段(see Table 24-8 in Section 24.6.11)。一个EPT PML4表包括512个64位条目(EPT PML4Es),使用如下定义的物理地址选择EPT PML4E:

——Bits 63:52 are all 0.

——Bits 51:12 are from the EPTP.

——Bits 11:3 are bits 47:39 of the GPA(guest-physical address).

——Bits 2:0 are all 0.

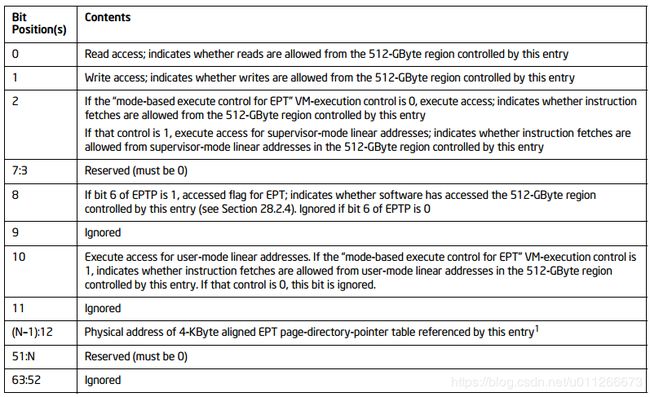

因为一个EPT PML4E使用客户机物理地址的Bit 47:39来标识,所以它控制对客户机物理地址空间的512 GB的访问区域。一个EPT PML4E格式如下表1所示:

表1 一个引用EPT页目录指针表的EPT PML4条目(EPT PML4E)的格式

- 一个4KB自然对齐的EPT分页目录指针表(PDPT)位于EPT PML4E的Bits 51:12中指定的物理地址。一个EPT 分页目录指针表包含512个64 bit的条目(EPT PDPTE)。使用如下定义的物理地址选择EPT PDPTE:

——Bits 63:52 are all 0.

——Bits 51:12 are from the EPT PML4E

——Bits 11:3 are bits 38:30 of the GPA.

——Bits 2:0 are all 0.

接着,因为一个EPT PDPTE使用客户机物理地址的Bit 47:39来标识,所以它控制着对客户机物理地址空间的1 GB的访问区域。使用EPT PDPTE取决于EPT PDPT entry中Bti 7的值:

- IF EPT PDPTE中Bit 7是1,则EPT PDPTE映射1GB的页。最终的物理地址计算如下:

——Bits 63:52 are all 0

——Bits 51:30 are from the EPT EPTPE

——Bits 29:0 are from the original GPA

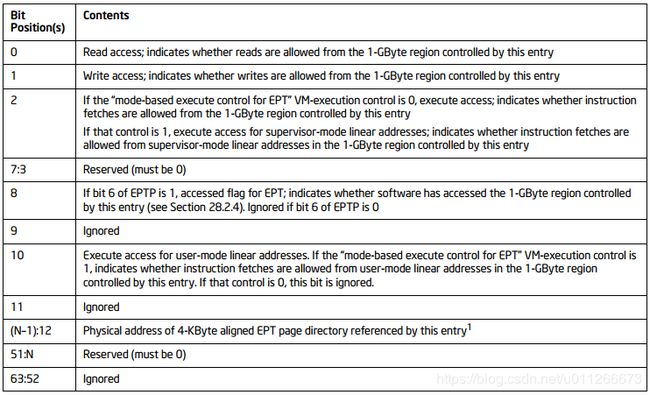

表2给出了映射1 GB页的EPT PDPTE的格式。

表2 一个映射1GB分页的EPT分页目录指针表条目(EPT PDPTE)的格式

- IF EPT PDPTE中Bit 7是0,一个4KB自然对齐的EPT分页目录(PDE)位于EPT PDPTE的Bits 51:12中指定的物理地址。一个EPT 分页目录包含了512个64位条目(PDEs)。使用如下定义的物理地址选择EPT PDPTE:

——Bits 63:52 are all 0.

——Bits 51:12 are from the EPT PDPTE

——Bits 11:3 are bits 29:21 of the GPA.

——Bits 2:0 are all 0.

表3给出了引用EPT页面目录的EPT PDPTE的格式。

表3 一个引用EPT分页目录的EPT分页目录指针表项(EPT PDPTE)的格式

接着,因为一个EPT PDE使用客户机物理地址的Bit 47:21来标识,所以它控制着对客户机物理地址空间的2MB的访问区域。使用EPT PDE取决于EPT PD entry中Bit 7的值:

- IF EPT PDE中Bit 7是1,则EPT PDE映射2MB的页。最终的物理地址计算如下:

——Bits 63:52 are all 0

——Bits 51:21 are from the EPT EPE

——Bits 20:0 are from the original GPA

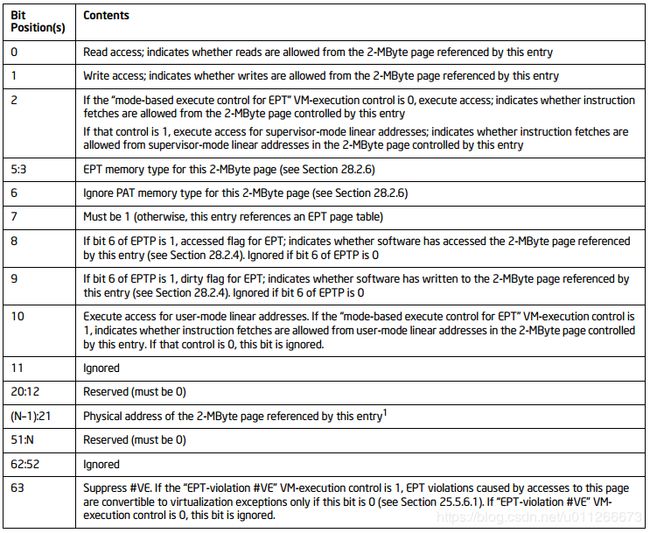

表4给出了一个映射2MB页的EPT PDE的格式。

表4 一个映射2MB分页的EPT分页目录条目(EPT PDE)的格式

- IF EPT PDE中Bit 7是0,一个4KB自然对齐的EPT页表位于EPT PDE的Bits 51:12中指定的物理地址。一个EPT页表包含了512个64位条目(PTEs)。使用如下定义的物理地址选择EPT PTE:

——Bits 63:52 are all 0.

——Bits 51:12 are from the EPT PDE

——Bits 11:3 are bits 20:12 of the GPA.

——Bits 2:0 are all 0.

表5给出了引用EPT页面目录的EPT PDE的格式。

表5 一个引用EPT页表的EPT分页目录项(EPT PDE)的格式

- 最后,因为一个EPT PTE使用客户机物理地址的Bit 47:21来标识,所以它每一个EPT PTE映射一个4KB页。最终计算的物理地址如下:

— Bits 63:52 are all 0.

— Bits 51:12 are from the EPT PTE.

— Bits 11:0 are from the original guest-physical address.

表6给出了一个EPT PTE的格式

表6 一个映射4KB页的EPT页表条目的格式

如果Bit 2:0中任何一个为1则存在EPT分页结构条目,否则该条目不存在。处理器忽略Bits 62:3并且既不使用该条目去链接另一个EPT分页结构条目,也不使用该条目来产生物理地址。使用GPA的引用,其翻译遇到不存在的EPT分页结构会导致EPT violation(Section 28.2.3.2).(If the ”EPT-violation #VE” VM-excution control is 1, 则只有当Bit 63是0时EPT violation才可转换为虚拟化异常(Section 25.6.1);IF the ”EPT-violation #VE” VM-excution control is 0,则忽略该位)。

注意:IF the “mode-based execute control for EPT” VM-execution control is 1, 如果bits 2:0或bit 10中任何一个为1,则存在一个EPT分页结构条目。如果bit2:0是0但bit 10是1,则该条目通常用于链接另一个EPT分页结构条目或产生物理地址。

总结,上面的讨论描述了EPT分页结构如何互相链接以及逻辑处理器在翻译一个gpa时是如何便利这些结构的。此处没有涵盖所有翻译过程的细节。其他更详细的内容如下:

- 翻译过程可能导致VM exit的情况(又是在过程完成之前)在section 28.2.3中描述

- EPT翻译机制和内存类型之间的互相作用在section 28.2.6中描述

图1给出了EPTP(extended-page-table pointer)格式和EPT分页结构条目的简介。对对EPT分页结构条目,它分别标识映射页面条目的格式,引用其他EPT分页结构条目的格式,以及不存在的分页结构条目。Bit2:0和Bit7被突出显示因为它们确定如何使用分页结构(图28-1不包含if the “mode-based execute control for EPT” VM-execution control is 1, if any of bits 2:0或bit 10中任何一个为1则存在分页结构条目的情况)。

图1 EPTP和EPT分页结构条目的格式

参考:

《Intel® 64 and IA-32 Architectures Software Developer’s Manual Volume 3 (3A, 3B & 3C): System Programming Guide》