FPGA_Quartus 18.1环境搭建

文章目录

- 前言

- Quartus下载与安装

- 硬件连接

- 新建工程

- Verilog代码

- 引脚分配

- 编译

- 下载

- 下载程序到Flash

- 微信公众号

前言

前几周总结了下MCU, Xavier的GPIO, UART, CAN, 以太网等的使用, 本周开一下FPGA, 水平有限, 只当一个划水的总结, 如有错误, 欢迎指正.

Quartus下载与安装

Quartus Prime 精简版下载

官网里可以看到最新的不收费的Lite版本已经更新到19.1了, 但是还没有Windows版本:

那就切换回18.1, 选择Windows:

下面下载Quartus Prime, Modelsim以及要用到的Cyclone IV的器件支持, 用Eagleget之类的下载软件下载还是挺快的, 注意下载到同一个文件夹, 需要注册一个Intel的帐号:

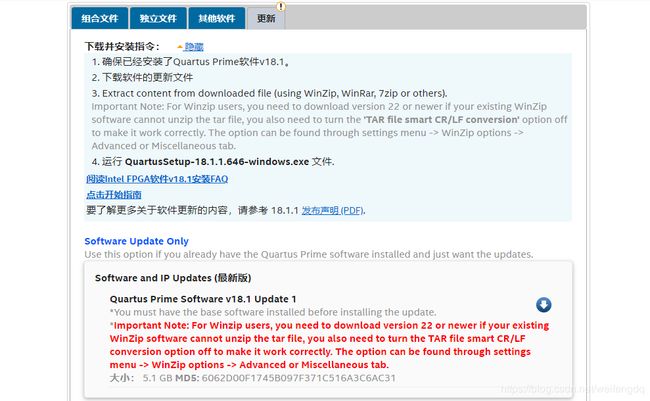

可以看到更新处有感叹号, 点击更新, 把这个更新也下载下来:

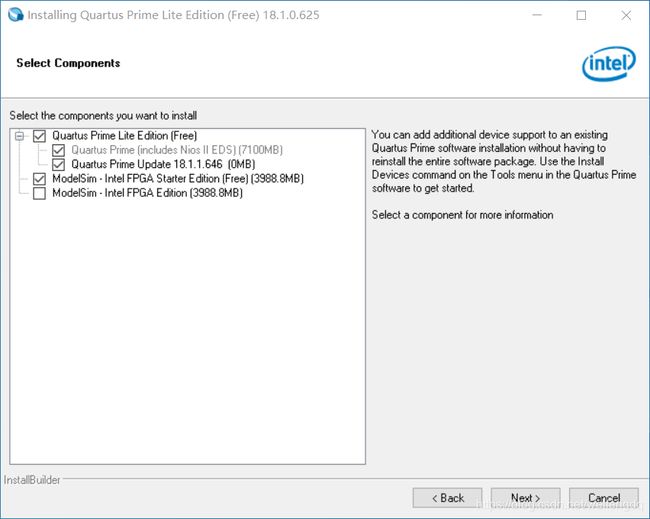

下载完后, 就双击QuartusLiteSetup-18.1.0.625-windows.exe进行安装, 中间可以换安装位置:

默认(这里当时的器件支持还没下下来, 后面单独装):

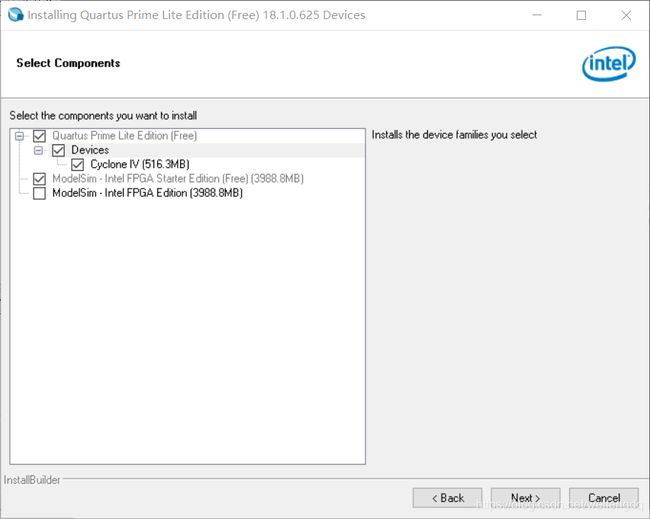

之后就可以一路到底了, 接下来安装器件支持, 找到Windows开始菜单中的Device Installer(Quartus Prime 18.1), 找到下载的Cyclone IV:

一路装下去就可以了.

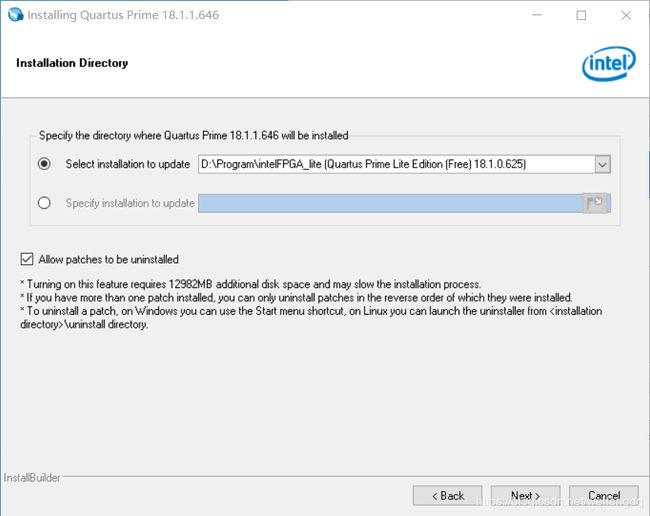

接着安装更新QuartusSetup-18.1.1.646-windows.exe(tar包解压):

也是一路到底就好.

硬件连接

这里用Verilog写一段EP4CE6F17C8点灯的代码, 引脚分布如下图:

| 名称 | 引脚 | 说明 |

|---|---|---|

| sys_clk | E1 | 50M有源晶振 |

| sys_rst_n | M1 | 复位, 低有效 |

| led | E10 | 高电平点亮 |

新建工程

步骤如下:

- File -> New Project Wizard…

- Next

- 选择工程目录, 填入工程名.

- Empty Project

- Add Files不设置, 直接点Next.

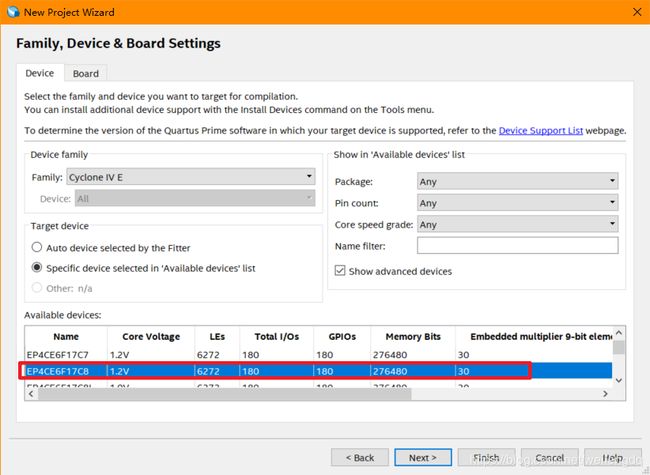

- 器件选择

EP4CE6F17C8:

- EDA Tool Setting暂不动, 点击Next.

- Summary中点Finish.

Verilog代码

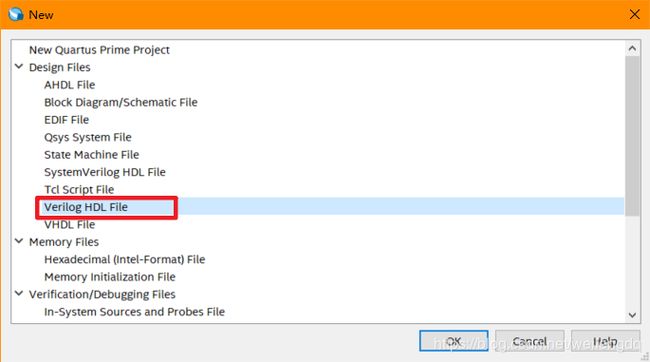

File -> New -> 选择Verilog HDL File:

填入以下代码:

module led_test(

input sys_clk,

input sys_rst_n,

output reg led

);

parameter count_1ms = 50000;

parameter on_time_ms = 1000; //led on 1s

parameter off_time_ms = 500; //led off 0.5s

reg [31:0] counter;

always @(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

counter <= 32'd0;

else if(counter < (on_time_ms+off_time_ms)*count_1ms)

counter <= counter + 1'b1;

else

counter <= 32'd0;

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

led <= 1'b0;

else if(counter > off_time_ms*count_1ms)

led <= 1'b1; //led on

else

led <= 1'b0; //led off

end

endmodule

编辑完后保存, 双击左侧Analysis & Elaboration或上面快捷按钮, 检查是否有代码错误.

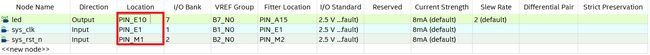

引脚分配

分配引脚, Assignments -> Pin Planner:

编译

Processing -> Start Compilation.

或者点击相应快捷按钮.

下载

USB Blaster连接FPGA板子与电脑, Tools -> Programmer或者点击上方快捷按钮, 可以看到默认已经选中sof文件, 没有的自己点Add File...按钮添加:

点击Start按钮, 等待Processing进度显示100%(Successful), 可以看到板子上LED, 亮1s灭0.5s, 符合预期. 需要注意的是, 这个断电后就没了.

下载程序到Flash

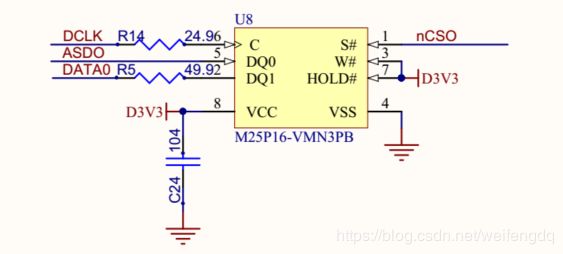

程序断电保存, 可以通过JTAG下载程序到板载Flash中, 使用的M25P16和官方的EPCS16用起来是一样的:

引脚对应为:

| 名称 | 引脚 |

|---|---|

| EPCS_ASDO | C1 |

| EPCS_CS | D2 |

| EPCS_DATA0 | H2 |

| EPCS_CLK | H1 |

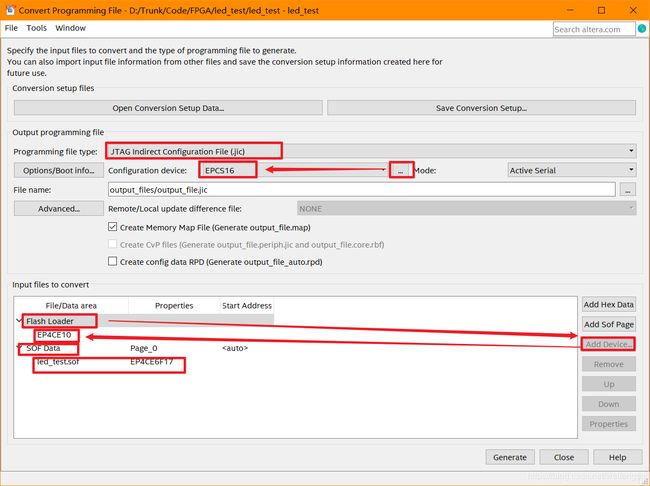

需要将上面的sof文件转换成jic文件: File -> Convert Programming Files...:

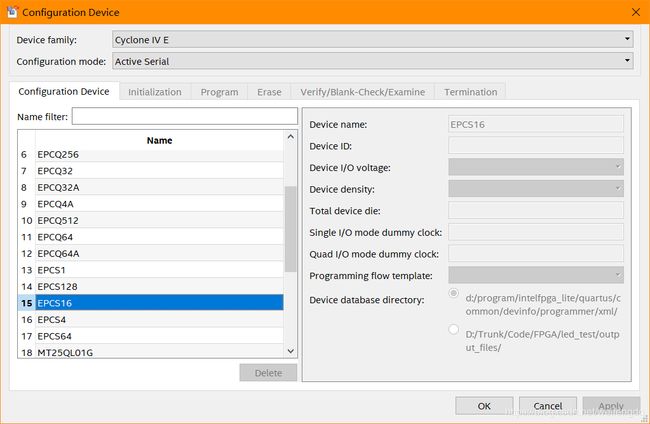

其中, EPCS16是点击右边的...按钮, 选择:

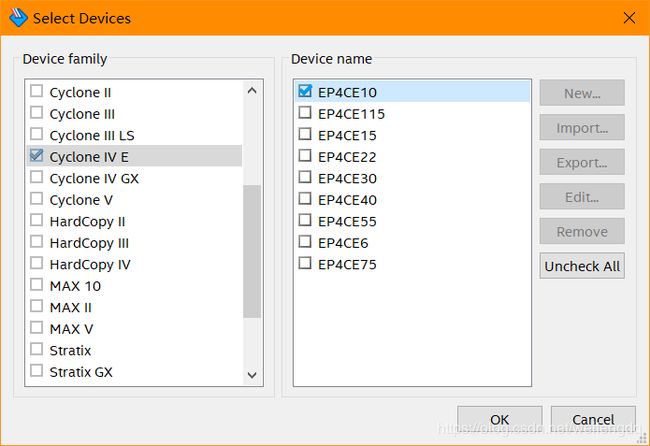

选中Flash Loader, 点击右边Add Device...:

选中SOF Data, 点击右边Add File, 添加sof文件.

最后点击下方的Generate按钮生成jic文件.

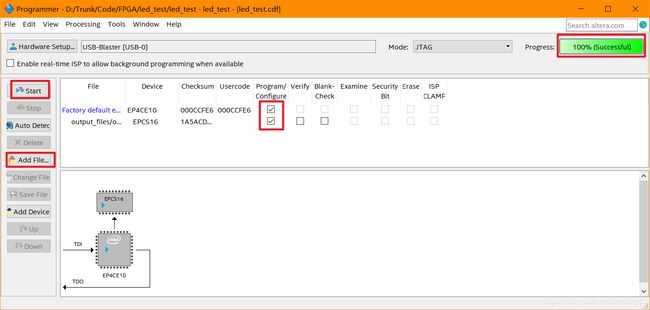

Tools -> Programmer或者点击上方Programmer快捷按钮, 删掉原来的sof文件, 添加jic文件, 注意图中的勾, 点击Start按钮, 下载比较慢, 等Progress显示100%, 可以看到开发板没有反应, 断电再重新上电可以看到程序运行.

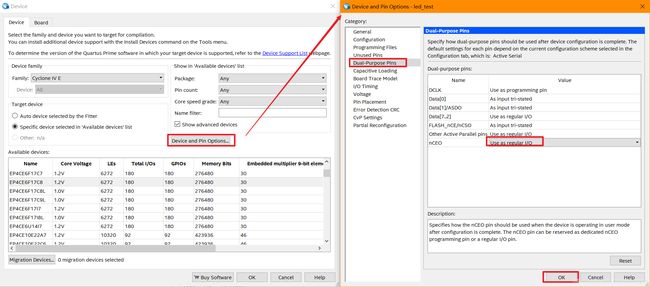

一说用到Flash时, 需要进行引脚配置: Assignments -> Device -> Device and Pin Options... -> Dual-Purpose Pins -> nCEO或者全部设置为Use as regular I/O:

微信公众号

欢迎扫描二维码关注本人微信公众号, 及时获取或者发送给我最新消息:

![]()