ARM架构——面试了菊厂,中兴,MTK,鼎桥,总结了ARM Cortex-M3中断

一、中断和异常概述

中断和异常的作用是指示系统中的某个地方发生一些事件,需要引起处理器(包括正在执行中的程序和任务)的注意.。当中断和异常发生时,典型的结果是迫使处理器将控制从当前正在执行的程序或任务转移到另一个历程或任务中去。该例程叫做中断处理程序,或者异常处理程序。如果是一个任务,则发生任务切换。

ARM架构的中断就是异常的一种,它一般由外设或外部输入产生,也可软件触发。中断的异常处理也被称作中断服务程序(ISR)。

二、Cortex-M3处理器中的嵌套向量中断控制器(NVIC)

本产品选用STM32L1系列单片机其处理器为Cortex-M3,在Cortex-M3处理器中存在一个嵌套向量中断控制器(NVIC)的中断控制器,它是可编程的且寄存器经过存储器映射,NVIC支持可编程中断优先级的数量。NVIC的地址是固定的且NVIC的编程模板与目前Cortex-M系列处理器都是一样的。

NVIC还支持多个系统异常,包括不可屏蔽中断(NMI)和处理器内部其他异常源。

嵌套向量中断控制器(NVIC)特性:

- 最多240个中断输入(1~15为系统异常,中断实际中在6~100之间,达到较小硅片面积,降低功耗),不可屏蔽中断(NMI)输入和系统异常。每个中断(NMI除外)都可以被单独的使能或禁止。

- 中断和系统异常具有可编程优先级。

- 嵌套中断/异常按照优先级先后处理。

- 向量中断/异常,处理器自动取出无需软件确认。

- 向量表可重定位在存储器多个区域(默认0x0)。

- 低中断等待。具有零等待状态存储系统,中断等待仅为12个周期。

- 中断和异常可用软件触发。

- 具有屏蔽中断和异常功能(NMI除外),也可将屏蔽为某个优先级之下。

- 多个优化用于降低不同异常上下文切换时的中断处理开销。

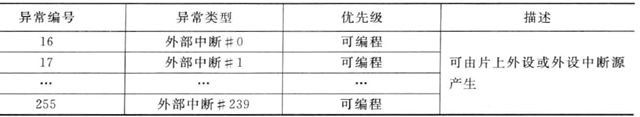

详细系统异常如下表:

中断类型如下表:

上面两个表详细阐述了异常/中断的编号、类型、优先级状态和具体的作用。

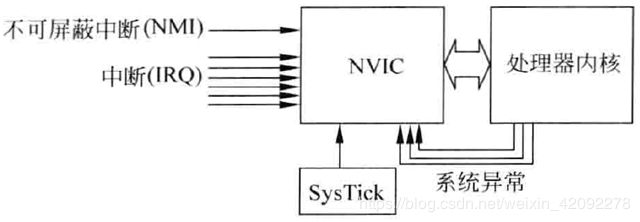

上图可知NVIC可以处理多个中断请求(IRQ)和一个不可屏蔽中断(NMI)请求,IRQ可由片上外设或外部中断输入通过I/O端口产生,NMI可由看门狗和掉电检测。处理器自身也是一个中断和异常源,比如处理器内部SysTick(系统节拍)定时器周期性产生中断或者系统错误事件状态。注:在Cortex-M3和Cortex-M4中断等待只有12个周期。

NVIC可以处理多种类型的中断源:

- 脉冲中断请求。中断请求至少持续一个时钟周期,NVIC会在收到该中断时,挂起状态保持到中断得到处理。

- 电平触发中断请求。中断得到处理前需要将中断源请求保持为高。

注:NVIC输入信号为高电平有效,实际外部中断输入设计会有所不同,片上系统逻辑会转换为有效高电平信号。

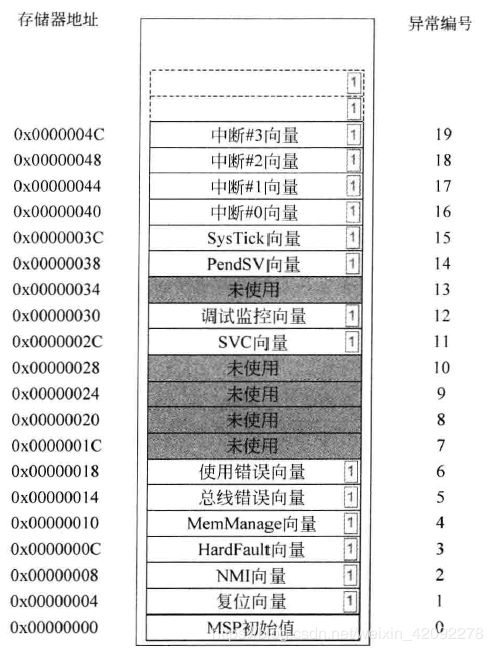

异常/中断入口:Cortex-M处理器会痛存储器的向量表中自动定位异常处理入口。

异常/中断抢占:每个异常都有优先级,当异常产生是MVIC会将输入异常优先级与当前运行任务优先级相比较,若新异常优先级较高,当前任务暂停,相关寄存器保存在栈空间,处理器开始处理新异常,当处理完成后,异常返回终止操作,处理器自动从栈恢复寄存器内容,并执行之前暂停任务。

中断屏蔽:NVIC有许多中断屏蔽寄存器。例如PRIMASK寄存器禁止除HardFault和NMI外所有异常;BASEPRI寄存器屏蔽低于特定优先级的异常或中断。

根据上图分析实际中异常/中断类型,NMI外设一般是看门狗或者掉电检测,IRQ外设一般是芯片自带ADC,DAC,比较器等,IRQ的I/O端口一般是外部芯片或者外围硬件电路产生的信号,SysTick(系统节拍)定时器产生中断用于有OS的芯片进行任务调度。

外设或I/O端口产生中断需要处理器处理服务流程如下:

- 处理器确认外设中断请求

- 进行优先级比较

- 处理器暂停当前执行任务

- 执行外设中断服务程序(ISR),可用软件清除中断请求。

- 处理完成后继续执行暂停任务

面经:

1.异常与中断之间的关系。

2.记住三个优先级最高的异常:复位(最高),NMI(第二)和硬件错误(第三)。

3.外设或I/O端口产生中断后,处理器接收到的处理流程。

4.中断源的信号类型:电平触发(高电平还是低电平?),脉冲触发(触发中断需要多少时间?),

三、优先级

在使用中断之前一般进行以下操作:

- 设置中断优先级(可以不设置,采用默认)

- 使能外设或I/O端口的触发中断开关

- 使能NVIC中断

Cortex-M3优先级配置寄存器为8位宽具有3个固定最高优先级(详见异常列表:复位,NMI,硬件错误)和256个可编程优先级(最多有128个抢占等级),但是实际可编程优先级数量远远低于256个,优先级越多会增加NVIC复杂度而且会增加功耗(增加逻辑门数)。优先级寄存器一般是高位有效(MSB),这样方便芯片间移植应用程序。

抢占等级划分:

优先级配置寄存器有8位宽为什么只有128个抢占等级?如下表所示:

优先级配置寄存器分为:抢占优先级和子优先级,从表中可以看出抢占优先级域最大只有7位,所以只有128个抢占优先级。因此在处理器判断如何执行中断时先判断抢占优先级,如果抢占优先级相同再判断子优先级。

面经:

1.中断初始化流程

2.可编程优先级个数?为什么这么多个?

3.抢占优先级(组优先级)与子优先级关系?抢占等级多少个?为什么抢占优先级有这么多个?

4.抢占优先级与子优先级哪个优先级更高?

四、向量表重定位

默认向量表地址从0开始。向量地址则为异常编号乘以4,向量表如下所示:

在CMSIS库中给SCB->VTOR赋予新地址进行重定位。

注:向量表基地址必须为下一个大小为2的整数次方

面经:

1.知道有向量表这个概念

2.向量表能否重定位?怎么定位?基地址有什么要求?

五、HAL库中断开发示例

设置中断流程三部曲:

- 设置抢占优先级

- 设置子优先级

- 使能中断

HAL库代码示例:

/*初始化端口操作这里不赘述*/

/*第一个参数:设置中断号,需要查询IO端口或者外设的中断号,

第二个参数:抢占优先级

第三个参数:子优先级*/

HAL_NVIC_SetPriority( EXTI0_IRQn, 6, 0 );

/*使能该中断号*/

HAL_NVIC_EnableIRQ( EXTI0_IRQn );

注:HAL库将设置抢占优先级和子优先级封装为一个接口,代码就缩减为两行代码。