vivado应用hardware manager进行JTAG调试常见问题

一、连接问题

有时会无法连接target,可能的原因。

A.目标硬件可能无法运行在缺省的target频率。

可以调整硬件target或者线缆的TCK管脚时钟频率。不同器件的特性可能不同。

B. IR(instruction register)长度不符

Vivado工具自动设置不同器件的IR长度,可能与实际不符。对于未知器件,需要检查确认IR设置正确。

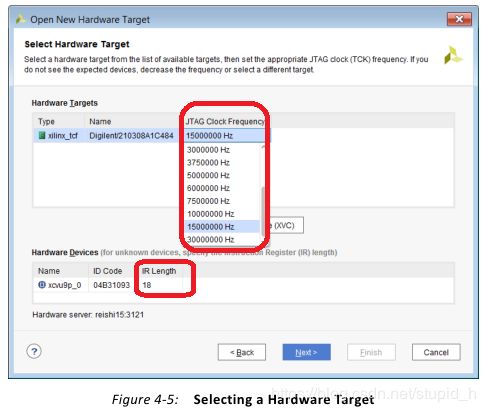

可以直接在Open New Hardware Target向导中设置IR。

见下图。

参考资料:xilinx手册UG908

二、检测不到debug core

在设计中加入调式诊断模块(debug core),但烧入后无法检测到。

WARNING: [Labtools 27-3361] The debug hub core was not detected.

Xilinx技术支持给出可能的解决办法:

- Ensure that the .bit file and the .ltx file assigned to this device match each other.

- Ensure that the capture clock to the ILA is a free running clock

- Ensure that timing requirement has been met after inserting Debug cores.

- The error can be caused by a Signal Integrity issue on the board.

- A case was found where the issue was caused by a bad USB Cable.

- In one case creating a new project resolved the error.

(1) 捕获时钟不存在

debug hub时钟最好是自由时钟,尽量不受其他因素干扰,确保上电后就有信号。debug hub时钟存在之后,再确认ILA时钟存在。

有时需要修改debug hub的时钟。Xilinx推荐加debug core的方式是在sythesis阶段,不用修改代码,通过图形化方式加,结果是保存在约束文件###.xdc中。在图形界面中想修改debug hub时钟是很困难的,可以直接在约束文件中修改。

在约束文件###.xdc中找到类似以下的语句

connect_debug_port dbg_hub/clk [get_nets dclk_IBUF_BUFG]

后面的get_nets dclk_IBUF_BUFG就是debug hub的时钟,修改即可。

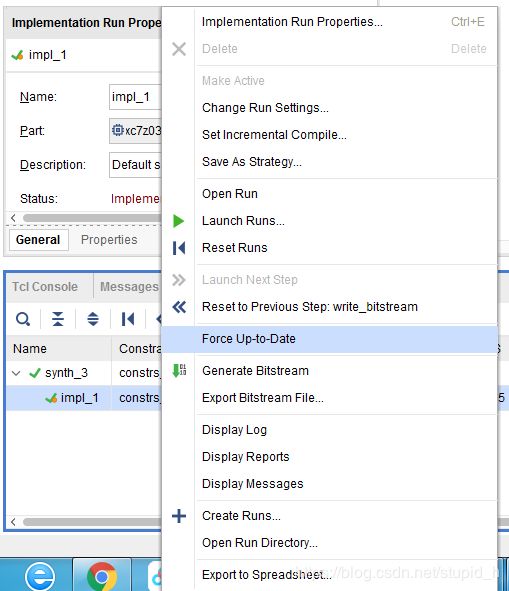

约束文件修改会导致综合过期,会再次重新综合。实际不必要,可以直接进行implementation。只要强制修改就可以跳过再次综合,见上图。

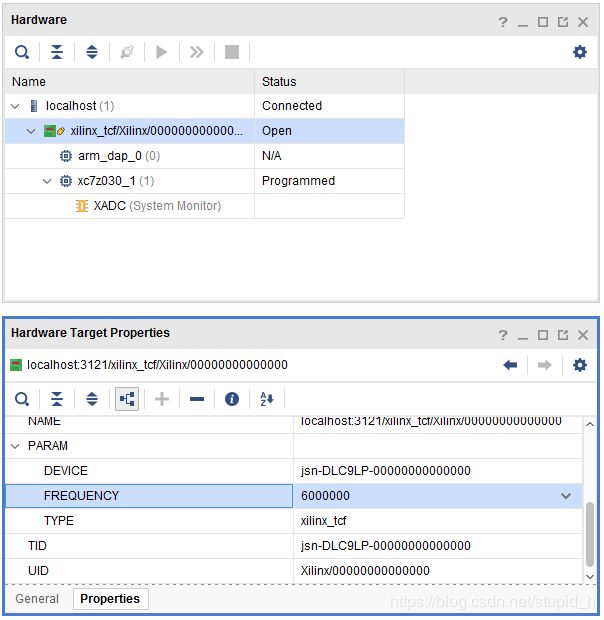

(2) JTAG时钟频率问题

JTAG clock should be half or less than half of ILA frequency.

比如,ILA时钟是25MHz,则JTAG时钟应小于等于12.5MHz.

(3) 参数配置

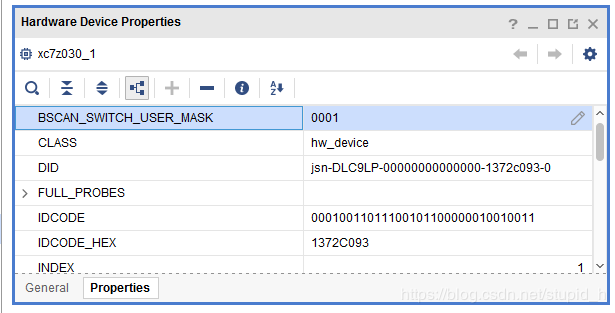

C_USER_SCAN_CHAIN = 1 ,而且BSCAN_SWITCH_USER_MASK = "0001"

在TCL窗口输入 get_property C_USER_SCAN_CHAIN [get_debug_cores dbg_hub] 可得到C_USER_SCAN_CHAIN

在Hardware Device Proerties窗口可以查到BSCAN_SWITCH_USER_MASK

(4) debug core不匹配

使用SD卡启动系统,已经加载了FPGA bit文件(非调试版本)。然后手动加载bit文件(带调试模块),并给出调试信息文件###.ltx,可能出现如下错误。

ERROR: [Common 17-70] Application Exception: CORE_LOCATION mismatch

这种情况,只需要关闭Hardware Manager,重新打开,并Open new hardware,再重新加载就可以了。

最好每次使用完hardware manager,先关闭,再下电设备。

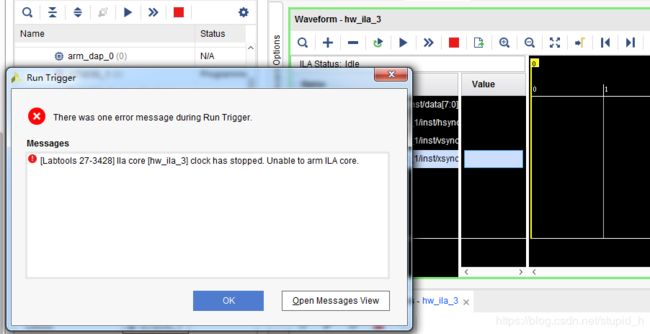

三、 ILA不能正常工作

(1) 不能使用ILA core

很可能是ILA时钟问题。

在加ILA信号的时候,将相关信号mark debug,然后使用Setup Debug,自动生成ILA,时钟也会自动生成,一般就不会有问题。