Vivado18.3-ILA(集成逻辑分析器)的使用 学习笔记

本文内容学习自正点原子ZYNQ领航者FPGA视频-P7

1.ILA介绍

ILA(Integrated Logic Analyzer)集成逻辑分析器:即Vivado的在线逻辑分析仪,其借用了传统逻辑分析仪的理念以及大部分的功能,并利用FPGA 中的逻辑资源,将这些功能植入到FPGA 的设计当中。ILA是用IP核的形式实现的。

在线逻辑分析仪通过一个或多个探针(Probe)来采集希望观察的信号,然后通过片内的JTAG 硬核组件,来将捕获到的数据传送给下载器,进而上传到Vivado IDE 以供用户查看。Vivado IDE 也能够按照上述数据路径,反向地向FPGA 中的在线逻辑分析仪传送一些控制信号。

Vivado 提供了三种具有不同集成层次的插入ILA 方法:

1.1HDL 实例化调试探针流程

ILA IP 核可以在IP Catalog(IP 目录)中找到,并对其进行配置,以符合所需的调试需求。这是最直接的方法,但其灵活性也较差。在调试工作完毕之后,还需要在HDL 源代码中删除ILA IP 核,然后重新综合并实现,以生成最终的比特流。

1.2网表插入调试探针流程

在综合后的网表中,分别标记要进行调试观察的各个信号,然后通过一个简单的“Setup Debug”向导来设置各个探针和ILA IP 核的工作参数,然后工具会根据用户设置的参数,自动地生成各个ILA IP 核。在此流程中,用户不需要修改HDL 源代码,并且能够单独控制每个ILA IP 核以及每个探针,这样就提供了很大的灵活性。用户设置的调试信息会以TclXDC 调试命令的形式保存到XDC 约束文件中,在实现阶段,Vivado 会读取这些XDC 调试命令,并在布局布线时加入这些ILA IP 核。在调试工作完毕之后,用户就可以在综合后的网表中删除ILA IP 核,然后再对设计进行实现,以生成最终的比特流。

1.3集成层次最低的方法,是手动地在XDC 约束文件中书写对应的Tcl XDC 调试命令,在实现阶段工具会自动读取这些命令,并在布局布线时加入这些ILA IP 核。在调试工作完毕之后,用户还需要在XDC 约束文件中删除这些命令,然后实现最终的设计。

2.ILA使用方法(1)HDL 实例化调试探针流程

“HDL 实例化调试探针流程”需要在HDL 源代码中实例化ILA IP 核。我们点击“Flow Navigator”窗口中的“IP Catalog”按钮,如下图所示:

Search一栏搜索ILA,然后双击打开。

弹出Customize IP 窗口,是用来配置IP核的。

最上方“Component Name”一栏用于设置ILA IP 核的名称。

General Options页面用于设置ILA IP 核的总体设置。

Monitor Type 监控类型:也就是选择接口类型,这里选Native

Number of Probes 探针数量:注意这个跟信号位宽没关系,一个信号就是一个probes。

Sample Data Depth: 用于设置采样深度,也就是采样点数,在每个采样时钟下,ILA 都会将捕获到的探针信号的值送入FPGA的RAM 中。

剩下是一些高级设置,暂时用不到。待补充。

Probe_Ports(0..0) 页面用于对每个探针的参数进行设置

因为要观测的信号为 rst_n,[1:0] led,[25:0] cnt,所以三个探针分别设为1,2,26位的。创建完成之后点击OK

接下来就会弹出“Generate Output Products”对话框,我们保持默认设置,直接点击“Generate”即可,此时Vivado 就开始对该ILA IP 核进行OOC 综合了。如下图所示:

OOC(Out of context) 就相当于现在在全局综合执勤,直接将这个IP核模块综合一次,并生成输出产品(GenerateOutput Products),包括综合后的网表等各种文件。然后固定下来,以后如果对整体设计修改再综合的时候,会把这个模块视为黑盒子,不再对它进行综合,节约时间。如果是Global方式就是每次综合都会对它综合。并且OOC 模块可以是来自IP catalog 的IP、来自Vivado IP Integrator 的block design或者顶层模块下手动设置为OOC 方式的任何子模块。

OOC综合之后,在Sources一栏就能找到添加到工程中的ip核,然后在IP Sources一栏点开这个文件就能找到例化用的模板文件

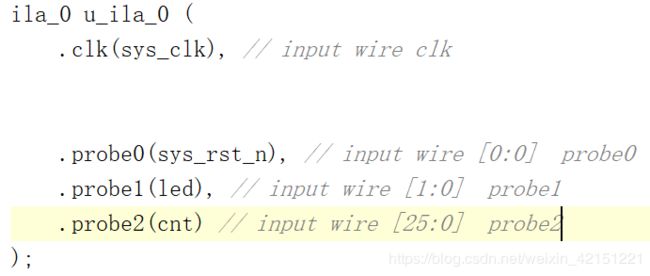

然后进行例化,注意这里clk就是用来采样的时钟。这里务必使用与待观测信号同步的时钟。

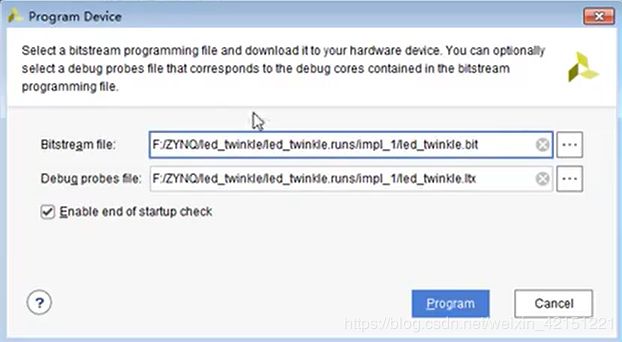

例化完成之后,生成bit流即可。这时下载bit流的时候会多一个.itx文件 这就是ILA的文件。

程序下载成功后,会多出观测窗口。

(1)自动触发开关,它和“开始触发”按钮联合在一起使用。若打开了此选项,则在ILA 开始运行触发(即点击了“开始触发”按钮)后,会不断地对触发条件进行检测,每次触发条件被满足时(即cnt 计数到了25_000_000),都会将RAM 中存储的所有的探针值数据上载到Vivado,Vivado 上显示的波形也会随之不断更新,直到用户点击了“停止触发”按钮。若没有点击此选项,则在ILA 开始运行触发(即点击了“开始触发”按钮)后,在检测到触发条件得到满足并完成了上载数据之后,就会停止触发,等待用户下一步的指令。

(2)开始触发,它和“自动触发开关”按钮联合在一起使用。点击之后ILA 就会开始进行触发操作。

(3)立即触发,立即将当前ILA RAM 中的数据上载到Vivado,而不管触发条件是否得到满足。

(4)停止触发,停止当前正在进行的触发活动。

这个窗口的右下角,Trigger Setup 就可以设置触发条件

3.ILA使用方法(2)网表插入调试探针流程

可以在综合之后的网表中手动选择网络并点击“Mark_Debug”按钮;

也可以在综合之前在HDL 代码中为想要观察的reg 或wire 信号添加“Mark Debug”综合属性

3.1综合之后的网表中手动选择网络并点击“Mark_Debug”按钮

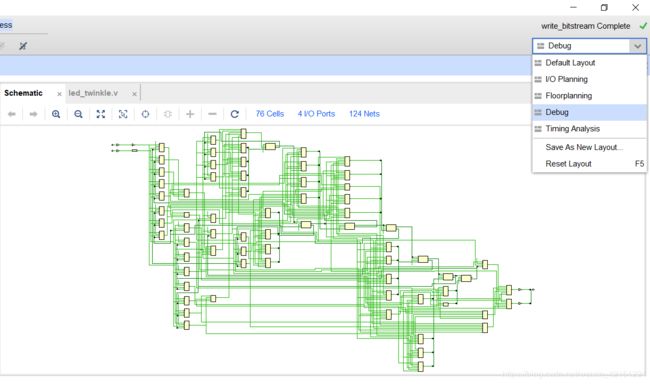

首先综合之后,打开综合设计文件

右上角将窗口选择为Debug

右键想要观测的信号,选择Mark Debug

3.2综合之前在HDL 代码中为想要观察的reg 或wire 信号添加“Mark Debug”综合属性

其中“(* mark_debug = “true” *)”必须紧挨在变量声明的前面。这样,在综合完成之后并打开综合后的设计时,cnt 信号就自动被标记了“Mark Debug”属性。此外,被添加了(* mark_debug = “true” *)属性的reg或wire 信号不会被工具优化掉。

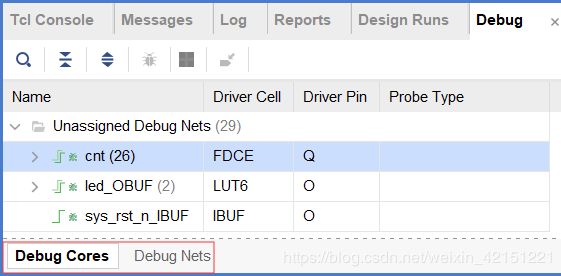

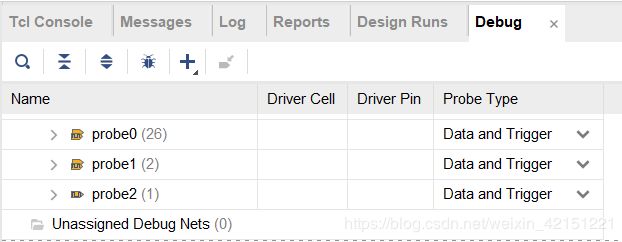

添加完成之后重新综合。这时候下方Debug一栏就有了reg信号。现在进行Set Debug点击这个小蜘蛛。

在“Debug”子窗口中,又包含两个选项卡“Debug Cores”和“Debug Nets”。这两个选项卡都用于示所有的已标记为“Mark_Debug”的信号。不同之处在于,“Debug Cores”选项卡是一个更加以ILA IP核为中心的视图,所有已标记为“Mark_Debug”的信号并且已经被分配到ILA 探针的信号都会被显示在各个ILA IP 核的视图树下,已标记为“Mark_Debug”的信号但是还没有被分配到ILA 探针的信号被显示在“Unassigned Debug Nets”下,当然也可以在其中查看和设置ILA IP 核的各种属性和参数。“Debug Nets”选项卡仅显示已标记为“Mark_Debug”的信号,但不显示ILA IP 核,所有已标记为“Mark_Debug”的信号并且已经被分配到ILA 探针的信号都会被显示在“Assigned Debug Nets”下,已标记为“Mark_Debug”的信号但是还没有被分配到ILA 探针的信号被显示在“Unassigned Debug Nets”下。

点Next

这里可以选择时钟,软件已经自动添加了。点击Next

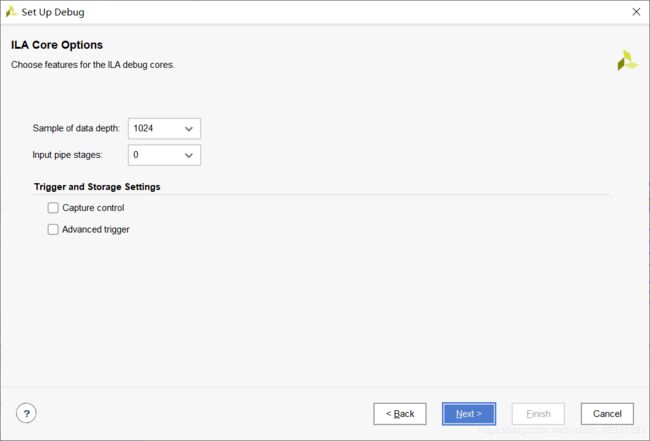

这里选择采样深度,其它高级选项先不管它。

“Input pipe stages”用于设置待测信号和其采样时钟之间的同步级数。如果在上一个设置时钟域页面中,存在与其采样时钟之间是异步的待测信号,则为了避免亚稳态,此数值最好不要低于2。由于本例中的两个待测信号的其采样时钟是同步的,所以可以设置为0。

点击Finish

然后点击Ctrl+S保存,然后点击ok

在“Debug”子窗口中的“Debug Cores”选项卡中,可以看到Vivado 已经添加了ILA IP 核,并且“Unassigned Debug Nets”目录下已经没有未被分配的信号了,如下图所示

之后再进行下载bit流,剩下的观测操作和HDL方式都是一样的。