FPGA数字信号处理(24)数字相关器设计(简化结构)

广义地讲,数字相关器件就是完成两路信号之间的相关运算。该技术应用于帧同步字检测、扩频接收机、误码矫正、模式匹配等领域。但就数字相关器本身实现的功能而言,具有更为广泛、通用的应用,如在“基于可编程逻辑器件FPGA的数字相关器_马玉良”这篇论文中,就将数字相关器中应用在动态光散射技术中的散射光强的自相关函数计算上。

本文将先讨论数字相关器在帧同步字检测应用中的设计方法。本文使用简化结构实现,第25篇采用了经典结构实现https://blog.csdn.net/fpgadesigner/article/details/81356491。

帧同步字检测

在数字通信的数据传输过程中,为了保持数据在传输过程中的同步,在发送端发送数据前插入帧同步字,在接收端解调后的数据流中检测帧同步字,以确定帧位置和帧定时信息。

帧同步字一般为一个特定的序列,当在接收端检测到一组连续码元与预设的帧同步字吻合时,表示数据同步,开始接收数据。帧同步字的选取有如下要求:

- 与信息码元区别度大;

- 具有尖锐单峰特性的自相关函数;

- 码长适当,保证传输效率。

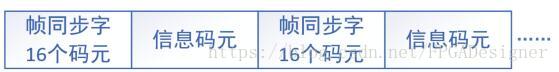

常用的帧同步字有全1码、全0码、10交叉码和巴克码。举一个简单的例子,GSM中一个帧结构为1250个连续码元,前16个为帧同步字,后1234个为信息码元:

接收端检测到帧同步字时,开始接收信息码元;1234个接收时钟周期之后,一帧数据传输完成。之后再开始检测下一帧数据的帧同步字。

数字相关器

完成帧同步检测的模块便是数字相关器,进行两个数字信号之间的相关运算。简单来说,就是比较两个输入的数字序列之间有多少位相同,多少位不同。完成该工作的基本元件便是异或门。

比如以16Bits的帧同步字为例,当检测到输入的16Bits码元与预设的帧同步字完全相同时,数字相关器便输出一个相关峰值表示帧同步。本设计中的相关峰值选择为高电平脉冲即可。码元的输入方式可以选择串行输入和并行输入两种。

FPGA设计思路

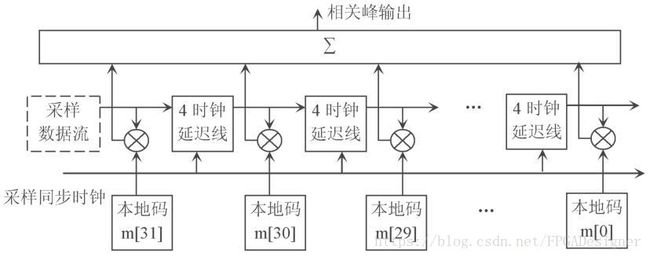

数字相关器的经典结构如下:

延时线时钟取值为采样时钟与数据码元时钟的倍数。当运算数据只有1bit时,可以采用异或门/同或门代替乘法器完成数字相关检测,节约乘法器资源。

设计目标如下:输入方式采用并行输入(省略移位寄存器);码元输入速率与系统采样时钟相同(100MHz);两个输入码元A和B为16Bits,A为预设的帧同步字(设置为10交叉码)。

由于两个16位数据的异或结果有2^16=256种,在编写代码时比较麻烦。可以采用如下方法:设计一个4位数字相关器,16位的原始序列依次拆分为4组4位,分别统计结果再相加。

数字相关器的输出设置一个5Bits宽的Out,负责统计两组序列中相同位数的格式;设置一个单比特pulse,高电平表示检测到一组完全相同的序列,pulse直接取Out的最高位即可(Out只有在取值为16,即序列完全相同时,最高位才会置1)。

无流水线设计

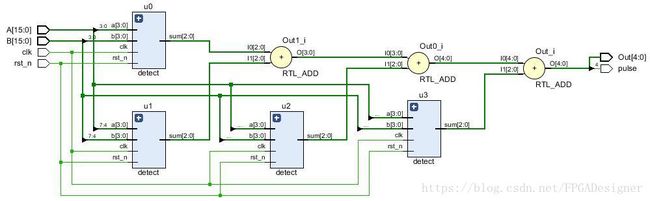

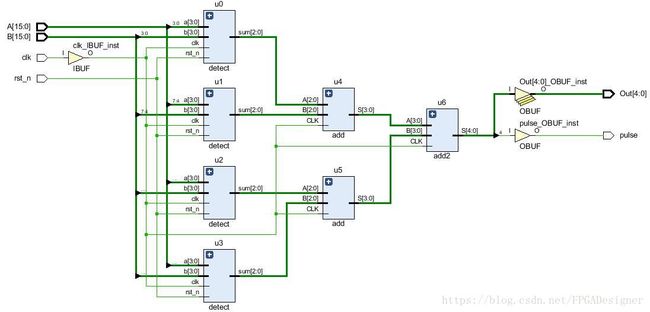

根据上述设计思路,在Vivado开发环境下完成Verilog HDL代码设计,对应的RTL原理图如下:

4个4位数字相关器完成对16Bits并行输入的数字序列的检测,结果直接相加作为输出。仿真结果如下:

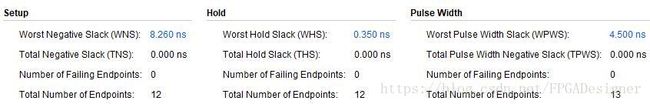

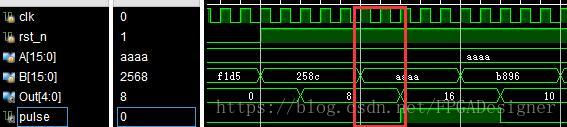

A设置为10交叉码,当B序列与A相同时,Out为16,且pulse输出高电平脉冲。系统时钟周期约束为10ns(100Mhz),时序分析报告如下:

建立时间的最差负裕量为8.26ns,满足时序要求。

流水线化设计

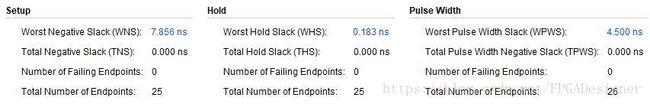

从上面设计的RTL图中可以看出加法器采用组合逻辑实现,组合逻辑会带来一定的路径延迟。考虑将加法器流水线化,缩短延时路径,从而优化时序。改进后设计的RTL原理图如下:

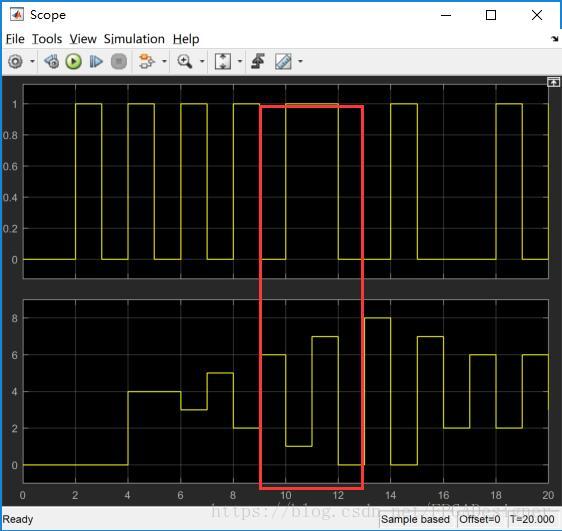

第一级先将4个4位数字相关器的输出两两相加,结果再使用一级加法器相加。两级加法器的Latency都设置为1,因此系统会带来两个时钟周期的延时。Vivado中仿真结果如下图:

从图中可以清楚地看到流水线带来的延时。系统时钟周期约束为10ns(100Mhz),时序分析报告如下:

可以看到最差建立时间和保持时间都有一定程度的改善。不过加法器的流水线化设计不会像乘法器的流水线化提升那么明显。

分别进行综合后资源分析:无流水线的设计使用了37个LUT,12个Slice;流水线化的设计使用了39个LUT,25个Slice。流水线带来了速度上的提升,但增加了额外资源的消耗,尤其是触发器资源的消耗。

4位数字相关器代码

从上面的RTL视图中也可以看出整体设计都很简单,这里只列出4位数字相关器子模块的代码:

//------------------------------------------------------

// 异或进行4位数字相关检测

//------------------------------------------------------

module detect

(

input clk,

input rst_n,

input [3:0] a,b,

output [2:0] sum

);

reg [2:0] sum_reg;

wire [3:0] ab = a ^ b;

always @(posedge clk or negedge rst_n)

if (!rst_n) sum_reg <= 'd0;

else

case(ab)

'd0: sum_reg <= 'd4;

'd1,'d2,'d4,'d8: sum_reg <= 'd3;

'd3,'d5,'d6,'d9,'d10,'d12: sum_reg <= 'd2;

'd7,'d11,'d13,'d14: sum_reg <= 'd1;

'd15: sum_reg = 'd0;

default: sum_reg <= 'd0;

endcase

assign sum = sum_reg;

endmodule在case中对异或结果进行检测,统计其中位数相同(即异或结果为0)的个数。本文设计的数字相关器很简单。在扩频通信中,使用到的数字相关器会是经典的“移位寄存器+乘法器+累加器”结构,将在后面的文章中介绍。其实本文的设计也是该结构的一种特例。

System Generator设计方法

System Generator是Xilinx推出的一款模型设计工具,在Simulink环境下完成设计,可以搭建高效快速的仿真系统,并将设计导出到HDL模型。

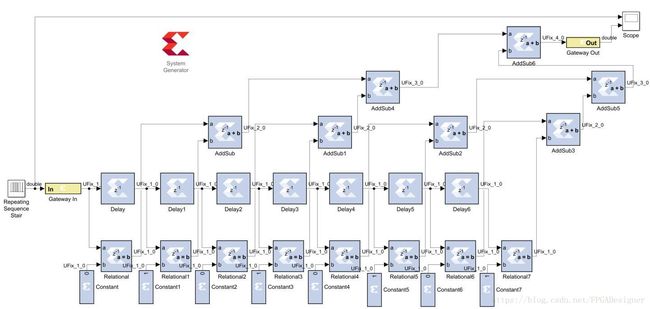

本章设计将实现数字相关器的经典结构,设计方式采用串行输入,需要移位寄存器来缓存数据。为了简化模型,码元设置为8Bits位宽,系统时钟仍为100MHz。System Generator的模型连接图如下:

中间为延迟寄存链;下面为相关检测部分,Constant模块存储本地码元(10交叉码),Relational模块完成数据比较;上面为累加器模块,包含三级加法器。很明显,系统为流水线设计,从输入到输出共有4级延时。仿真结果如下图:

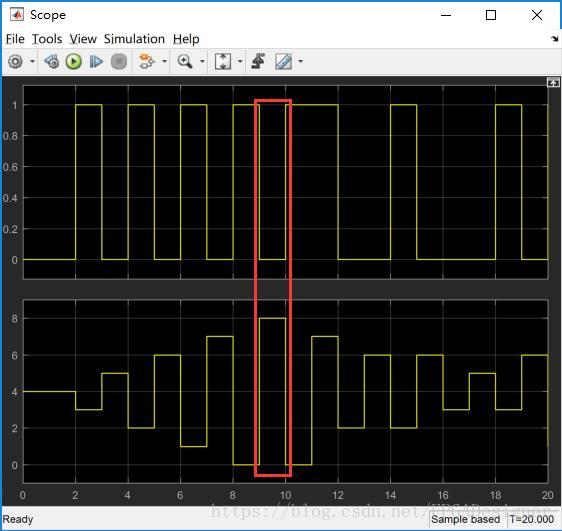

在输入与本地码元相同的10101010序列后,经过4个时钟延时,累加器才输出8,表示两序列完全相同。比较有无流水线对系统性能的影响。将模型中加法器、比较器的Latency设置为0,表示使用纯组合逻辑实现。运行仿真结果如下:

组合逻辑没有延时,因此在检测到10交叉序列后累加器马上得到了结果。运行时序分析,没有任何流水线的设计最差路径延时为3.804ns,最大工作频率约为250MHz;流水线设计后的最差路径延时为1.872ns,最大工作频率约为500MHz,提升了2倍多,当然如上一章所述,所消耗的资源也有所增加。