PS与PL协同设计实现GPIO

前面的和上一结差不多,新建工程,新建IP核(ARM_CORE),再放置ZYNQ的处理器,Run Block后就双击图标进行配置和剪裁

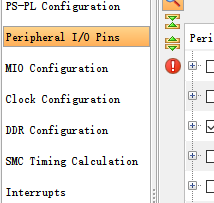

Peripheral 里面只要UART,MIO里的APP里的Timer去掉,Clock里面PL里面FCLK不能去,用的就是这个100M的时钟

还需要加复位控制模块:图标旁边右击-Add IP-搜reset

如下图

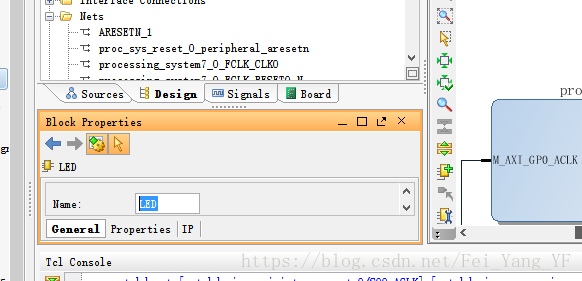

输出的时钟(FCLK-CLK0)就是给AXI(FPGA的逻辑部分)的时钟,连接reset的时钟也是这个, PS部分也输出一个时钟(FCLK-RESETO-N)到ext_rest_in。

然后再放一个交换模块add IP-interconnect(搜索词),这个东西就是把一路的AXI接口转换成多路,是多路对多路(最多16路),一个ZYNQ里面有4个类似交换模块,双击此模块,按下图设置

再放两个gpio(快捷键Ctrl+I),接着按下图连线

单击上图第一个GPIO1模块,按下图操作,

注:

对端口的网络名称进行修改

,保证

生成的

TOP和例子提供的XDC引脚约束文件一致(包括大小写)

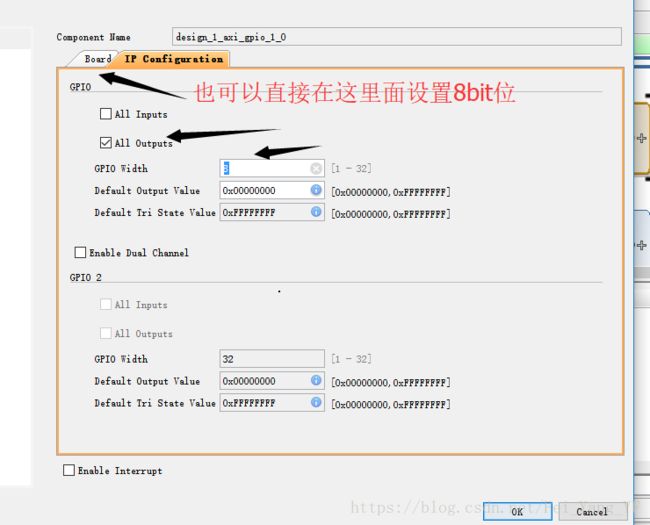

意思是用它输出LED,接下来双击此模块,

同样的操作将GPIO0命名位sw,双击设置,但是是把输出改为输入,宽度改为8位

然后把LED的GPIO口扩展一下,旁边右击-Make External,sw也是这样做引出去,前者引出脚命名位led,后者命名为sw,在上面方框里可以看见其名字下面的底层文件

整理页面:右击Regenerate Layout

然后保存

两个模块挂载上去之后,再赋一个地址,在Address Editor栏里,因为FPGA控制这些外设要通过地址,而地址要映射入FPGA的寻址地址:一直点开下拉栏,在sw和led上右击选择Assign Address,然后保存,模块设计完

在Source的Design下面的文件(.bd文件)上右击,点击Genereate Output Products产生它所调用的外围模块,再产生

Verilog代码,同样的位置点击Create HDL Wrapper

双击.v文件,第一部分是ps部分文件,Ctrl+F搜索关键词

注:如果发现代码有错,比如8位写成32位了,在连线图上改一下,再重新生成Verilog文件,再在.v文件上方点击一下Reload

在程序里面8位的led或sw引脚是FPGA的引脚,要在约束文件(管脚对应文件)中对应上,主要分指定引脚和电平,是一堆代码

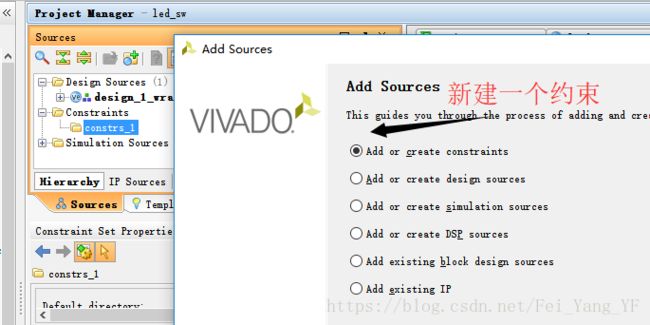

之前新建一个约束,下图

然后把那些代码拷进PIN_SET里面,再保存,然后生成比特流

生成比特流失败:

前面对端口的网络名称进行修改,在2015.4版本的VIVADO是不支持的。这就导致不能修改,如果不修改,生成的TOP就和例子提供的XDC引脚约束文件不一致了。解决原则就是保证TOP层的引脚和XDC引脚名称完全一致(包括大小写)。具体有两个可以操作的方法:

1,修改XDC文件,与TOP的一致。

2,修改顶层,与XDC文件一致。如果这个顶层是自动生成的,则需要再次生成之后修改会被覆盖。

XDC文件就是上面约束文件里面的那堆代码(后缀是LED和SW)

下面是第二种方法改正流程:

删除原工程,新建工程-建立块设计(建立IP核)-添加处理器(ZYNQ7)-填充一下(

Run Block)-加上两个GPIO模块-左键单击在右面改名字-双击改配置(都是8位,SW是输入,LED是输出)-端口引出(右击选Make External)-点击引出的端口,改成和上面一样的名字

然后自动连接(最上面的绿字RCA,进去后左面栏全选加上复位和AXI开关转换模块)-上一步把地址分配好(地址高低和放置模块的先后顺序有关)-在Sources的.bd文件上右击Create HDL

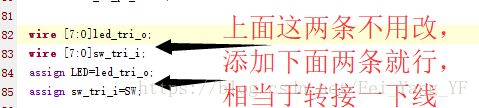

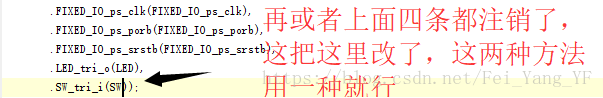

此时顶层文件(.bd文件上面的.v文件)里面的代码可以编辑,把led_tri_o改成LED,sw_tri_i改成SW

然后新建引脚锁定文件(右击Add source,PIN_SET),把代码拷进来,保存生成比特流,这是第二种方法

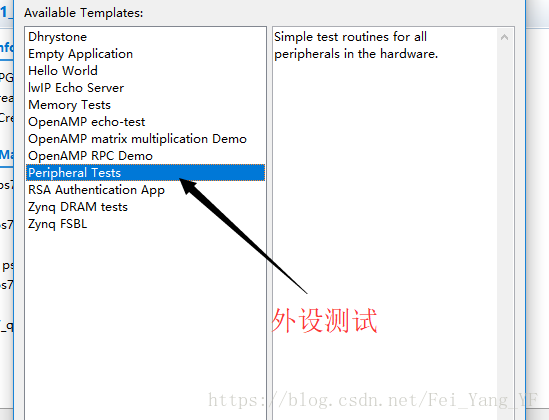

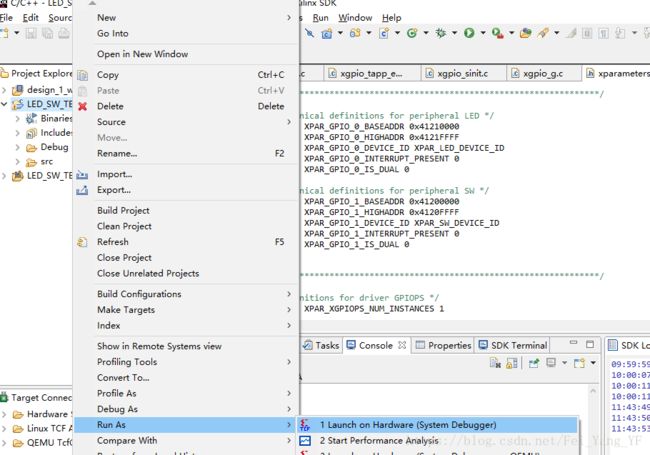

第一种方法稍后再说,先接上上一次出错前的流程:导入到SDK里面(File路径下)-新建应用项目(命名完成后不选Hello World选应用外设如下图)

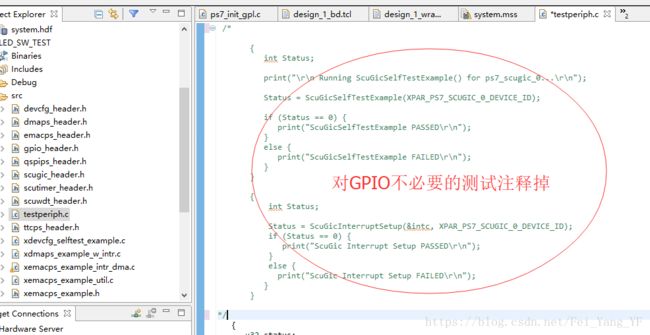

然后

快速查看某个函数,选中按F3跳转

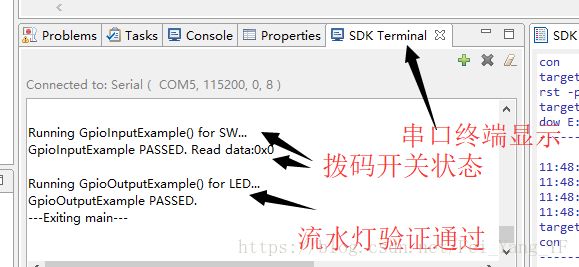

保存-配置串口(SDK自带的在下面栏Terminal加号上)115200-下载比特流

下载进去进行调试

切换到DEBUG模式窗口,在下面串口那栏(SDK Treminal)

下面是对原有程序进行简化:写小灯,读拨码开关

然后保存,保存就是编译,再运行(上面蓝三角),程序会一直运行,现象是灯收开关控制

现在是现成的IP核,直接调用就行,以后要自己做核