【 Verilog HDL 】不同抽象级别的Verilog HDL模型之门级结构描述

本博文参考:《从算法设计到硬件逻辑实现》,仅供学习交流使用。

Verilog模型可以是实际电路不同级别的抽象。这些抽象的级别和它们对应的模型类型共有以下五种:

1) 系统级(system)

2) 算法级(algorithmic)

3) RTL级(RegisterTransferLevel):

4) 门级(gate-level):

5) 开关级(switch-level)

对于数字系统的逻辑设计工程师而言,熟练地掌握门级、RTL级、算法级、系统级是非常重要的。而对于电路基本部件(如门、缓冲器、驱动器等)库的设计者而言,则需要掌握用户自定义源语元件(UDP)和开关级的描述。

一个复杂电路的完整Verilog HDL模型是由若干个Verilog HDL模块构成的,每一个模块又可以由若干个子模块构成。这些模块可以分别用不同抽象级别的Verilog HDL描述,在一个模块中也可以有多种级别的描述。利用Verilog HDL语言结构所提供的这种功能就可以构造一个模块间的清晰层次结构来描述极其复杂的大型设计。

门级结构描述

一个逻辑网络是由许多逻辑门和开关所组成,因此用逻辑门的模型来描述逻辑网络是最直观的。Verilog HDL提供了一些门类型的关键字,可以用于门级结构建模。

下面列出了八个基本的门类型(GATETYPE)关键字和它们所表示的门的类型:

and 与门

nand 与非门

nor 或非门

or 或门

xor 异或门

xnor 异或非门

buf 缓冲器

not 非门

门与开关的说明语法可以用标准的声明语句格式和一个简单的实例引用加以说明。门声明语句的格式如下:

<门的类型>[<驱动能力><延时>]<门实例1>[,<门实例2>,…<门实例n>];

门的类型是门声明语句所必需的,它可以是Verilog HDL语法规定的26种门类型中的任意一种。驱动能力和延时是可选项,可根据不同的情况选不同的值或不选。门实例1是在本模块中引用的第一个这种类型的门,而门实例n是引用的第n个这种类型的门。

最后我们用一个具体的例子来说明门类型的引用:

nand #10 nd1(a,data,clock,clear);

这说明在模块中引用了一个名为nd1的与非门(nand),输入为data、clock和clear,输出为a,输出与输入的延时为10个单位时间。

下面这个例子仅供说明语法的运用:

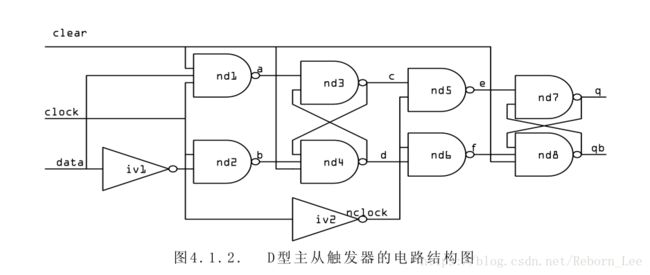

下面的例子是用Verilog HDL语言描述的D型主从触发器模块,通过这个例子,我们可以学习门级结构建模的基本技术。

module flop(data,clock,clear,q,qb);

input data,clock,clear;

output q,qb;

nand #10 nd1(a,data,clock,clear),

nd2(b,ndata,clock),

nd4(d,c,b,clear),

nd5(e,c,nclock),

nd6(f,d,nclock),

nd8(qb,q,f,clear);

nand #9 nd3(c,a,d),

nd7(q,e,qb);

not #10 iv1(ndata,data),

iv2(nclock,clock);

endmodule

在这个Verilog HDL 结构描述的模块中,flop定义了模块名,设计上层模块时可以用这个名(flop)调用这个模块;module, input, output, endmodule等都是关键字; nand表示与非门;#10表示10个单位时间的延时;nd1,nd2,......,nd8,iv1,iv2分别为图4.1.2中的各个基本部件,而其后面括号中的参数分别为图4.1.2 中各基本部件的输入输出信号。

我想这里例子的意义并不是让你能用这些基本的门元件来编写一个D触发器,更重要的地方在于懂得如何使用这些基本的原语,门级原语属于很基本的元件了,作为一个学习硬件的人来说,这是必须掌握的。

看到上面这个图,真的是信了你的邪,至少让我是不可能直接用门级原语描述出这个电路图的;但是从电路图出发来写成Verilog HDL语言的形式还是可以的。这些都是废话了,上面已经说了,掌握门级原语的目的也并非让你去描述一个触发器之类的,此时,且掌握如何引用原语罢了。

由已经设计成的模块来构成更高一层的模块

如何引用已经设计成的模块,也就是如何实例化,下面有两种方式,推荐第二种。

如果已经编制了一个模块,如4.1.2.中的flop,我们可以在另外的模块中引用这个模块,引用的方法与门类型的实例引用非常类似。只需在前面写上已编的模块名,紧跟着写上引用的实例名,按顺序写上实例的端口名即可,也可以用已编模块的端口名按对应的原则逐一填入,见下面的两个例子:

1) flop f1op_d( d1, clk, clrb, q, qn);

2) flop flop_d (.clock(clk),.q(q),.clear(clrb),.qb(qn),.data(d1));

这两个例子都表示实例f1op_d引用已编模块flop。从上面的两个例子可以看出引用时f1op_d的端口信号与flop的端口对应有两种不同的表示方法。模块的端口名可以按序排列也可以不必按序排列,如果模块的端口名按序排列,只需按序列出实例的端口名。(见例1)。如果模块的端口名不按序排列,则实例的端口信号和被引用模块的端口信号必需一一列出(见例2)。

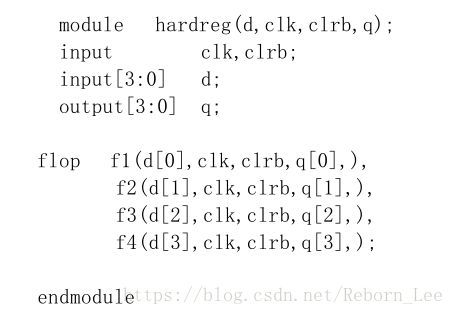

下面的例子引用了上面设计好的一个触发器模块设计一个4位的寄存器:

在上面这个结构描述的模块中,hardreg定义了模块名;f1,f2,f3,f4分别为图5中的各个基本部件,而其后面括号中的参数分别为图5中各基本部件的输入输出信号。请注意当f1到f4实例引用已编模块flop时,由于不需要flop端口中的qb口,故在引用时把它省去,但逗号仍需要留着。

显而易见,通过Verilog HDL模块的调用,可以构成任何复杂结构的电路。这种以结构方式所建立的硬件模型不仅是可以仿真的,也是可综合的,这就是以门级为基础的结构描述建模的基本思路。