【FPGA】ROM/EPROM的设计(使用case的方式初始化)

上篇博文:【FPGA】ROM/EPROM的设计(使用加载文件的方式初始化),提到了这篇博文中要用的方式初始化ROM,在代码中用case语句的方式,给一个地址,给一个数据。

很容易,通过异步的方式来给出代码设计:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Create Date: 2019/05/29 11:25:09

// Design Name:

// Module Name: rom_using_case

//////////////////////////////////////////////////////////////////////////////////

module rom_using_case (

input [3:0] address , // Address input

output reg [7:0] data , // Data output

input read_en , // Read Enable

input ce // Chip Enable

);

always @ (ce or read_en or address)

begin

case (address)

0 : data = 10;

1 : data = 55;

2 : data = 244;

3 : data = 0;

4 : data = 1;

5 : data = 8'hff;

6 : data = 8'h11;

7 : data = 8'h1;

8 : data = 8'h10;

9 : data = 8'h0;

10 : data = 8'h10;

11 : data = 8'h15;

12 : data = 8'h60;

13 : data = 8'h90;

14 : data = 8'h70;

15 : data = 8'h90;

endcase

end

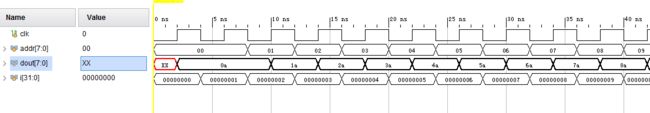

endmodule仿真波形如下:

给出RTL原理图:

可见,ce和read_en并没有用,所以可以去掉,经过测试:

//always @ (ce or read_en or address)

//always@(*)

always@(address)

begin

case (address)

0 : data = 10;

1 : data = 55;

2 : data = 244;

3 : data = 0;

4 : data = 1;

5 : data = 8'hff;

6 : data = 8'h11;

7 : data = 8'h1;

8 : data = 8'h10;

9 : data = 8'h0;

10 : data = 8'h10;

11 : data = 8'h15;

12 : data = 8'h60;

13 : data = 8'h90;

14 : data = 8'h70;

15 : data = 8'h90;

endcase

end

以上三种写法,仿真以及RTL图一样。

给出测试文件:

`timescale 1ns / 1ps

module rom_using_case_tb;

reg [3:0] address;

reg read_en, ce;

wire [7:0] data;

integer i;

initial begin

address = 0;

read_en = 0;

ce = 0;

//#10 $monitor ("address = %h, data = %h, read_en = %b, ce = %b", address, data, read_en, ce);

for (i = 0; i < 16; i = i + 1 ) begin

#5

address = i;

read_en = 1;

ce = 1;

#5

read_en = 0;

ce = 0;

address = 0;

end

end

rom_using_case U_rom_case(

.address(address) , // Address input

.data(data) , // Data output

.read_en(read_en) , // Read Enable

.ce(ce) // Chip Enable

);

endmodule

参考链接:http://www.asic-world.com/examples/verilog/rom_eprom_eeprom.html

再给出一个与时钟相关的同步设计,参考链接:https://blog.csdn.net/ic7x24/article/details/89735950

module mini_rom (

input clk,

input [ 7:0] addr,

output reg [ 7:0] dout

);

always @(posedge clk) begin

case(addr)

8'h00: dout <= 8'h0A;

8'h01: dout <= 8'h1A;

8'h02: dout <= 8'h2A;

8'h03: dout <= 8'h3A;

8'h04: dout <= 8'h4A;

8'h05: dout <= 8'h5A;

8'h06: dout <= 8'h6A;

8'h07: dout <= 8'h7A;

8'h08: dout <= 8'h8A;

8'h09: dout <= 8'h9A;

8'h0A: dout <= 8'hAA;

8'h0B: dout <= 8'hBA;

8'h0C: dout <= 8'hCA;

8'h0D: dout <= 8'hDA;

8'h0E: dout <= 8'hEA;

8'h0F: dout <= 8'hFA;

8'h10: dout <= 8'h50;

8'h11: dout <= 8'h51;

8'h12: dout <= 8'h52;

8'h13: dout <= 8'h53;

8'h14: dout <= 8'h54;

8'h15: dout <= 8'h55;

8'h16: dout <= 8'h56;

8'h17: dout <= 8'h57;

8'h18: dout <= 8'h58;

8'h19: dout <= 8'h59;

8'h1A: dout <= 8'h5A;

8'h1B: dout <= 8'h5B;

8'h1C: dout <= 8'h5C;

8'h1D: dout <= 8'h5D;

8'h1E: dout <= 8'h5E;

8'h1F: dout <= 8'h5F;

default: dout <= 8'hff;

endcase

end

endmodule

对其进行测试,易如反掌:

测试文件:

`timescale 1ns / 1ps

module mini_rom_tb;

reg clk;

reg [7:0] addr;

wire [7:0] dout;

integer i;

initial begin

clk = 0;

forever

#2 clk = ~clk;

end

initial begin

addr = 0;

//#10 $monitor ("addr = %h, data = %h, read_en = %b, ce = %b", addr, data, read_en, ce);

for (i = 0; i < 256; i = i + 1 ) begin

@(negedge clk)

addr = i;

end

end

mini_rom U_rom_case(

.clk(clk),

.addr(addr) , // addr input

.dout(dout) // Data output

);

endmodule

互联网上有很多宝贵的资源,让人感动,我等也奉行开源的精神,让自己得益的同时,也发光发热。