一、先决知识

(1)理解并知道移位寄存器如何工作

二、SPI概述

SPI(serial Peripheral Interface 串行片上(外围)设备接口)是由摩托罗拉公司研发的。SPI器件可以工作在全双工或半双工的模式下,在短距离内实现数据的高速传输(并没有规定速度限制,由硬件和软件决定)。

三、SPI的关键特性

(1)读/写全双工

(2)采用主从结构(一般只有一个主设备)

(3)SPI总线

时序极性(CPOL),时序相位(CPHA),频率可配置

(4)传输位数可配置(即一个通讯周期的传输bit可配置)

1、SPI的优点

(1)相比于IIC,UART等,传输协议比较简单

(2)是最快的串行通信接口之一

(3)支持全双工传输

2、SPI缺点

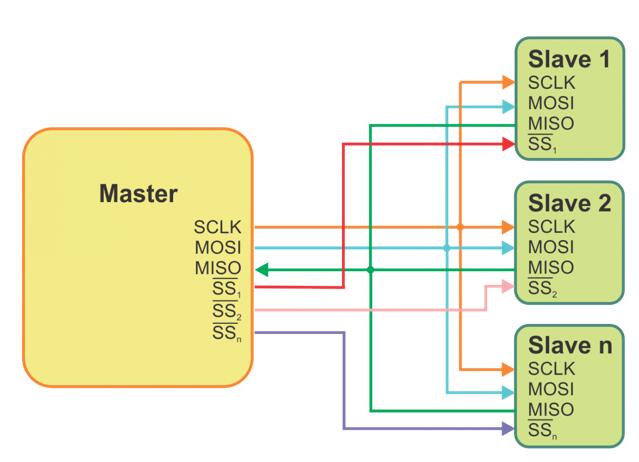

(1)占用多根线路引脚(x+3,x表示设备数量)

(2)没有硬件的流控制

(3)从机没有确认信号

(4)易被尖峰脉冲干扰

四、物理结构

(1)连接模型

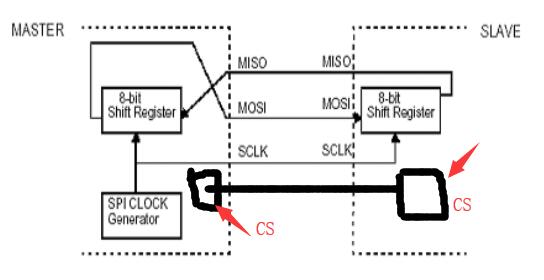

(2)内部结构模型

接口定义:

MISO: Master input slave output(主入从出) /或称为SDI() 主设备输入接从设备输出

MOSI: Master output slave input(主出从入) /或称为 SDO 主设备的输出接从设备的输入

CS(SS):chip select (slave selec) 选择从器件

SCLK:(slave clock) 从设备时钟信号(由主设备提供和控制)

从内部结构可以知道,两个移位寄存器形成了一个回路,故可以知道,有输出必定会有输入.

(3)传输模型和时序

传输模型

工作模式

SPI的工作模式有4中,工作模式的区别是:什么时候对输入数据采样,什么时候输出数据,相关参数是CPOL,CPHA,其中CPHA起决定性作用

CPOL:clock polarity (时钟闲时属性,即不在采样时刻的电平)

CPHA:clock phase (时钟相位,即什么时候采样,什么时候输出)

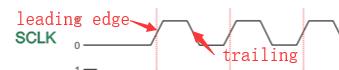

其他相关名词(在工程具体配置中会见到)

leading edge(前跳变沿),trailing edge(后跳变沿)与跳变方向无关

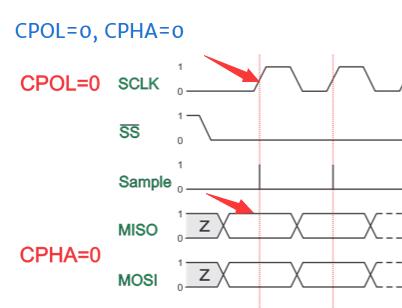

模式0(MODE 0)

(1) CLK闲时是低电平

(2) 数据在上升沿到来时(前)必须是可靠的(可采集的)

(3) 在CLK高电平时,MISO 和MOSI的数据必须保持不变

(4) 数据在下降沿和低电平时可改变

(5) 一个CLK内数据在第一个跳变(0->1)中输入(采集),第二个跳变(1->0)中输出

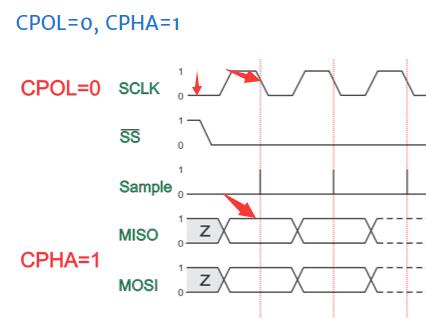

模式1(MODE1)

(1) CLK闲时是低电平

(2) 上升沿可以用来准备数据(即传输)

(3) 在CLK低电平时,MISO 和MOSI的数据必须保持不变

(4)

数据在上升沿和高电平时可改变

(5) 一个CLK内数据在第一个跳变(0->1)中输出,第二个跳变(1->0)中输入

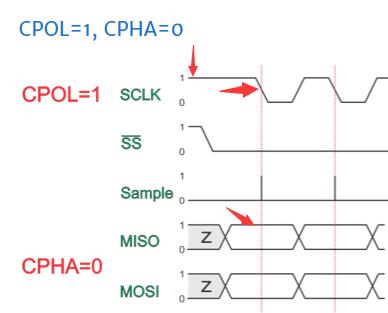

模式2(MODE2)

(1) CLK闲时是高电平

(2) 上升沿可以用来准备数据(即传输),下降沿到来时必须保证数据可靠

(3) 在CLK低电平时,MISO 和MOSI的数据必须保持不变

(4)

数据在上升沿和高电平时可改变

(5) 一个CLK内数据在第一个跳变(1->0)中输入2,第二个跳变(0->1)中输出

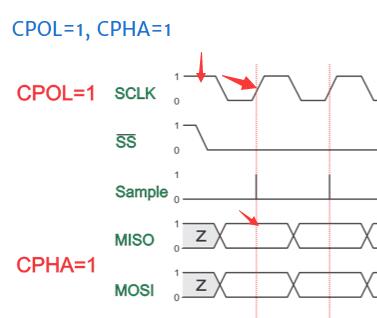

模式3(MODE3)

(1) CLK闲时是高电平

(2) 下降沿可以用来准备数据(即传输)

(3) 在CLK高电平时,MISO 和MOSI的数据必须保持不变

(4)

数据在下降沿和低电平时可改变(即传送给对方,对方在上升沿采集)

(5) 一个CLK内数据在第一个跳变(1->0)中输出,第二个跳变(0->1)中输入

具体数据交换(以模式1为例子)

CLK

主机buff 从机buff

---------------------------------------------------

0 0 10 1 01010 01010101

---------------------------------------------------

1 0--1 0101010x 0 1010101x 1

---------------------------------------------------

0 0 10 1 01010 01010101

---------------------------------------------------

1 0--1 0101010x 0 1010101x 1

1--0 01010100

10101011

---------------------------------------------------

2 0--1 1010100x 1 010101 1 x 0

1--0 10101001 01010110

---------------------------------------------------

3 0--1 0101001x 0 1010110x 1

1--0 01010010 10101101

---------------------------------------------------

4 0--1 1010010x 1 0101101x 0

1--0 10100101 01011010

---------------------------------------------------

....

---------------------------------------------------

2 0--1 1010100x 1 010101 1 x 0

1--0 10101001 01010110

---------------------------------------------------

3 0--1 0101001x 0 1010110x 1

1--0 01010010 10101101

---------------------------------------------------

4 0--1 1010010x 1 0101101x 0

1--0 10100101 01011010

---------------------------------------------------

....

0--1 表示上升沿 1--0 表示下降沿

补充:

LSB:Least significat Bit (最小权重位,即低位)

MSB: most significat Bit (最大权重位,即高位)