Xilinx Artix-7 FPGA 【1】之实现DEMO工程并烧写

一、主要目的

- 使用vivado 15.4 创建A7 FPGA工程

- Verilog、约束等资源文件的编写及添加

- 程序的仿真

- 程序烧入固化

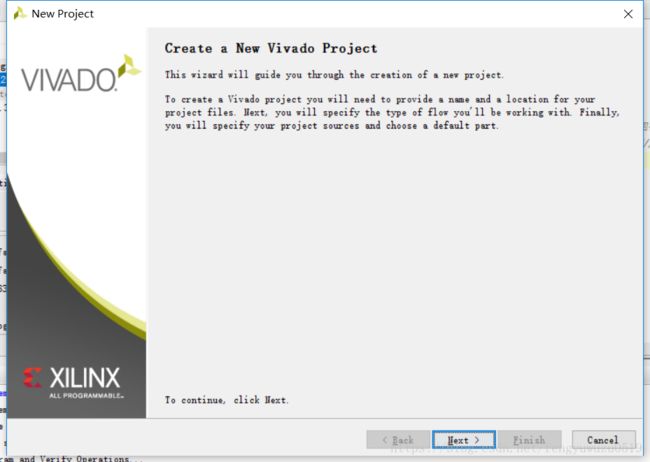

二、创建 A7 FPGA Vivado 工程

(1)选择新建工程:

(2)项目名称及保存路径

(3)选择工程类型

在下面的对话框中默认选择RTL Project, 因为我们这里使用verilog行为描述语言来编程。下面的 Do not specify source at this time 的勾也可以打上。如果不打上,下一步会进入添加 source file 界面

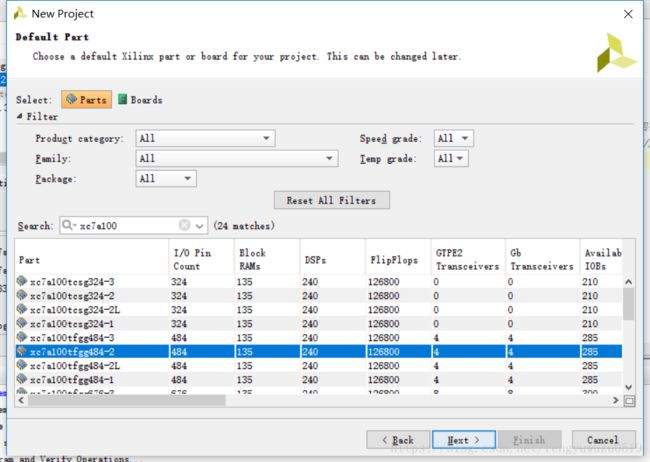

(4)选择FPGA型号

在接下来的对话框选择所用的 FPGA 器件,以及进行一些配置。FPGA 芯片型号一定要跟开发板上的型号一致,首先在 Family 栏里选择 Artix-7, Speed grade 栏选择-2, 在 Package栏选择 fgg484, 然后在下面的列表中选择 xc7a100tfgg484-2,单击 NEXT 进入下一界面:

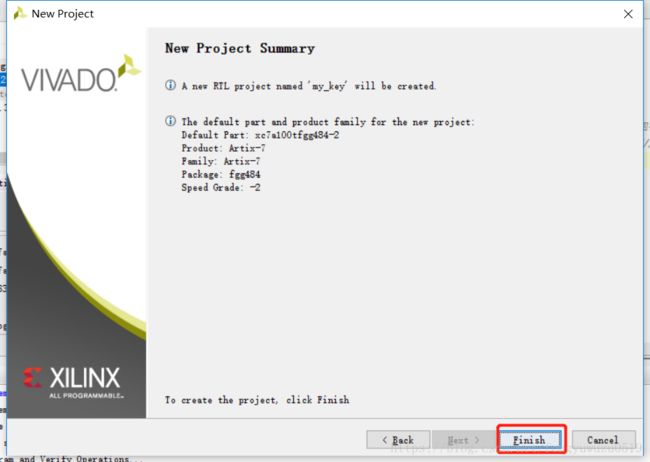

(5)再次确认一下板子型号有没有选对, 没有问题再点击“Finish”完成工程创建。

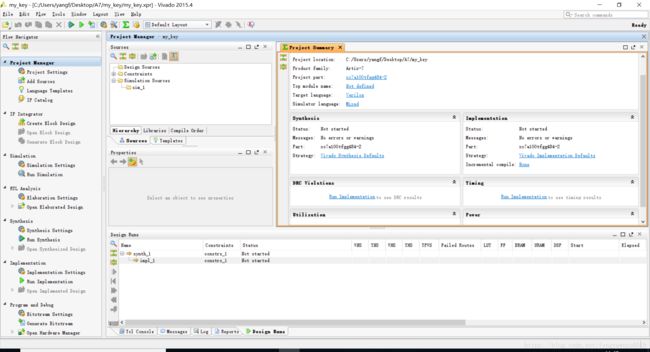

工程创建后如下图所示:

三、添加资源文件

1、添加并编写按键的 verilog 代码

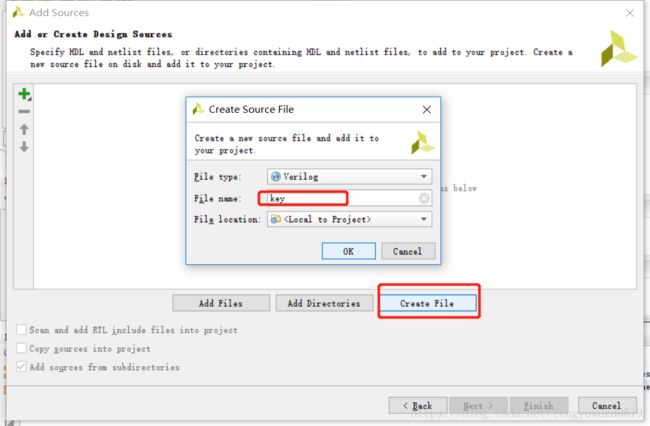

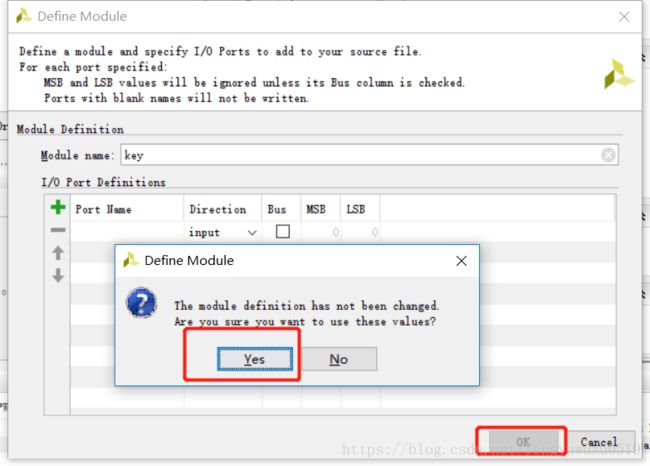

(1)添加verilog设计文件

向导会提示您定义 I/O 的端口,这里我们可以不定义,后面自己在程序中编写就可以,单击 OK完成。

这时在 Project Manager 界面下的 Design Sources 里已经有了一个 led_test.v 文件, 并且自动成为项目的顶层(Top)模块了。

(2)编写verilog代码

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 14:43:40 10/31/2015

// Design Name: key_test

// Module Name: key_test

// Project Name: key_test

// Target Devices: xc7a100tfgg484-2

// Tool versions: vivado 2015.2

// Description: 按键测试程序

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

// 程序思路:循环监测 20ms延时再检测 如果按键有效则点按键上方的灯1S 而后熄灭 返回循环监测

//////////////////////////////////////////////////////////////////////////////////

module KEY(

input clk,reset,

input [1:0]sw,

output [1:0]led

);

//状态机状态声明

localparam [1:0]

FIRST_TEST = 2'b00,

SECOND_TEST = 2'b01,

LED_ON = 2'b10;

//信号声明

reg [18:0]count1;//延时程序 1clk 约为42ns

reg [24:0]count2;

reg [1:0]led_reg,led_next;

reg [1:0]state_reg,state_next;

//FSMD状态和数据寄存器

always @(posedge clk or negedge reset)

if(!reset)

begin

state_reg <= FIRST_TEST;

led_reg <= 2'b00;

count1 <= 19'd0;

count2 <= 25'd0;

end

else

begin

state_reg <= state_next;

led_reg <= led_next;

//第二次按键检查

if(state_next==SECOND_TEST)

begin

count1 <= count1 + 1'b1;

end

else

begin

count1 <= 19'd0;

end

//点灯延时1S

if(state_next==LED_ON)

begin

count2 <= count2 + 1'b1;

end

else

begin

count2 <= 25'd0;

end

end

//按键点灯延时1S组合逻辑

always@( * )

begin

state_next = state_reg;

led_next = led_reg;

case(state_reg)

FIRST_TEST://第一次按键检测

begin

if(sw != 2'b11)

begin

state_next = SECOND_TEST;

end

end

SECOND_TEST://延时20ms左右 作第二次按键检测

begin

if(count1>19'd476190)

begin

if(sw == 2'b11)

begin

state_next = FIRST_TEST;

end

else

begin

state_next = LED_ON;

led_next = ~sw;

end

end

end

LED_ON://点灯延时1s左右 然后熄灭

begin

if(count2>25'd23809524)

begin

state_next = FIRST_TEST;

led_next = 2'b00;

end

end

endcase

end

//led输出

assign led = (reset==1'b0)?2'b11:led_reg;

//另一种简单程序 直接连接到按键

//assign led = ~sw

endmodule

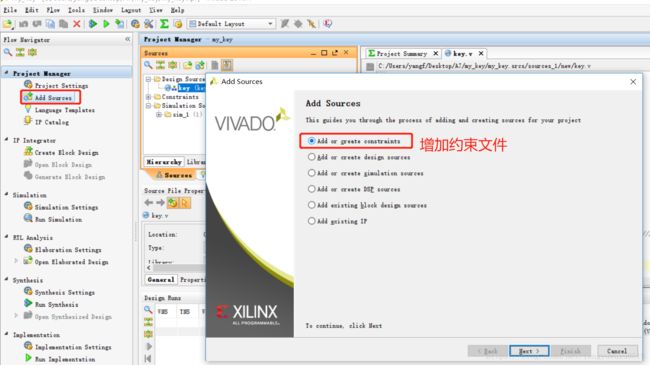

2、添加 XDC 管脚约束文件

和 ISE 软件不同, Vivado 使用的约束文件格式为 xdc 文件。xdc 文件里主要是完成管脚的约束,时钟的约束, 以及组的约束。这里我们需要对 led_test.v 程序中的输入输出端口分配到 FPGA的真实管脚上, 这需要准备一个 FPGA 的引脚绑定文件.xdc 并添加到工程中。

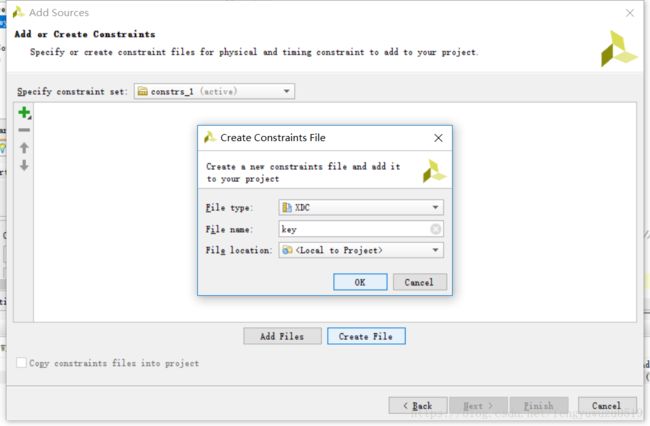

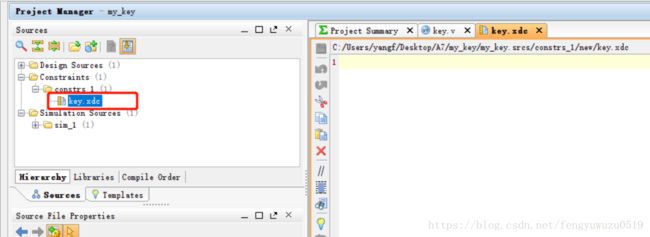

(1)添加xdc约束文件

这时在 Project Manager 界面下的 Constraints 目录的 constrs_1 目录下已经有了一个key.xdc 文件。

(2)编写约束文件

双击打开这个xdc 文件,在这个文件里添加以下的引脚定义。

set_property IOSTANDARD LVCMOS15 [get_ports {sw[1]}]

set_property IOSTANDARD LVCMOS15 [get_ports {sw[0]}]

set_property PACKAGE_PIN Y7 [get_ports {sw[1]}]

set_property PACKAGE_PIN Y8 [get_ports {sw[0]}]

set_property PACKAGE_PIN W9 [get_ports {led[0]}]

set_property PACKAGE_PIN Y9 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS15 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS15 [get_ports {led[0]}]

set_property PACKAGE_PIN R17 [get_ports reset]

set_property PACKAGE_PIN Y18 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports reset]下面来介绍一下最基本的 XDC 编写的语法,普通 IO 口只需约束引脚号和电压,

管脚约束如下:

set_property PACKAGE_PIN "引脚编号" [get_ports “端口名称”]

电平信号的约束如下:

set_property IOSTANDARD "电压" [get_ports “端口名称”]

这里需要注意文字的大小写,端口名称是数组的话用{ }刮起来,端口名称必须和源代码中的名字一致,且端口名字不能和关键字一样。

时钟端口还可以定义时钟周期约束,差分时钟只要定义和约束 P 脚的。比如我们在 XDC里面定义了输入的差分时钟的时钟周期为 5ns。 时钟周期的约束方法如下:

create_clock -period "周期" [get_ports “端口名称”]

这里核心板上的 LED 灯,也就是程序中 led[2],是连接到 1.5V 电压的 Bank,所以电压这里是 LVCMOS15。

完成后选择菜单 File->Save all files 保存所有文件。

四、编译

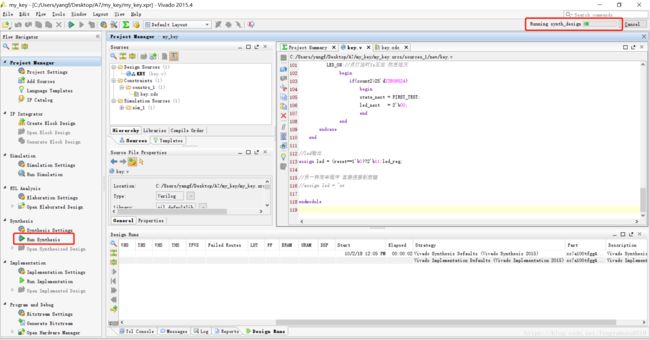

(1)综合

点击 Run Synthesis,即可开始综合并生成网表文件:

(2)布局布线

综合完成后,会弹出这样一个提示小窗口。可以点这里的 Run Implementation 来开始布局布线:

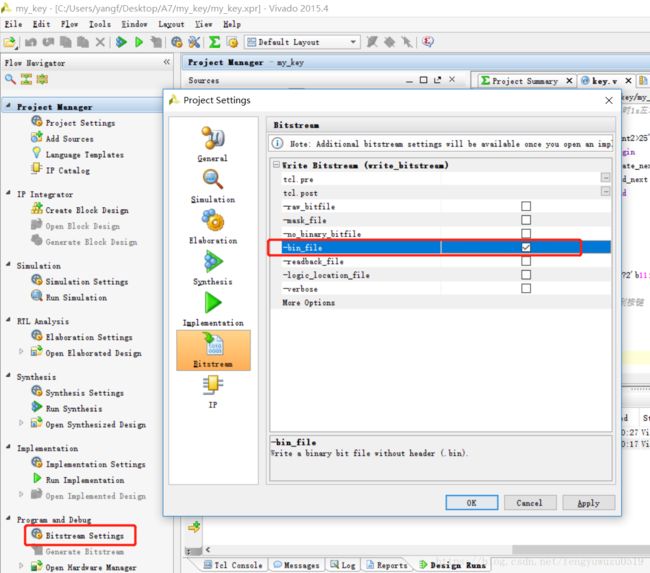

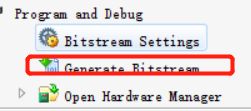

(3)生成bit文件

设置生成bin文件

生成key.bin和key.bit文件用于下载。

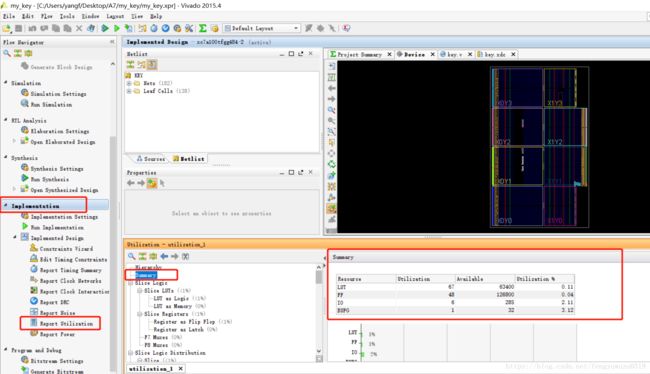

(4)查看资源使用情况

Bit 文件生成完成后,我们可以打开 Project Summary 页面的 Table 来查看板子上实际资源的使用情况,因为我们这里的 test 程序比较简单,只用到了四个资源: LUT(查找表),FF(Flip Flop 寄存器), IO(管脚)和 BUFG(时钟 Buffer)。

五、代码的烧写及固化

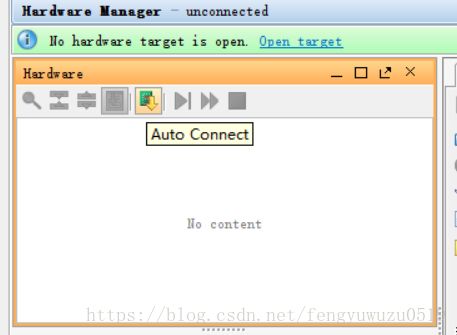

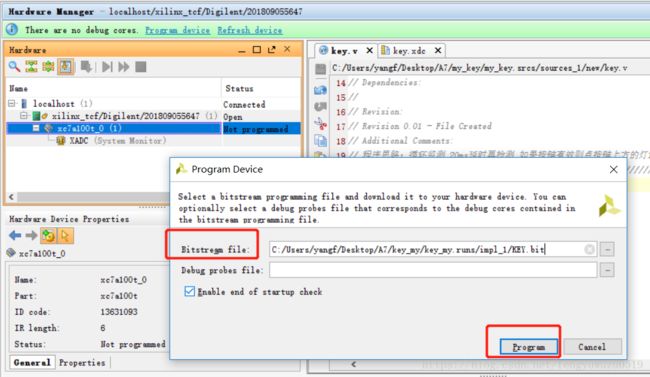

1、烧写bit文件

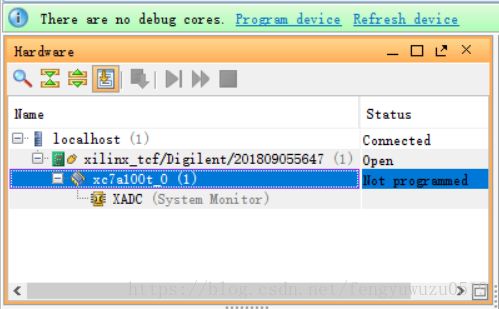

打开硬件管理界面

接上下载器

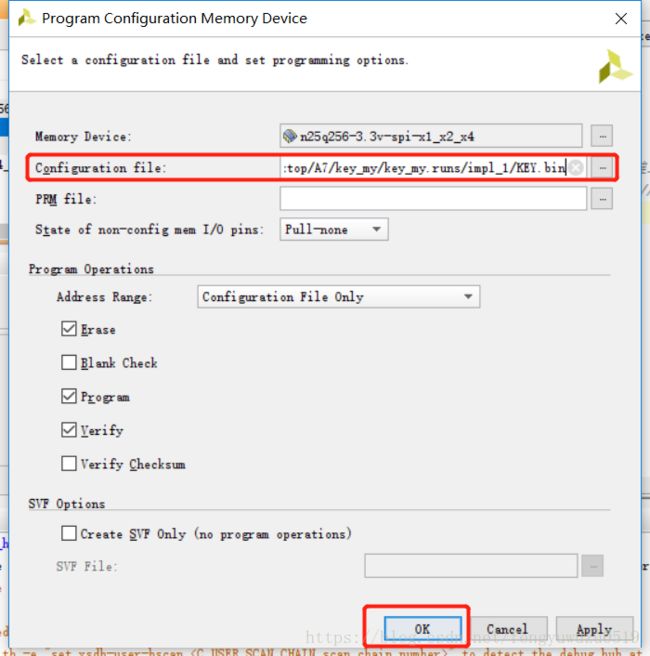

2、烧写bin文件,固化到NOR

选择flash型号

烧写:

断电选择上电启动方式,重新上电观察现象。