ic 电源管理单元

芯片里面的电源管理电源主要功能描述如下:

* 复位

* 锁相环和分频器

* HWCFG[2:0] 引脚信号识别和解码

* 睡眠模式

* 模块电源管理

* 顶层控制寄存器

一、复位

复位的信号源有以下几种:

1、PIN_RESETN(低有效):PIN_RESETN 将会把整个芯片都恢复到默认状态

2、PIN_A11STRST(低有效):PIN_A11STRST 通常连接到 ARM 调试工具,它能恢复芯片的大部分模块(除了以下模块):

a、ARM 协处理器 CP14 调试逻辑

b、锁相环

3、看门狗复位:除了软件配置寄存器 SWRSTR 其他的都将会被复位

4、SWRSTR 寄存器复位:除了自己本身不被复位,其他的都将被复位

二、锁相环

芯片里面共有 5 路锁相环:PLL1、PLL2、PLL3、PLLM 和 PLLA

* PLL1 和 PLL2 是通用的锁相环

* PLL3 是高速锁相环专用于基带

* PLLM 是通用锁相环专用于 MDDR

* PLLA 是高速锁相环专用于 ARM CPU

1、通用锁相环

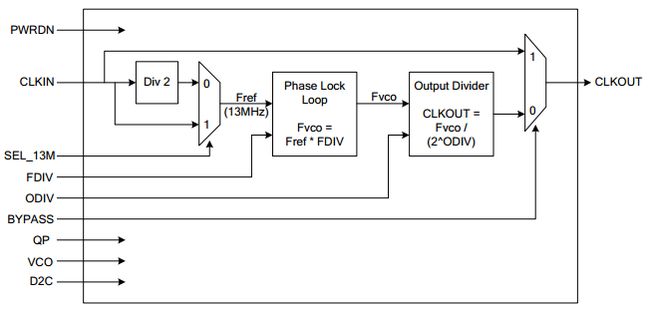

下面是通用锁相环(PLL1、PLL2、PLLM)的结构图

CLKIN 是输入时钟(通常为 26M)。CLKIN 通过输入分频器提供 13M 的参考时钟给锁相环,如果输入时钟为 13M,则需要将 SEL_13M 置 1 绕开输入分频器。锁相环的反馈分频器由 FDIV 控制,输出分频器将会对 Fvco 进行 1、2、4、8 分频,由 ODIV[1:0] 控制。当 SEL_13M = 0 时,输出时钟频率计算公式如下:

![]()

当 BYPASS = 1,输出时钟等于输入时钟。当 PWRDN = =1,锁相环关闭。PLL1、PLL2 和 PLLM 的 Fvco 频率范围为 [650M,1300M],即 FDIV 的范围为 (50,100]。QP、VCO 和 D2C 控制锁相环内部的电流。

2、高速锁相环

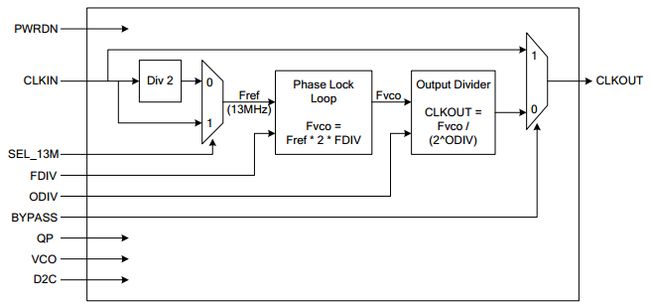

下面是高速锁相环(PLL3、PLLA)的结构图

高速锁相环的控制信号和通用锁相环基本一致,输出时钟频率计算公式如下:

![]()

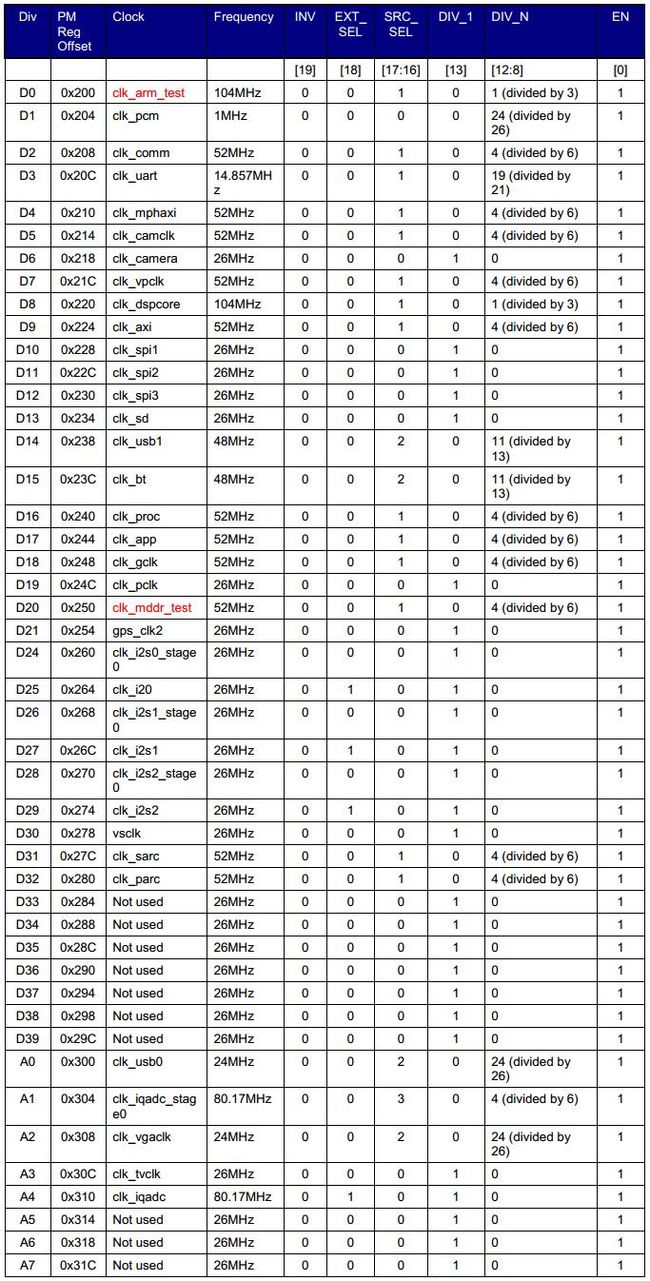

3、分频器

数组电路有 40 组分频器(D0 - D39),模拟电路有 8 组分频器(A0 - A7)。每个分频器都能通过编程设置输入时钟(PLL1、PLL2、PLL3、晶振、外部时钟),输出时钟为输入时钟除以 n,n 为寄存器取值 [1, 32]。芯片默认的状态将会打开所有的分频器,软件必须在合适的情况下关掉不必要的分频器以降低功耗,还有一些分频器通过级联的方式提供更低的输出频率。分频器通过相应的寄存器来设置,硬件电路通过一个状态机自动保证时钟变化时的瞬时时钟不会影响到下游的逻辑。在硬件状态机完成之前 AHB 总线上的其他寄存器都不能访问,这段时间大约为 160 晶振时钟周期。下面是各时钟在 000 - 011 四种启动模式下的默认设置:

其中SRC_SEL: 0 为 晶振时钟,1 为 PLL1, 2 为 PLL2,3 为 PLL3。另外外设的时钟源由 D17 控制即 clk_app 提供。

三、HWCFG 模式选择

芯片的操作模式通过 PIN_NDDAT[2:0] 来选择,可以通过上下拉来控制其状态,所有的模式列表如下:

000 Boot from NAND

001 UART download

010 Boot from SD

011 Boot from MSD

100 Reserved

101 PLL bypass(boot from NAND)

110 External boot

111 External boot(debug bus enabled)

四、睡眠模式

处理器通过进入睡眠模式以降低功耗,在睡眠模式,ARM 的核心时钟以及 AXI 总线都将会被关闭,直到中断将处理器唤醒。当处理器睡眠时,可以通过寄存器设置 app bus 是否关闭。同样 L2 cache 在处理器睡眠的时候也将被关闭,所以在睡眠之前软件需要对 L2 cache 做同步操作。下面是处理器进入和退出睡眠的操作顺序:

a、设置中断事件以唤醒处理器(通常为 timer 或者 GPIO)

b、设置 ARM 配置寄存器 ARMCFGR 的 bit0 为 1 启动睡眠流程

c、执行 WFI 指令,这个指令将会让 ARM 执行必要的操作以安全的进入待机模式,一旦 ARM 进入待机模式,STANDBYWFI 标记将会被置位 ARMCFGR bit1

d、关闭 ARM 时钟,硬件标记 ARM_SLEEP 将会被设置 ARMCFGR bit2

e、当唤醒中断来临,ARM_SLEEP 标记将会被清除,ARM 时钟将会打开,然后 ARM 退出待机模式进入运行模式

基带睡眠的时候,STACH processor 和 PHY processor 将会独立的进入睡眠,可以从 PMSTATR 寄存器获取相应的状态标记。为了最大限度的节省电能,芯片可以进入深度睡眠模式,在深度睡眠模式所有的锁相环电路和时钟都将被关闭,只有 32.768 KHz 时钟存在。在深度睡眠时,处理器可以通过一个 GPIO 控制外部 PMU 进入低功耗模式。

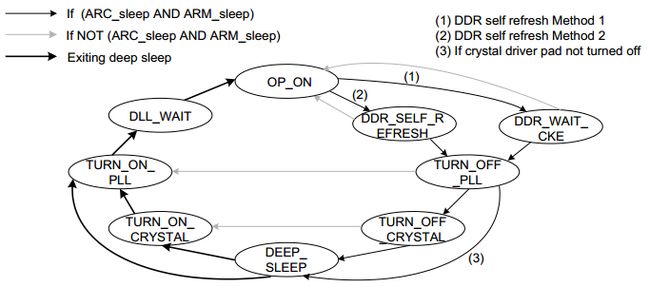

在深度睡眠模式可以通过如下方法控制DDR self-refresh,软件首先编程控制 DDR 控制器进入自动低功耗模式,在该模式下 DDR 控制器在指定时钟周期内没有收到活跃的操作就将开启 DDR self-fresh 并将 CKE_STATUS 标记置位,处理器在进入深度睡眠之前会一直等到这个标记的置位,当退出深度睡眠时,首先会打开 DDR 的时钟并等到 DLL 稳定,然后再打开其他模块的时钟,DDR 控制将会在第一次存取 DDR 数据时退出 self-fresh。在深度睡眠模式下仍然可以指定一些时钟保持开启状态,比如:USB。下面是深度睡眠的状态机:

五、模块电源管理

芯片里面的一些功能模块有内置的电源开关,可以独立的打开或者关闭,这些模块包括:ARM_CPU、DSP、MM_GE,他们可以通过寄存器 ARMPWDR、DSPPWDR、MMGEPWDR 控制。

ARM 的关闭流程如下:首先设置 ARMPWDR.SLEEP_PWD 为 1,然后开始 ARM 的正常睡眠流程,当 ARM_SLEEP 被设置,电源管理单元将会自动关闭 ARM 直到唤醒中断来临。当 ARM 再次上电的时候,ARM 将会被复位并从地址 0x0 开始执行。

六、顶层控制寄存器

* 时钟控制寄存器

* USB PHY 控制器

* 基带顶层控制寄存器

* 模拟前端顶层控制寄存器