利用FPGA实现PCI总线接口及Windows驱动实现

利用FPGA实现PCI总线接口及Windows驱动实现

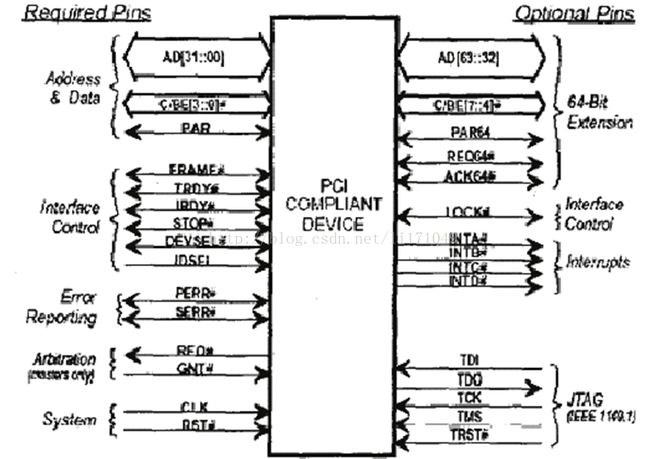

关于PCI总线协议,资料网上、书本都是。这里我们仅仅对重点对利用FPGA实现PCI总线接口问题进行简单分析。下图是PCI总线接口信号:

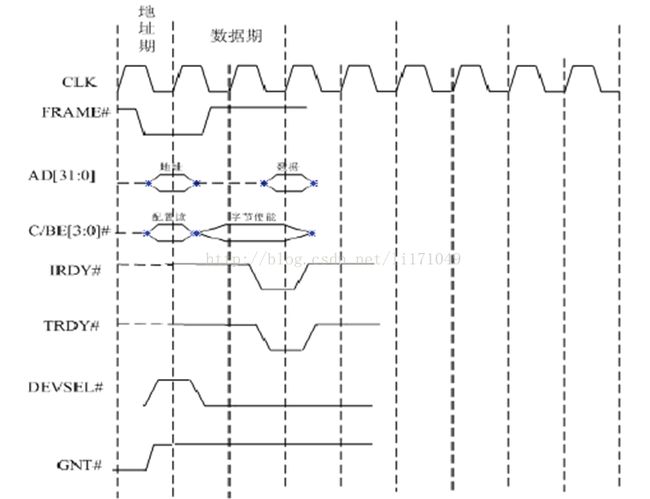

配置空间寄存器操作时序如下图:

配置寄存器空间写时序如下图:

依照状态机的编程思路。

部分Verilog代码如下:

ST_CFGREAD: begin

enable <= EN_RD;

if (~irdy || trdy) begin

case (address)

0: data <= { DEVICE_ID,VENDOR_ID };

1: data <= { 5'b0,DEVSEL_TIMING, 9'b0, 14'b0, memen,1'b0};

2: data <= {DEVICE_CLASS, DEVICE_REV };

4: data <= { 12'b0,baseaddr, 8'b0, 4'b0010 }; // baseaddr + request mem < 1Mbyte

11: data <={SUBSYSTEM_ID, SUBSYSTEM_VENDOR_ID };

16: data <= { 24'b0,baseaddr };

default: data <='h00000000;

endcase

address <= address + 1'b1;

end

if (frame && ~irdy && ~trdy) begin

devsel <= 1;

state <= ST_IDLE;

enable <= EN_TR;

end

end

ST_CFGWRITE: begin

enable <= EN_WR;

if (~irdy) begin

case (address)

4: baseaddr <=ad[19:12]; // XXX examine cbe

1: memen <= ad[1];

default: ;

endcase

address <= address + 1'b1;

if (frame) begin

devsel <= 1;

state <= ST_IDLE;

enable <= EN_TR;

end

end

end

完整代码地址(QuartusII 9.0 (32-Bit)):http://download.csdn.net/detail/li171049/6784589

针对以上部分的windows驱动开发,就像我一篇文章(http://blog.csdn.net/li171049/article/details/17612283)中提到的windows对I/O读写的原理是一样的。这部分驱动vc6.0+DDK2600我也实现了。----

--参见:http://download.csdn.net/detail/li171049/6784595

对于PCI总线读写时序,我还在研究中,这里就不瞎说了。