s5pv210——nandflash和inand的基础理论

以下内容源于朱友鹏《物联网大讲坛》课程的学习。如有侵权,请告知删除。

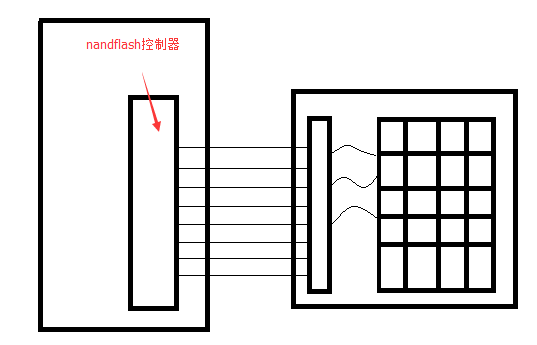

首先是一些基础知识,见下图

一、NandFlash的接口

1、Nand的型号与命名

以K9F2G08为例

- K9F表示是三星公司的NandFlash系列。

- 2G表示Nand的大小是2Gbit(256MB)。

- 08表示Nand是8位的(8位就是数据线有8根)。

- 看出厂家、系列型号、容量大小、数据位数。

2、Nand的数据位

- Nand有8位数据位的,有16位数据位的;

- Nand是并行接口;

- Nand的数据线上传递的不一定全部是有效数据,也可能有命令、地址等。

3、Nand的功能框图

(1)Nand的结构

- 可以看作一个矩阵式存储器。被分成一个个小块,每一小块可以存储一个bit位。

(2)Nand中可以被单次访问的最小单元叫做Page(页)

- 即Nand进行一次读写至少要读写这么多内容,或者是这么多内容的整数倍;

- K9F2G08芯片中,Page的大小是2KB+64B。这说明要读写K9F2G08,每次至少要读写2KB或者n*2KB,即使只需要其中的一个字节。其中2KB是真正用来存储的,而64B是用来存储ECC数据、块坏标志。

- 这是典型的块设备。(现在有些块设备为了方便,提供了一种random read模式,可以只读取1个字节)。

- 块设备(例如硬盘)的扇区,类似于nand的页。而block的概念是共有的,那么块设备中的一个block有多少个扇区?

(3)页往上还有个Block(块)的概念

- 1个块等于若干个页(譬如在K9F2G08中1个块等于64页)。

(4)块往上是整个Nand芯片,叫做Device。

- 一个Device是若干个Block,譬如K9F2F08一个Device有2028个block。所以整个Device大小为:2048×64×2K = 256MB

(5)块设备分page、block的意义

- 块设备不能完全按字节访问而必须块访问,这是物理上的限制,而非人为设置的障碍。

- Page和Block各有各的意义,譬如Nand中,Page是读写Nand的最小单位;Block是擦除Nand的最小单位。

- 这些规则都是Nand的物理原理和限制要求的。

(6)Nand芯片中主要包含2部分:Nand存储颗粒+Nand接口电路。

- 存储颗粒就是纯粹的Nand原理的存储单元,类似于仓库;

- Nand接口电路是用来管理存储颗粒,并且给外界提供一个统一的Nand接口规格的访问接口的。

(7)Nand中有多个存储单元,每个单元都有自己的地址(地址是精确到字节的)。

- 所以Nand是地址编排精确到字节,但是实际读写却只能精确到页(所以Nand的很多操作都要求给的地址是页对齐的,譬如2K、4K、512K等这样的地址,不能给3000B这样的地址)。

- Nand读写时地址传递是通过IO线发送的,因为地址有32位而IO只有8位,所以需要多个cycle才能发送完毕。

- 一般的Nand都是4cycle或者5cycle发送地址(从这里把Nand分为了4cycle Nand和5cycle Nand)。

(8)总结

- Nand芯片内部有存储空间,并且有电路来管理这些存储空间,向外部提供统一的Nand接口的访问规则。

- 外部的SoC可以使用Nand接口时序来读写这个Nand存储芯片。

- Nand接口是一种公用接口,是一种标准,理论上来说外部SoC可以直接模拟Nand接口来读写Nand芯片,但是实际上因为nand接口对时序要求非常严格,而且时序很复杂,所以一般的SoC都是通过专用的硬件的Nand控制器(这些控制器一般是作为SoC的内部外设来存在的)来操控Nand芯片的。

二、NandFlash的结构

1、Nand的单元组织:block与page

(1)Nand的页和块设备(尤其是硬盘)的扇区是类似的。

- 扇区最早在磁盘中是512字节,后来也有些高级硬盘扇区不是512字节而是1024字节/2048字节/4096字节等。

- Nand也是一样,不同的Nand的页的大小是不同的,也有512字节/1024字节/2048字节/4096字节等。

(2)一个block等于多少page也是不定的,不同的Nand也不同。一个Nand芯片有多少block也是不定的,不同的Nand芯片也不同。

(3)Nand的组织架构挺乱的,接口时序也不同,造成结构就是不同厂家的Nand芯片,或者是同一个厂家的不同系列型号存储容量的nand接口也不一样。

- nand有一个很大的问题就是一旦升级容量或者换芯片系列则硬件要重新做、软件要重新移植。

2、带内数据和带外数据

(1)Nand的每个页由2部分组成,这2部分各自都有一定的存储空间。

- 譬如K9F2G08中为2K+64字节。

- 2K字节属于带内数据,是我们真正的存储空间,将来存储在Nand中的有效数据就是存在这2K范围内的(平时计算nand的容量时只考虑这2KB);

- 64字节的带外数据不能用来存储有效数据,是作为别的附加用途的(譬如用来存储ECC数据、用来存储坏块标志等……)。

(2)ECC(error correction code,错误校验码)

- Nand的稳定性不够好,因而nand存储的出错(即位反转)概率高;

- 将有效信息存储到Nand中的同时,按照一定的算法(譬如CRC16等校验算法)计算ECC信息,将ECC信息同时存储到Nand这个页的带外数据区。

- 读取数据时,对数据用同样的算法再计算一次ECC,并且和从带外数据区读出的ECC进行校验;

- 如果校验通过则证明Nand的有效数据可信,如果校验不通过则证明这个数据已经被损坏(只能丢弃或者尝试修复)。

(3)坏块标志

- Nand芯片在用一段时间后,某些块可能会坏掉(这些块无法擦除了,或者无法读写了),类似于硬盘的坏道。

- 坏块是不可避免的,而且随着Nand的使用坏块会越来越多。当坏块还不算太多时这个Nand都是可以用的,除非坏块太多了不划算使用了才会换新的。

- 为了管理Nand,发明了一种坏块标志机制。Nand的每个页的64字节的带外数据中,文件系统定义了一个固定位置(譬如定位第24字节)来标记这个块是好的还是坏的。当某个块已经坏了,文件系统将该块标记为坏块,以后访问nand时直接跳过这个块。

3、Nand的地址时序

(1)nand的地址有多位,分4/5周期通过IO引脚发送给Nand芯片(一般它的外接引脚只有8bit或者16bit)来对Nand进行寻址。

- 寻址的最小单位是字节,但是读写的最小单位是页。

(2)nand的地址在写代码时要按照Nand要求的时序和顺序去依次写入。

4、Nand的命令码

(1)外部SoC要想通过Nand控制器来访问Nand(实质就是通过Nand接口),就必须按照Nand接口给nand发送命令、地址、数据等信息来读写Nand。

(2)Nand芯片内部的管理电路本身可以接收外部发送的命令,然后根据这些命令来读写Nand内容与外部SoC交互。

- 对nand进行的所有操作(擦除、读、写……)都要有命令、地址、数据的参与才能完成,而且必须按照Nand芯片规定的流程来做。

三、NandFlash的常见操作及流程分析

1、坏块检查

- Flash使用之前要先统一擦除(擦除的单位是块)。Flash类设备擦除后里面全是1,所以擦干净之后读出来的值是0xff。

- 检查坏块的思路就是:先块擦除,然后将整块读出来,依次检测各自节是否为0xff,如果是则表明不是坏块,如果不是则表明是坏块。

2、页写(program)操作

(1)写之前确保这个页被擦除干净

- 写操作(write)在flash的操作中就叫编程(program)

(2)SoC写Flash时通过命令线、IO线依次发送写命令、写页地址、写数据等进入NandFlash。

(3)写的过程

- SoC通过Nand控制器和Nand芯片完成顺序对接,然后按照时序要求将一页数据发给Nand芯片内部的接口电路。

- 接口电路先接收收据到自己的缓冲区,然后再集中写入Nand芯片的存储区域中。

- Nand接口电路将一页数据从缓冲区中写入Nand存储系统中需要一定的时间,这段时间Nand芯片不能再响应SOC发过来的其他命令,所以SoC要等待Nnad接口电路忙完。

- 等待方法是SoC不断读取状态寄存器(这个状态寄存器有2种情况:一种是SoC的Nand控制器自带的,另一种是SoC通过发命令得到命令响应得到的);

- SoC通过检查状态寄存器的状态位,得知页数据是否已经写完。

(4)Nand的读写可能出错,为了安全进行ECC校验

- ECC校验有硬件式校验和软件式校验;

- 软件式校验,策略之一是将刚才写入的1页数据读出来,和写入的内容进行逐一对比。如果读出的和写入的完全一样,说明刚才的写入过程正确完成了;如果读出来的和写入的不完全一样那就说明刚才的写入有问题。

- SoC的Nand控制器可以提供硬件式ECC(这个也是比较普遍的情况),硬件式ECC就是在Nand的控制器中有个硬件模块专门做ECC操作。

- 在写入Nand芯片时,打开ECC生成开关。则在写入Nand芯片的过程中,Nand控制器的ECC模块会自动生成ECC数据,并放在相应的寄存器中,然后将ECC数据写入Nand芯片的带外数据区;

- 在读取Nand芯片时,打开硬件ECC开关。则在读取Nand芯片的过程中,硬件ECC会自动计算读进来的一页数据的ECC值,并放到相应的寄存器中。然后读取带外数据区中原来写入时存入的ECC值,和之前得到的ECC值进行校验。

- 校验通过则说明读写正确,校验不通过则说明不正确。

3、擦除(erase)操作

(1)擦除时必须给块对齐的地址。如果给了不对齐的地址,结果是不可知的(有些Nand芯片没关系,它内部会自动将其对齐,而有些Nand会返回地址错误)。

(2)读写时给的地址也是一样,要求是页对齐地址。如果给了不对齐的,也是有可能对有可能错。

4、页读(read)操作

四、S5PV210的NandFlash控制器

1、SoC的Nand控制器的作用

(1)Nand芯片本身通过Nand接口电路来存取数据,Nand接口电路和SOC之间通过Nand接口时序来通信。

- Nand接口时序相对复杂,完全用软件来实现Nand接口时序的缺点:难保证时序能满足、容易不稳定,代码很难写。

- 解决方案:在SoC内部集成一个Nand控制器(实质是一块硬件电路,其完全满足Nand接口时序的操作,然后将接口时序的操作寄存器化)。

(2)SOC和Nand芯片之间通信

- 在SoC没有Nand控制器时,需要SoC来处理接口时序,编程很麻烦,需要程序员看Nand芯片的接口时序图,严格按照接口时序图中编程;

- 在SoC有Nand控制器时,SoC只需要编程操控Nand控制器的寄存器即可,Nand控制器内部硬件会根据寄存器值来生成合适的Nand接口时序和Nand芯片通信。因此读写Nand芯片时不用再关注Nand接口时序,只要关注SoC的Nand控制器的寄存器,编程变得简单。

(3)现在的技术趋势(硬件加速)

- 目前几乎所有的外设在SoC内部都有对应的控制器来与其通信;

- SoC内部集成的各种控制器(也就是各种内部外设)越多,则SoC硬件能完成的功能越多,使用此SoC来完成相应任务时,软件编程越简单。

- 譬如图形处理和图像处理领域中的2D图像编码(jpeg编码)、视频编码(h.264编码)。现在大部分的application级别的SoC都有集成的内部编码器(像S5PV210就有,更复杂的譬如4418、6818也有)。利用这些硬件编码器来进行快速编解码,软件工作量和大大难度降低。

2、结构框图分析

结构框图中关键点:

(1)SFR

- 后续编程的关键,编程时就是通过读写SFR来产生Nand接口时序以读写Nand芯片的;

(2)Nand interface

- 硬件接口,将来和Nand芯片的相应引脚进行连接

(3)ECC生成器

五、S5PV210的Nand控制器的主要寄存器

NFCONF、NFCONT、NFCMMD、NFADDR、NFDATA、NFMECCD0&NFMECCD1、NFSECCD、NFSTAT六、iNand介绍

1、iNand/eMMC/SDCard/MMCCard的关联

(1)最早出现的是MMC卡,卡片式结构,按照MMC协议设计。

- 相较于NandFlash芯片来说,MMC卡有2个优势:第一是卡片化,便于拆装;第二是统一了协议接口,兼容性好。

(2)后来出现SD卡,兼容MMC协议。

- SD卡较MMC有一些改进,譬如写保护、速率、容量等。

- SD卡遵守SD协议,有多个版本。多个版本之间向前兼容。

(3)iNand/eMMC在SD卡的基础上发展起来。

- 较SD卡的区别就是将SD卡芯片化了(解决卡的接触不良问题,便于设备迷你化)。

(4)iNand和eMMC的关联

- eMMC是协议;

- iNand是Sandisk公司符合eMMC协议的一种芯片系列名称。

2、iNand/eMMC的结构框图及其与NandFlash的区别

(1)iNand内部也是由存储系统和接口电路构成(和Nand结构特性类似,不同之处在于接口电路功能不同)。

(2)iNand的接口电路挺复杂,功能很健全。譬如:

- 提供eMMC接口协议,和SoC的eMMC接口控制器通信对接。

- 提供块的ECC校验相关的逻辑,也就是说iNand本身自己完成存储系统的ECC功能,SoC使用iNand时自己不用写代码来进行ECC相关操作,大大简化了SoC的编程难度。(NandFlash分2种:SLC和MLC,SLC更稳定,但是容量小价格高;MLC容易出错,但是容量大价格低)。

- iNand芯片内部使用MLC Nand颗粒,所以性价比很高。

- iNand接口电路还提供了cache机制,所以inand的操作速度很快。

3、iNand/eMMC的物理接口和SD卡物理接口的对比

(1)S5PV210芯片本身支持4通道的SD/MMC

- 在X210中实际是在SD/MMC0通道接了iNand芯片,而SD/MMC2接了SD卡(SD/MMC3也接了SD卡)。

(2)对比inand和SD卡接线

- 这两个接线几乎是一样的,唯一的区别就是SD卡IO线有4根,而iNand的IO线有8根。

- 在实际操作iNand芯片时和操作SD卡时几乎是一样的(物理接线几乎一样,软件操作协议几乎一样)。

- iNand/eMMC其实就是芯片化的SD/MMC卡,软件操作和SD卡相同。

- 分析iNand芯片的操作代码时,其实就是以前的SD卡的操作代码。一些细节的区别就是为了区分各种不同版本的SD卡、iNand的细节差异。

七、SD卡/iNand操作

1、硬件接口:DATA、CLK、CMD

(1)iNand的IO线有8根,支持1、4、8线并行传输模式;SD卡IO线有4根,支持1、4线并行传输模式。

(2)CMD线用来传输命令、CLK线用来传输时钟信号。

(2)接口有CLK线,工作时主机SoC通过CLK线传输时钟信号给SD卡/iNand芯片。

- SD/iNand是同步的,SD/iNand的工作速率是由主机给它的CLK频率决定的。

2、命令响应的操作模式

(1)SD协议事先定义很多标准命令(CMD0、CMD1……),每个命令都有它的作用和使用条件和对应的响应。

- 在一个命令周期中,主机先发送CMD给SD卡,然后SD卡解析这个命令并且执行这个命令;

- SD卡根据结果回发给主机SoC一个响应(有些命令是不需要响应的,这时SD卡不会给主机回发响应,主机也不用等待响应)。

(2)标准的“命令+响应”的周期中,主机发完一个命令后应该等待SD卡的响应而不是接着发下一条命令。

3、SD/iNand的体系结构图

(1)SD卡内部有一个接口控制器

- 其类似于一个单片机,功能是通过CMD线接收外部主机SoC发给SD卡的命令码,然后执行这个命令并且回发响应给主机SoC。

- 这个单片机处理命令及回发响应遵循的就是SD协议。这个单片机同时可以控制SD卡内部的存储单元,可以读写存储单元。

4、SD/iNand的寄存器(重点是RCA寄存器)

(1)SD卡内部的寄存器,而非主机SoC的SD控制器的寄存器。

- 很多外置芯片内部都是有寄存器的,这些寄存器可以按照一定的规则访问,访问这些寄存器可以得知芯片的一些信息。

(2)RCA(relative address,相对地址寄存器)

- 我们在访问SD卡时,实际上SD卡内部每个存储单元的地址没有绝对数字,都是使用相对地址。

- 相对地址由SD卡自己决定的,存放在RCA寄存器中。

5、SoC的SD/MMC/iNand控制器简介

(1)不同的SoC可能在SD/MMC/iNand等支持方面有差异,但是如果支持都是通过内部提供SD控制器来支持的。

(2)S5PV210的SD卡控制器在Section8.7部分。