FPGA Vivado AXI _DMA IP介绍

参考文档:《pg021》

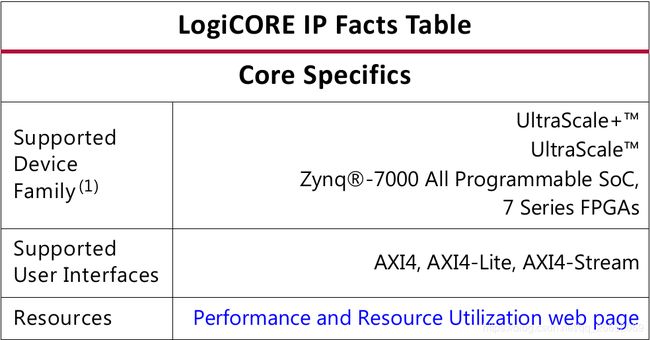

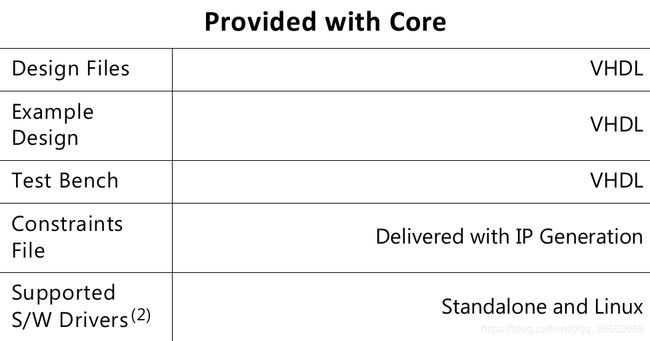

IP Facts

Introduction

AXI DMA内核是用于XilinxVivado®设计套件的软Xilinx IP内核。AXI DMA在内存和AXI4-Stream目标外设之间提供高带宽直接内存访问。其可选的分散/收集功能还可以从中央处理单元(CPU)卸载数据移动任务。

Features

• 符合AXI4标准 ;(Compliant合规)

• 可选分散/收集直接内存访问(DMA)支持

•AXI4数据位宽支持32, 64, 128, 256, 512和1024位;

•支持的用户接口:AXI4,AXI4-Lite,AXI4-Stream;

•支持多通道操作(最多16个通道)

•支持多通道模式下的二维(2-D)传输。

•AXI4-Stream数据宽度支持8,16,32,64,128,256,512和1,024位

•可选的孔眼支持;

•可选数据重新对齐支持流数据宽度高达512位。

•可选AXI控制和状态流;

•可选的Micro DMA支持;

•支持最多64位寻址;

Chapter1 Overview

AXI直接存储器访问(AXI DMA)IP内核在AXI4内存映射和AXI4-Stream IP接口之间提供高带宽直接内存访问。 其可选的分散收集功能(scatter/gather)还可以在基于处理器的系统中从中央处理单元(CPU)卸载数据移动任务。 通过AXI4-Lite从站接口访问初始化,状态和管理寄存器。 图1-1说明了芯的功能组成。

系统内存和流目标之间的主要的高速DMA数据搬移通过AXI4读主设备到AXI4内存映射到流(MM2S)主机,AXI流到内存映射(S2MM)从机到AX I4写主机。 AXI DMA还可以在分散/聚集模式下在MM2S和S2MM路径上实现多达16个多通道数据传输。

MM2S通道和S2MM通道独立运行。 AXI DMA提供4 KB地址边界保护(配置在非Micro DMA中),自动突发映射,以及使用AX I4-Stream总线的全部带宽功能提供多个传输请求的能力。 此外,AXI DMA提供字节级数据重新对准,允许从任何字节偏移位置开始的存储器读取和写入。

MM2S通道支持AXI控制流,将应用数据发送到目标IP。 对于S2MM通道,提供了一个AXI Status流,用于从目标IP接收用户应用程序数据。

可选的散点/收集引擎通过AXI4分散收集读/写主接口从系统内存中获取和更新缓冲区描述符。

Feature Summary

• 符合AXI4标准 (Compliant合规)

• 可选分散/收集直接内存访问(DMA)支持

- 提供从CPU卸载DMA管理工作

- 提供独立于主数据的转移脚本的提取和更新总线

- 允许描述符放置在与数据缓冲区分开的任何存储器映射位置。 例如,描述符可以放在块RAM中

- 可选择在分散/收集模式下在MM2S和S2MM路径上提供多达16个多通道的数据移动

- 提供可选的二维转移

- 提供可选的循环操作

•可选的直接寄存器模式(无分散/收集支持)

通过排除分散/收集引擎,可以启用较低性能但较少的FPGA资源密集型模式。 在此模式下,通过设置源地址(MM2S)或目标地址(对于S2MM),然后在长度寄存器中指定字节计数来命令传输。

• AXI4数据位宽支持32, 64, 128, 256, 512和1024位;

•主AXI4-Stream数据宽度支持8,16,32,64,128,256,512和1,024位

•可选数据重新对齐引擎,流数据宽度最大为512位

允许数据重新对齐主存储器映射和流数据路径上的字节(8位)级别

•可选的AXI控制和状态流,可与AXI以太网IP连接

为S2MM通道提供MM2S通道和状态流的可选控制流,以从高带宽数据通路卸载低带宽控制和状态。

•可选的微型模式(Micro Mode)

AXI DMA可配置为提供低占用空间,低性能的IP,可处理小数据包的传输。 有关更多信息,请阅读以下章节。

Application

AXI DMA在系统内存和基于AXI4-Stream的目标IP(如AXI以太网)之间提供高速数据移动。

Chapter2 Product Specification

性能

最高频率

延迟和吞吐量

表2-2和表2-3描述了AXI DMA的延迟和吞吐量。 这些表提供典型配置的性能信息。 吞吐量测试包括在MM2S和S2MM侧传输10,000个字节。是从描述符提取完成(DMACR.Idle = 1)到帧计数中断断言来测量的。

【注意】:

1.前面的图是使用默认IP配置进行测量的。

2.MM2S吞吐量在内存映射端的第一个无效到流媒体上的tlast之间进行测量。

3.S2MM吞吐量是在内存映射一侧的流式传输端的第一个tvalid与最后一个wlast之间进行测量的

Port Descriptions

AXI DMA I / O信号如表2-4所示。

| 名称 |

接口名 |

信号类 型 |

初始状态 |

描述 |

|

| s_axi_lite_aclk |

Clock |

I |

|

AXI4-Lite时钟 |

|

| m_axi_sg_aclk |

Clock |

I |

|

AXI DMA分散收集时钟 |

|

| m_axi_mm2s_aclk |

Clock |

I |

|

AXI DMA MM2S主时钟 |

|

| m_axi_s2mm_aclk |

Clock |

I |

|

AXI DMA S2MM主时钟 |

|

| axi_resetn |

Reset |

I |

|

AXI DMA复位。 低电平有效复位。 当置为低电平时,复位整个AXI DMA内核。必须与s_axi_lite_aclk同步。 |

|

| mm2s_introut |

Interrupt |

O |

0 |

用于内存映射到流信道的(MM2S)中断。 |

|

| s2mm_introut |

Interrupt |

O |

0 |

用于S2MM中断 |

|

| axi_dma_tstvec |

NA |

O |

0 |

供内部使用的调试信号。 |

|

| AXI4-Lite Interface Signals |

|||||

| s_axi_lite_* |

S_AXI_LITE |

I/O |

|

请参见“AXI参考指南”的附录A. (UG1037)[参考2] AXI4信号 |

|

| MM2S Memory Map Read Interface Signals |

|||||

| m_axi_mm2s_* |

M_AXI_MM2S |

I/O |

|

请参见“AXI参考指南”的附录A. (UG1037)[参考2] AXI4信号 |

|

| MM2S Master Stream Interface Signals |

|||||

| mm2s_prmry_reset_out_n |

M_AXIS_MM2S |

O |

1 |

主要MM2S复位输出。 低电平有效复位。 |

|

| m_axis_mm2s_* |

M_AXIS_MM2S |

I/O |

|

请参见“AXI参考指南”的附录A. (UG1037)[参考2] AXI4信号 |

|

| MM2S Master Control Stream Interface Signals |

|||||

| mm2s_cntrl_reset_out_n |

M_AXIS_CNTRL |

O |

1 |

控制复位输出。 低电平有效复位。 |

|

| m_axis_mm2s_cntrl_* |

M_AXIS_CNTRL |

I/O |

|

请参见“AXI参考指南”的附录A. (UG1037)[参考2] AXI4信号 |

|

| S2MM Memory Map Write Interface Signals |

|||||

| m_axi_s2mm_* |

M_AXI_S2MM |

I/O |

|

UG1037 |

|

| S2MM Slave Stream Interface Signals |

|||||

| s2mm_prmry_reset_out_n |

S_AXIS_S2MM |

O |

1 |

主S2MM复位输出。 低电平有效复位 |

|

| s_axis_s2mm_* |

S_AXIS_S2MM |

I |

Input/ Outpu |

UG1037 |

|

| S2MM Slave Status Stream Interface Signals |

|||||

| s2mm_sts_reset_out_n |

S_AXIS_STS |

O |

1 |

AXI状态流(STS)复位输出。 低电平有效复位。 |

|

| s_axis_s2mm_sts_* |

S_AXIS_STS |

input/ Output |

|

UG1037 |

|

| Scatter Gather Memory Map Read Interface Signals |

|||||

| m_axi_sg_* |

M_AXI_SG |

Input/ Outpu |

|

UG1037 |

|

| Scatter Gather Memory Map Write Interface Signals |

|||||

| m_axi_sg* |

M_AXI_SG |

Input/ Output |

|

UG1037 |

|

Register Space

Register Space

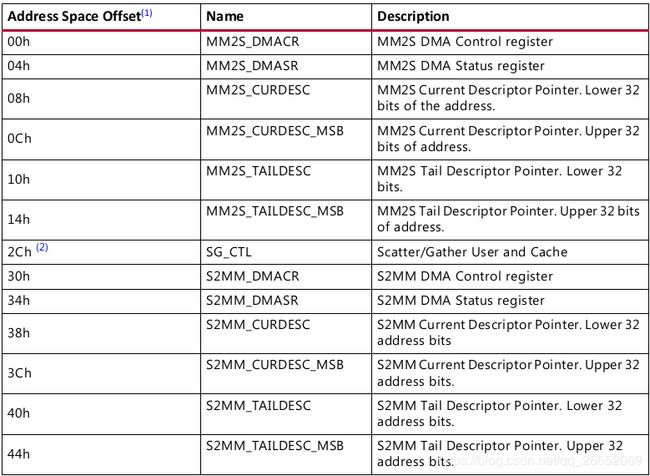

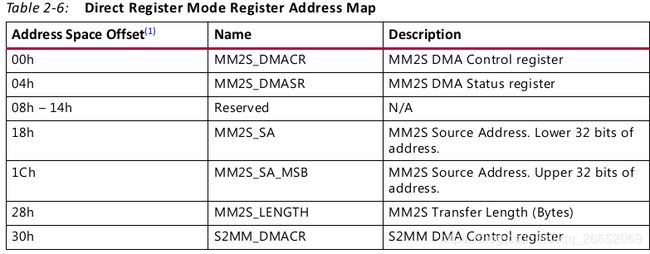

表2-5显示了用于分散/聚集模式的AXI DMA核心寄存器空间。 用于直接寄存器(DC)模式的AXI DMA内核寄存器空间如表2-6所示。 AXI DMA寄存器被内存映射到不可缓存的内存空间。 该存储器空间必须在AXI字(32位)边界上对齐。

【注意】:AXI4-Lite写访问寄存器由32位AXI写数据(* _wdata)信号更新,不受AXI写入数据选通(* _wstrb)信号的影响。 对于写入,AXI写入地址有效(* _awvalid)和AXI写入数据有效(* _wvalid)信号应一起被断言。

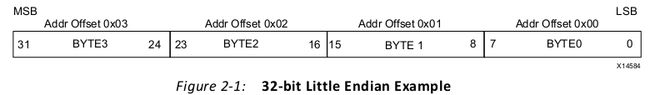

Endianess(字节序)

所有寄存器均为小端格式,如图2-1所示

AXI DMA Register Address Map

scatter/gather模式寄存器地址映射图

【注意】:

1.地址空间偏移量相对于C_BASEADDR赋值。

2.寄存器2Ch仅在DM A配置为多通道模式时可用。

【注】:

地址空间偏移量相对于C_BASEADDR赋值

Memory Map to Stream Register Detail

待整理