猜数字游戏代码:importrandomdefpythonit():a=random.randint(1,100)n=int(input("输入你猜想的数字:"))whilen!=a:ifn>a:print("很遗憾,猜大了")n=int(input("请再次输入你猜想的数字:"))elifna::如果玩家猜的数字n大于随机数字a,则输出"很遗憾,猜大了",并提示玩家再次输入。elifn

2024.9.14 Python,差分法解决区间加法,消除游戏,压缩字符串

RaidenQ

python游戏开发语言算法力扣

1.区间加法假设你有一个长度为n的数组,初始情况下所有的数字均为0,你将会被给出k个更新的操作。其中,每个操作会被表示为一个三元组:[startIndex,endIndex,inc],你需要将子数组A[startIndex…endIndex](包括startIndex和endIndex)增加inc。请你返回k次操作后的数组。示例:输入:length=5,updates=[[1,3,2],[2,4,

简单说说关于shell中zsh和bash的选择

秋刀prince

MacOS小猿们的开发日常bash

希望文章能给到你启发和灵感~如果觉得文章对你有帮助的话,点赞+关注+收藏支持一下博主吧~阅读指南开篇说明一、基础环境说明1.1硬件环境1.2软件环境二、什么是shell、bash、zsh?2.1bash2.2zsh三、选择Bash还是Zsh?四、一些常见问题开篇说明本篇主要简单说明一下,shell中bash和zsh的区别和选择;我们经常会把这两个搞混,不知道什么时候用哪一个,以及怎么使用;一、基础

ARM V8 base instruction -- Debug instructions

xiaozhiwise

Assemblyarm

/**Debuginstructions*/BRK#imm16进入monitormodedebug,那里有on-chipdebugmonitorcodeHLT#imm16进入haltmodedebug,连接有外部调试硬件

ARMv8 Debug

__pop_

ARMv8ARM64架构linux运维

内容来自DEN0024A_v8_architecture_PG.pdf本质ARMv8Debug是什么历史在ARMv4开始被引入,并已发展成一系列广泛的调试(debug1)和跟踪(trace)功能ARMv6和ARMv7-a新增了自托管调试(debug2)和性能评测(trace-enhance)ARMv8处理器提供硬件功能侵入式:调试工具能够对核心活动提供显著级别的控制非侵入式:以非侵入性方式收集有关

Android应用性能优化

轻口味

Android

Android手机由于其本身的后台机制和硬件特点,性能上一直被诟病,所以软件开发者对软件本身的性能优化就显得尤为重要;本文将对Android开发过程中性能优化的各个方面做一个回顾与总结。Cache优化ListView缓存:ListView中有一个回收器,Item滑出界面的时候View会回收到这里,需要显示新的Item的时候,就尽量重用回收器里面的View;每次在getView函数中inflate新

258-各位相加

不胖二十斤不改名zz

给定一个非负整数num,反复将各个位上的数字相加,直到结果为一位数。输入:38输出:2解释:各位相加的过程为:3+8=11,1+1=2。由于2是一位数,所以返回2。最简单的方法就是递归了。进阶:你可以不使用循环或者递归,且在O(1)时间复杂度内解决这个问题吗?假如一个三位数'abc',其值大小为s1=100*a+10*b+1*c,经过一次各位相加后,变为s2=a+b+c,减小的差值为(s1-s2)

iPhone怎么删除重复照片,可以尝试这几种方法

2401_85240355

iphoneios

在数字化时代,智能手机尤其是iPhone成为我们日常生活中不可或缺的一部分。随着我们不断使用iPhone拍照,重复照片的积累逐渐成为一个普遍问题。这不仅占用了大量的存储空间,也使得照片库变得杂乱无章。本文将介绍几种有效的iPhone怎么删除重复照片方法,并介绍如何利用CleanMyPhone来简化这一过程。iPhone怎么删除重复照片方法一:人工筛查人工筛查是最直接的方法,尽管它可能比较耗时。这种

【Python搞定车载自动化测试】——Python实现车载以太网DoIP刷写(含Python源码)

疯狂的机器人

Python搞定车载自动化pythonDoIPUDSISO142291SO13400Bootloadertcp/ip

系列文章目录【Python搞定车载自动化测试】系列文章目录汇总文章目录系列文章目录前言一、环境搭建1.软件环境2.硬件环境二、目录结构三、源码展示1.DoIP诊断基础函数方法2.DoIP诊断业务函数方法3.27服务安全解锁4.DoIP自动化刷写四、测试日志1.测试日志五、完整源码链接前言随着智能电动汽车行业的发展,汽车=智能终端+四个轮子,各家车企都推出了各自的OTA升级方案,本章节主要介绍如何使

深入浅出 -- 系统架构之负载均衡Nginx的性能优化

xiaoli8748_软件开发

系统架构系统架构负载均衡nginx

一、Nginx性能优化到这里文章的篇幅较长了,最后再来聊一下关于Nginx的性能优化,主要就简单说说收益最高的几个优化项,在这块就不再展开叙述了,毕竟影响性能都有多方面原因导致的,比如网络、服务器硬件、操作系统、后端服务、程序自身、数据库服务等,对于性能调优比较感兴趣的可以参考之前《JVM性能调优》中的调优思想。优化一:打开长连接配置通常Nginx作为代理服务,负责分发客户端的请求,那么建议开启H

如何利用大数据与AI技术革新相亲交友体验

h17711347205

回归算法安全系统架构交友小程序

在数字化时代,大数据和人工智能(AI)技术正逐渐革新相亲交友体验,为寻找爱情的过程带来前所未有的变革(编辑h17711347205)。通过精准分析和智能匹配,这些技术能够极大地提高相亲交友系统的效率和用户体验。大数据的力量大数据技术能够收集和分析用户的行为模式、偏好和互动数据,为相亲交友系统提供丰富的信息资源。通过分析用户的搜索历史、浏览记录和点击行为,系统能够深入了解用户的兴趣和需求,从而提供更

线上到线下:相亲交友系统如何打造全方位恋爱体验

h17711347205

人工智能大数据

在数字化时代,相亲交友系统正逐渐成为单身人士寻找伴侣的重要渠道。我们的目标是打造一个全方位的恋爱体验,将线上的便捷性与线下的真实互动相结合,为用户提供一个无缝衔接的交友平台。以下是如何从运营角度出发,实现这一目标的详细策略。线上到线下:相亲交友系统如何打造全方位恋爱体验在快节奏的现代社会,相亲交友系统为单身人士提供了一个便捷的相识途径17711347205。然而,真正的恋爱体验往往需要线下的真实互

【日记】2023.10.31十月

冰瑗

不知不觉,十月走到了尾声,从灿烂的阳光走向了灿烂的落叶。以前我看日历,总会觉得一个月的时间很快就会过去,在日历上短短的四行数字,是呼吸间就能读完的几行,可是真正经历过后,才蓦然发觉,似乎太多事情的堆叠,让我觉得像是过了很久。十一回家的路途还历历在目,辗转在火车站里的凌晨,和到达沈阳站看到的破晓的霞光,在今夜都让我觉得恍若隔世。翻看之前记录的有关十月的日记,有很多都是心情的起伏,其实每一天还是平静悠

信息系统安全相关概念(上)

YuanDaima2048

课程笔记基础概念安全信息安全笔记

文章总览:YuanDaiMa2048博客文章总览下篇:信息系统安全相关概念(下)信息系统安全相关概念[上]信息系统概述信息系统信息系统架构信息系统发展趋势:信息系统日趋大型化、复杂化信息系统面临的安全威胁信息系统安全架构设计--以云计算为例信息系统安全需求及安全策略自主访问控制策略DAC强制访问控制策略MAC信息系统概述信息系统用于收集、存储和处理数据以及传递信息、知识和数字产品的一组集成组件。几

我的总资产6.666

莱莱克西

刚才打开,准备日更,顺便看了一眼自己在里面的资产。咦…总资产6.666,突然觉得这个数字应该截一下屏,保留下来。纯粹觉得这个数字这么刚刚好还挺吉利也挺难得的(我是个迷信鬼吧……)。然后今天日更的主题一下子就有了。大多数时候在打开前还不知道当天要写点什么,但神奇的是,当我打开之后,略略思索一下,灵感立马就来了。我想这大概就是写作的魅力,不去下笔就永远不知道自己能写出什么东西来。起初来也是为了锻炼自己

C++常见知识掌握

nfgo

c++开发语言

1.Linux软件开发、调试与维护内核与系统结构Linux内核是操作系统的核心,负责管理硬件资源,提供系统服务,它是系统软件与硬件之间的桥梁。主要组成部分包括:进程管理:内核通过调度器分配CPU时间给各个进程,实现进程的创建、调度、终止等操作。使用进程描述符(task_struct)来存储进程信息,包括状态(就绪、运行、阻塞等)、优先级、内存映射等。内存管理:包括物理内存和虚拟内存管理。通过页表映

广东麻将开发

红匣子实力推荐

在中国,麻将作为一种深受人们喜爱的传统娱乐活动,已经有着数百年的历史。随着互联网和移动设备的普及,麻将游戏也从实体桌面转移到了数字平台,其中广东麻将因其独特的地方特色和玩法而备受青睐。本文将介绍广东麻将的开发过程,包括其设计理念、技术实现以及用户体验优化等方面。一、设计理念:广东麻将开发的核心理念是保留传统麻将的精髓,同时融入现代科技元素,使游戏既具有亲切感又不失趣味性。开发者通常会深入研究广东地

炒币好还是挖矿好?

区块链大社会

炒币好还是挖矿好?相信这个问题对于很多初入行的朋友来说是个不小的问题,小编也经常会被问到类似问题。为此,本文专门针对这个问题做一下分析,供各位朋友们参考。在比特币世界里,有些非常有意思的比喻,像挖金子一样“挖”比特币叫做“挖矿”,挖比特币的人被称为“矿工”,而用于“挖”比特币的电脑被称为“矿机”。而“炒币”就像炒股,直接在交易平台购买数字货币进行交易,不需要“挖”,只要将法币兑换成某种数字货币,再

jsonp 常用util方法

hw1287789687

jsonpjsonp常用方法jsonp callback

jsonp 常用java方法

(1)以jsonp的形式返回:函数名(json字符串)

/***

* 用于jsonp调用

* @param map : 用于构造json数据

* @param callback : 回调的javascript方法名

* @param filters : <code>SimpleBeanPropertyFilter theFilt

多线程场景

alafqq

多线程

0

能不能简单描述一下你在java web开发中需要用到多线程编程的场景?0

对多线程有些了解,但是不太清楚具体的应用场景,能简单说一下你遇到的多线程编程的场景吗?

Java多线程

2012年11月23日 15:41 Young9007 Young9007

4

0 0 4

Comment添加评论关注(2)

3个答案 按时间排序 按投票排序

0

0

最典型的如:

1、

Maven学习——修改Maven的本地仓库路径

Kai_Ge

maven

安装Maven后我们会在用户目录下发现.m2 文件夹。默认情况下,该文件夹下放置了Maven本地仓库.m2/repository。所有的Maven构件(artifact)都被存储到该仓库中,以方便重用。但是windows用户的操作系统都安装在C盘,把Maven仓库放到C盘是很危险的,为此我们需要修改Maven的本地仓库路径。

placeholder的浏览器兼容

120153216

placeholder

【前言】

自从html5引入placeholder后,问题就来了,

不支持html5的浏览器也先有这样的效果,

各种兼容,之前考虑,今天测试人员逮住不放,

想了个解决办法,看样子还行,记录一下。

【原理】

不使用placeholder,而是模拟placeholder的效果,

大概就是用focus和focusout效果。

【代码】

<scrip

debian_用iso文件创建本地apt源

2002wmj

Debian

1.将N个debian-506-amd64-DVD-N.iso存放于本地或其他媒介内,本例是放在本机/iso/目录下

2.创建N个挂载点目录

如下:

debian:~#mkdir –r /media/dvd1

debian:~#mkdir –r /media/dvd2

debian:~#mkdir –r /media/dvd3

….

debian:~#mkdir –r /media

SQLSERVER耗时最长的SQL

357029540

SQL Server

对于DBA来说,经常要知道存储过程的某些信息:

1. 执行了多少次

2. 执行的执行计划如何

3. 执行的平均读写如何

4. 执行平均需要多少时间

列名 &

com/genuitec/eclipse/j2eedt/core/J2EEProjectUtil

7454103

eclipse

今天eclipse突然报了com/genuitec/eclipse/j2eedt/core/J2EEProjectUtil 错误,并且工程文件打不开了,在网上找了一下资料,然后按照方法操作了一遍,好了,解决方法如下:

错误提示信息:

An error has occurred.See error log for more details.

Reason:

com/genuitec/

用正则删除文本中的html标签

adminjun

javahtml正则表达式去掉html标签

使用文本编辑器录入文章存入数据中的文本是HTML标签格式,由于业务需要对HTML标签进行去除只保留纯净的文本内容,于是乎Java实现自动过滤。

如下:

public static String Html2Text(String inputString) {

String htmlStr = inputString; // 含html标签的字符串

String textSt

嵌入式系统设计中常用总线和接口

aijuans

linux 基础

嵌入式系统设计中常用总线和接口

任何一个微处理器都要与一定数量的部件和外围设备连接,但如果将各部件和每一种外围设备都分别用一组线路与CPU直接连接,那么连线

Java函数调用方式——按值传递

ayaoxinchao

java按值传递对象基础数据类型

Java使用按值传递的函数调用方式,这往往使我感到迷惑。因为在基础数据类型和对象的传递上,我就会纠结于到底是按值传递,还是按引用传递。其实经过学习,Java在任何地方,都一直发挥着按值传递的本色。

首先,让我们看一看基础数据类型是如何按值传递的。

public static void main(String[] args) {

int a = 2;

ios音量线性下降

bewithme

ios音量

直接上代码吧

//second 几秒内下降为0

- (void)reduceVolume:(int)second {

KGVoicePlayer *player = [KGVoicePlayer defaultPlayer];

if (!_flag) {

_tempVolume = player.volume;

与其怨它不如爱它

bijian1013

选择理想职业规划

抱怨工作是年轻人的常态,但爱工作才是积极的心态,与其怨它不如爱它。

一般来说,在公司干了一两年后,不少年轻人容易产生怨言,除了具体的埋怨公司“扭门”,埋怨上司无能以外,也有许多人是因为根本不爱自已的那份工作,工作完全成了谋生的手段,跟自已的性格、专业、爱好都相差甚远。

一边时间不够用一边浪费时间

bingyingao

工作时间浪费

一方面感觉时间严重不够用,另一方面又在不停的浪费时间。

每一个周末,晚上熬夜看电影到凌晨一点,早上起不来一直睡到10点钟,10点钟起床,吃饭后玩手机到下午一点。

精神还是很差,下午像一直野鬼在城市里晃荡。

为何不尝试晚上10点钟就睡,早上7点就起,时间完全是一样的,把看电影的时间换到早上,精神好,气色好,一天好状态。

控制让自己周末早睡早起,你就成功了一半。

有多少个工作

【Scala八】Scala核心二:隐式转换

bit1129

scala

Implicits work like this: if you call a method on a Scala object, and the Scala compiler does not see a definition for that method in the class definition for that object, the compiler will try to con

sudoku slover in Haskell (2)

bookjovi

haskellsudoku

继续精简haskell版的sudoku程序,稍微改了一下,这次用了8行,同时性能也提高了很多,对每个空格的所有解不是通过尝试算出来的,而是直接得出。

board = [0,3,4,1,7,0,5,0,0,

0,6,0,0,0,8,3,0,1,

7,0,0,3,0,0,0,0,6,

5,0,0,6,4,0,8,0,7,

Java-Collections Framework学习与总结-HashSet和LinkedHashSet

BrokenDreams

linkedhashset

本篇总结一下两个常用的集合类HashSet和LinkedHashSet。

它们都实现了相同接口java.util.Set。Set表示一种元素无序且不可重复的集合;之前总结过的java.util.List表示一种元素可重复且有序

读《研磨设计模式》-代码笔记-备忘录模式-Memento

bylijinnan

java设计模式

声明: 本文只为方便我个人查阅和理解,详细的分析以及源代码请移步 原作者的博客http://chjavach.iteye.com/

import java.util.ArrayList;

import java.util.List;

/*

* 备忘录模式的功能是,在不破坏封装性的前提下,捕获一个对象的内部状态,并在对象之外保存这个状态,为以后的状态恢复作“备忘”

《RAW格式照片处理专业技法》笔记

cherishLC

PS

注意,这不是教程!仅记录楼主之前不太了解的

一、色彩(空间)管理

作者建议采用ProRGB(色域最广),但camera raw中设为ProRGB,而PS中则在ProRGB的基础上,将gamma值设为了1.8(更符合人眼)

注意:bridge、camera raw怎么设置显示、输出的颜色都是正确的(会读取文件内的颜色配置文件),但用PS输出jpg文件时,必须先用Edit->conv

使用 Git 下载 Spring 源码 编译 for Eclipse

crabdave

eclipse

使用 Git 下载 Spring 源码 编译 for Eclipse

1、安装gradle,下载 http://www.gradle.org/downloads

配置环境变量GRADLE_HOME,配置PATH %GRADLE_HOME%/bin,cmd,gradle -v

2、spring4 用jdk8 下载 https://jdk8.java.

mysql连接拒绝问题

daizj

mysql登录权限

mysql中在其它机器连接mysql服务器时报错问题汇总

一、[running]

[email protected]:~$mysql -uroot -h 192.168.9.108 -p //带-p参数,在下一步进行密码输入

Enter password: //无字符串输入

ERROR 1045 (28000): Access

Google 今天在 Chromium 官方博客宣布由于 H.264 编解码器并非开放标准,Chrome 将在几个月后正式停止对 H.264 视频解码的支持,全面采用开放的 WebM 和 Theora 格式。

Google 在博客上表示,自从 WebM 视频编解码器推出以后,在性能、厂商支持以及独立性方面已经取得了很大的进步,为了与 Chromium 现有支持的編解码器保持一致,Chrome

yii 获取控制器名 和方法名

dcj3sjt126com

yiiframework

1. 获取控制器名

在控制器中获取控制器名: $name = $this->getId();

在视图中获取控制器名: $name = Yii::app()->controller->id;

2. 获取动作名

在控制器beforeAction()回调函数中获取动作名: $name =

Android知识总结(二)

come_for_dream

android

明天要考试了,速速总结如下

1、Activity的启动模式

standard:每次调用Activity的时候都创建一个(可以有多个相同的实例,也允许多个相同Activity叠加。)

singleTop:可以有多个实例,但是不允许多个相同Activity叠加。即,如果Ac

高洛峰收徒第二期:寻找未来的“技术大牛” ——折腾一年,奖励20万元

gcq511120594

工作项目管理

高洛峰,兄弟连IT教育合伙人、猿代码创始人、PHP培训第一人、《细说PHP》作者、软件开发工程师、《IT峰播》主创人、PHP讲师的鼻祖!

首期现在的进程刚刚过半,徒弟们真的很棒,人品都没的说,团结互助,学习刻苦,工作认真积极,灵活上进。我几乎会把他们全部留下来,现在已有一多半安排了实际的工作,并取得了很好的成绩。等他们出徒之日,凭他们的能力一定能够拿到高薪,而且我还承诺过一个徒弟,当他拿到大学毕

linux expect

heipark

expect

1. 创建、编辑文件go.sh

#!/usr/bin/expect

spawn sudo su admin

expect "*password*" { send "13456\r\n" }

interact

2. 设置权限

chmod u+x go.sh 3.

Spring4.1新特性——静态资源处理增强

jinnianshilongnian

spring 4.1

目录

Spring4.1新特性——综述

Spring4.1新特性——Spring核心部分及其他

Spring4.1新特性——Spring缓存框架增强

Spring4.1新特性——异步调用和事件机制的异常处理

Spring4.1新特性——数据库集成测试脚本初始化

Spring4.1新特性——Spring MVC增强

Spring4.1新特性——页面自动化测试框架Spring MVC T

idea ubuntuxia 乱码

liyonghui160com

1.首先需要在windows字体目录下或者其它地方找到simsun.ttf 这个 字体文件。

2.在ubuntu 下可以执行下面操作安装该字体:

sudo mkdir /usr/share/fonts/truetype/simsun

sudo cp simsun.ttf /usr/share/fonts/truetype/simsun

fc-cache -f -v

改良程序的11技巧

pda158

技巧

有很多理由都能说明为什么我们应该写出清晰、可读性好的程序。最重要的一点,程序你只写一次,但以后会无数次的阅读。当你第二天回头来看你的代码 时,你就要开始阅读它了。当你把代码拿给其他人看时,他必须阅读你的代码。因此,在编写时多花一点时间,你会在阅读它时节省大量的时间。

让我们看一些基本的编程技巧:

尽量保持方法简短

永远永远不要把同一个变量用于多个不同的

300个涵盖IT各方面的免费资源(下)——工作与学习篇

shoothao

创业免费资源学习课程远程工作

工作与生产效率:

A. 背景声音

Noisli:背景噪音与颜色生成器。

Noizio:环境声均衡器。

Defonic:世界上任何的声响都可混合成美丽的旋律。

Designers.mx:设计者为设计者所准备的播放列表。

Coffitivity:这里的声音就像咖啡馆里放的一样。

B. 避免注意力分散

Self Co

深入浅出RPC

uule

rpc

深入浅出RPC-浅出篇

深入浅出RPC-深入篇

RPC

Remote Procedure Call Protocol

远程过程调用协议

它是一种通过网络从远程计算机程序上请求服务,而不需要了解底层网络技术的协议。RPC协议假定某些传输协议的存在,如TCP或UDP,为通信程序之间携带信息数据。在OSI网络通信模型中,RPC跨越了传输层和应用层。RPC使得开发

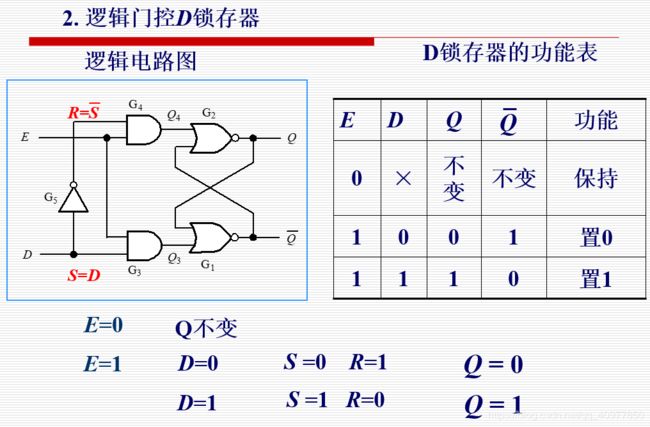

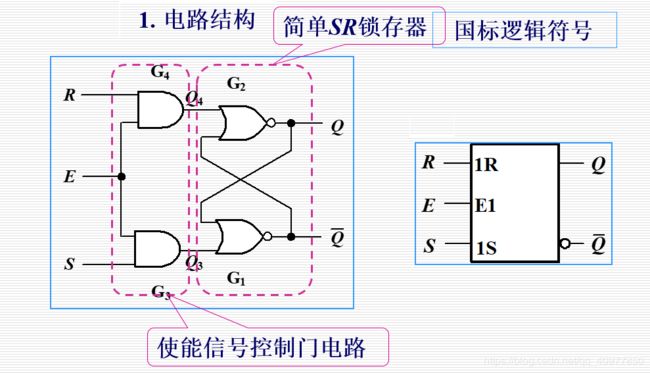

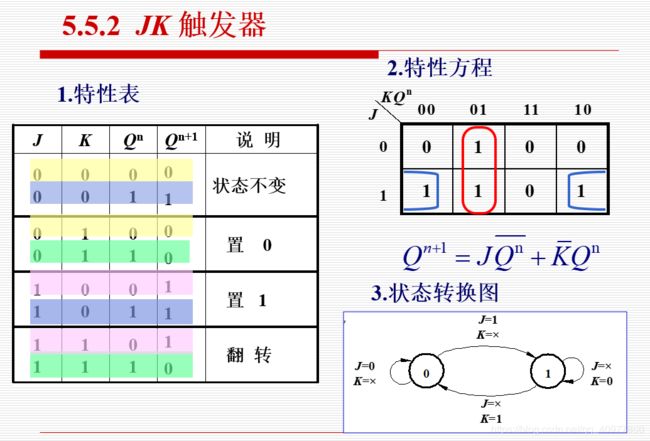

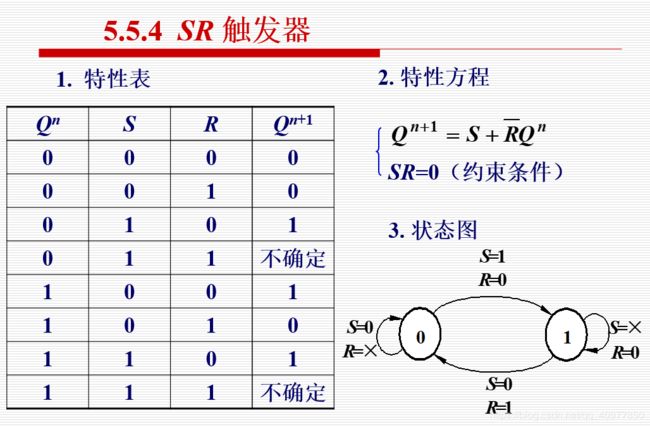

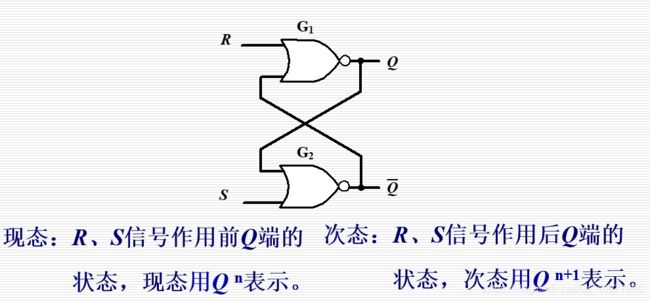

状态0:当R=0、S=0时,若Qn=1,则Qn+1=1,,若Qn=0,则Qn+1=0

状态0:当R=0、S=0时,若Qn=1,则Qn+1=1,,若Qn=0,则Qn+1=0