FPGA实现RAM--LPM_RAM

软件环境:QuartusII 11.0

操作系统:win7

实现方法一、利用LPM_RAM:

1.首先准备好存储器初始化文件,即.mif文件。

该文件的生成方法见《如何生成mif文件》;

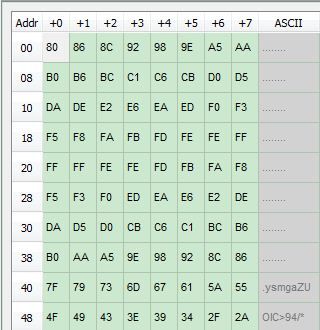

本文预先生成了一个正弦波的数据文件,TEST1.mif,可以在QuartusII中打开,以便查看内容:【file】/【open】,在文件类型中选择memory files,打开TEST1.mif,内容如下:

2.生成LPM_RAM块

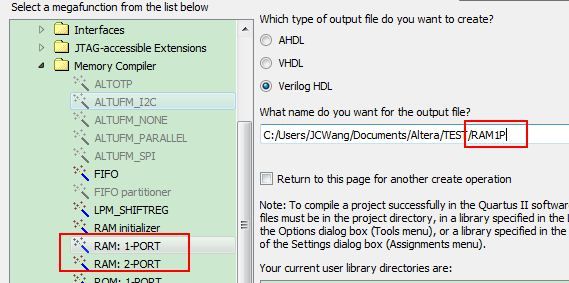

1)在QuartusII中,【tools】/【megawizard plugin manager】,打开向导,选择【memory compiler】文件夹下的RAM:这里选择单口RAM,

即:RAM:1-PORT,命名为RAM1P:

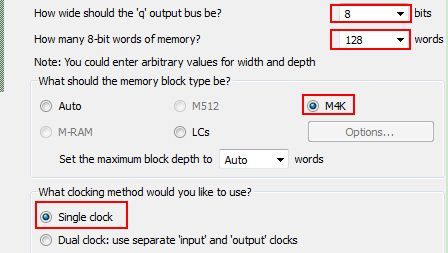

2)设置存储深度为128,数据宽度为8bit、选择嵌入式M4K RAM实现、使用单时钟方案:

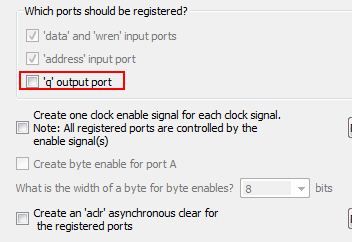

3)取消选择“数据输出锁存”,不需要时钟使能端:

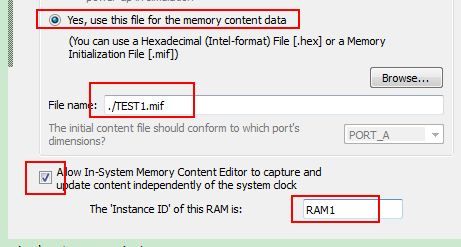

4)使用mif初始化该RAM块、允许“在系统(In System)存储器读写”,并将此RAM的ID设置为RAM1:

- 载入前面生成的存储器初始化文件:TEST1.mif;

- ID主要用于多RAM系统时,对不同RAM的识别,此处命名为RAM1;

- 关于“在系统存储器读写”的含义,后续会补一片文章,专门介绍该工具的使用;

经过以上设置,即可生成一个名字为RAM1P.v的文件,以后就可以对其进行例化和使用。

3. 对RAM1P.v进行例化,就可以使用,例化方法如下:

module TEST( input [6:0] address, input clock, input [7:0] data, input wren, output [7:0] q ); RAM1P RAM1P_inst ( .address ( address ), .clock ( clock ), .data ( data ), .wren ( wren ), .q ( q ) ); endmodule

推荐使用verilog文本的方式进行例化,博主十分不赞成用原理图的方式来例化各个模块。

生成的RTL图:

4.对该RAM块进行仿真,以便了解端口的特性:

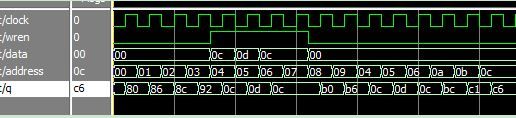

- 由于使用的时钟方案为单时钟(single clock),因此无论wren=0还是1,Q都输出address指定的地址中的数据;可以从verilog描述中看出这是利用assign语句实现的(verilog代码见下文)。

- 当wren=1时,将数据输入端data的数据写入到address指定的存储单元内。

输出的数据依次为0x80,0x86,0x8c,0x92……,对比前文所显示的mif文件内容,可以验证mif文件已经成功导入;

而接下来输出的数据0x0c、0x0d、0x0c、0x0c,是在wren=1期间,由数据输入端data写入到地址04、05、06、07中的数据;

接下来继续输出0xb0、0xb6……,则仍然为mif中对应地址的初始化数据。

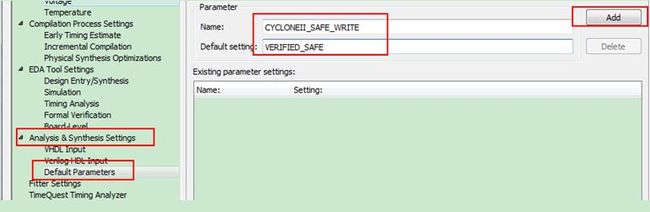

说明:在编译过程中,如果使用cycloneII器件,可能会出现错误“Error: M4K memory block WYSIWYG primitive……”,解决办法为:

【ASSIGNMENTS 】/【 SETTING】,找到如下位置,在name中输入“CYCLONEII_SAFE_WRITE”,在DEFAULT SETTING中输入“VERIFIED_SAFE”;

然后点击add按钮:

方法二、使用verilog纯文本的描述方式:

生成同样功能的RAM块,代码如下:

module RAM1P( input [6:0] address, input clock, input [7:0] data, input wren, output [7:0] q ); (* ram_init_file = "TEST1.mif " *) reg [7:0] mem[127:0]; always@(posedge clock) if(wren) mem[address] <= data; /*在时钟的上升沿写入数据*/ assign q = mem[address]; endmodule

注意此时mif文件载入RAM的方法,是利用文本描述的方式实现的,此种方式有一个缺点,就是不能在modelsim中进行仿真:

(* ram_init_file = "TEST1.mif " *) reg [7:0] mem[127:0];

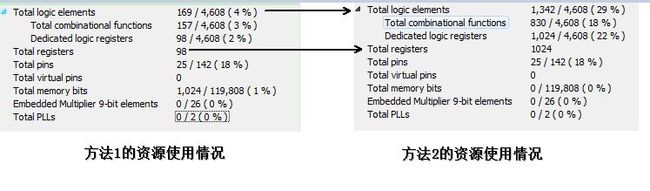

对比两种方法的优缺点:

经过QuartusII的编译报告可以看出,方法2比方法1相比,占用了很多的LE,同时还使用了1024个register,故方法2是十分不经济的,这里给出只是提供一个参考,便于理解LPM_RAM的工作方式,平时应用时,建议使用方法1来构建RAM。