- SQL Server_查询某一数据库中的所有表的内容

qq_42772833

SQLServer数据库sqlserver

1.查看所有表的表名要列出CrabFarmDB数据库中的所有表(名),可以使用以下SQL语句:USECrabFarmDB;--切换到目标数据库GOSELECTTABLE_NAMEFROMINFORMATION_SCHEMA.TABLESWHERETABLE_TYPE='BASETABLE';对这段SQL脚本的解释:SELECTTABLE_NAME:这个语句的作用是从查询结果中选择TABLE_NAM

- libyuv之linux编译

jaronho

Linuxlinux运维服务器

文章目录一、下载源码二、编译源码三、注意事项1、银河麒麟系统(aarch64)(1)解决armv8-a+dotprod+i8mm指令集支持问题(2)解决armv9-a+sve2指令集支持问题一、下载源码到GitHub网站下载https://github.com/lemenkov/libyuv源码,或者用直接用git克隆到本地,如:gitclonehttps://github.com/lemenko

- ARM中断处理过程

落汤老狗

嵌入式linux

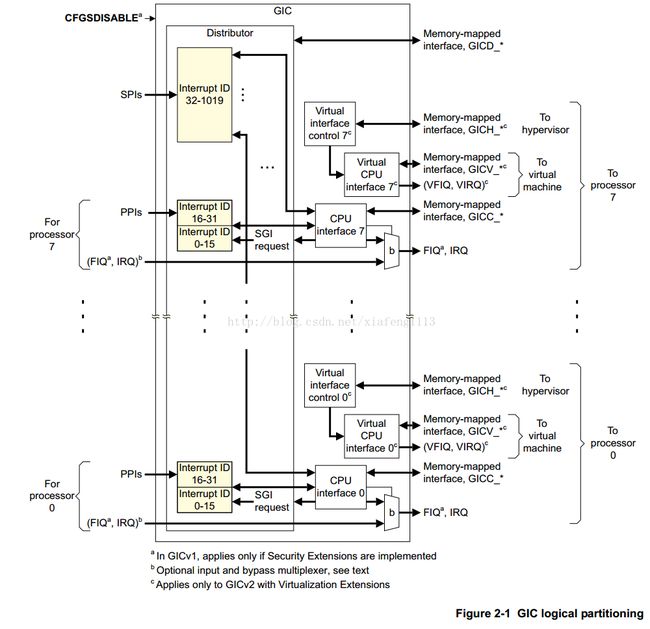

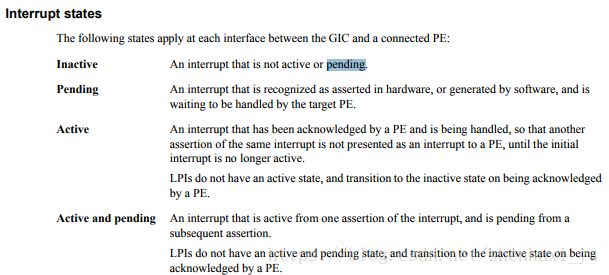

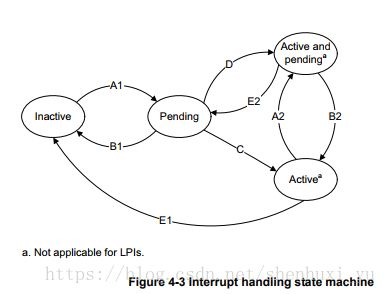

一、前言本文主要以ARM体系结构下的中断处理为例,讲述整个中断处理过程中的硬件行为和软件动作。具体整个处理过程分成三个步骤来描述:1、第二章描述了中断处理的准备过程2、第三章描述了当发生中的时候,ARM硬件的行为3、第四章描述了ARM的中断进入过程4、第五章描述了ARM的中断退出过程本文涉及的代码来自3.14内核。另外,本文注意描述ARM指令集的内容,有些sourcecode为了简短一些,删除了T

- ARM驱动学习之基础小知识

JT灬新一

ARM嵌入式arm开发学习

ARM驱动学习之基础小知识•sch原理图工程师工作内容–方案–元器件选型–采购(能不能买到,价格)–原理图(涉及到稳定性)•layout画板工程师–layout(封装、布局,布线,log)(涉及到稳定性)–焊接的一部分工作(调试阶段板子的焊接)•驱动工程师–驱动,原理图,layout三部分的交集容易发生矛盾•PCB研发流程介绍–方案,原理图(网表)–layout工程师(gerber文件)–PCB板

- ARM驱动学习之5 LEDS驱动

JT灬新一

嵌入式C底层arm开发学习单片机

ARM驱动学习之5LEDS驱动知识点:•linuxGPIO申请函数和赋值函数–gpio_request–gpio_set_value•三星平台配置GPIO函数–s3c_gpio_cfgpin•GPIO配置输出模式的宏变量–S3C_GPIO_OUTPUT注意点:DRIVER_NAME和DEVICE_NAME匹配。实现步骤:1.加入需要的头文件://Linux平台的gpio头文件#include//三

- ARM驱动学习之4小结

JT灬新一

嵌入式C++arm开发学习linux

ARM驱动学习之4小结#include#include#include#include#include#defineDEVICE_NAME"hello_ctl123"MODULE_LICENSE("DualBSD/GPL");MODULE_AUTHOR("TOPEET");staticlonghello_ioctl(structfile*file,unsignedintcmd,unsignedlo

- Python编译器

鹿鹿~

Python编译器Pythonpython开发语言后端

嘿嘿嘿我又来了啊有些小盆友可能不知道Python其实是有编译器的,也就是PyCharm。你们可能会问到这个是干嘛的又不可以吃也不可以穿好像没有什么用,其实你还说对了这个还真的不可以吃也不可以穿,但是它用来干嘛的呢。用来编译你所打出的代码进行运行(可能这里说的有点不对但是只是个人认为)现在我们来说说PyCharm是用来干嘛的。PyCharm是一种PythonIDE,带有一整套可以帮助用户在使用Pyt

- ARM V8 base instruction -- Debug instructions

xiaozhiwise

Assemblyarm

/**Debuginstructions*/BRK#imm16进入monitormodedebug,那里有on-chipdebugmonitorcodeHLT#imm16进入haltmodedebug,连接有外部调试硬件

- Armv8.3 体系结构扩展--原文版

代码改变世界ctw

ARM-TEE-Androidarmv8嵌入式arm架构安全架构芯片TrustzoneSecureboot

快速链接:.ARMv8/ARMv9架构入门到精通-[目录]付费专栏-付费课程【购买须知】:个人博客笔记导读目录(全部)TheArmv8.3architectureextensionTheArmv8.3architectureextensionisanextensiontoArmv8.2.Itaddsmandatoryandoptionalarchitecturalfeatures.Somefeat

- ARMv8 Debug

__pop_

ARMv8ARM64架构linux运维

内容来自DEN0024A_v8_architecture_PG.pdf本质ARMv8Debug是什么历史在ARMv4开始被引入,并已发展成一系列广泛的调试(debug1)和跟踪(trace)功能ARMv6和ARMv7-a新增了自托管调试(debug2)和性能评测(trace-enhance)ARMv8处理器提供硬件功能侵入式:调试工具能够对核心活动提供显著级别的控制非侵入式:以非侵入性方式收集有关

- 【ARM Cortex-M 系列 2.3 -- Cortex-M7 Debug event 详细介绍】

主公讲 ARM

#ARM系列arm开发debugevent

请阅读【嵌入式开发学习必备专栏】文章目录Cortex-M7DebugeventDebugeventsCortex-M7Debugevent在ARMCortex-M7架构中,调试事件(DebugEvent)是由于调试原因而触发的事件。一个调试事件会导致以下几种情况之一发生:进入调试状态:如果启用了停滞调试(HaltingDebug),一个调试事件会使处理器在调试状态下停滞。通过将DHCSR.C_DE

- ARMV8体系结构简介:概述

简单同学

ARMV8体系结构ARMV8

1.前言本文主要概括的介绍ARMV8体系结构定义了哪些内容,概括的说:ARM体系结构定义了PE的行为,不会定义具体的实现ARM体系结构也定义了debug体系结构和trace体系结构ARM体系结构采用RISC指令集(1)长度一致的寄存器;(2)load/store架构,数据处理操作只能对寄存器内容进行处理,不会直接对内存的内容进行处理;(3)简单寻址方式,load/store地址来源于寄存器或指令域

- [实验室服务器使用]使用VSCode、PyCharm、MobaXterm和CMD连接远程服务器

YuanDaima2048

工具使用服务器vscodepycharmcmd代理模式机器学习实验

文章总览:YuanDaiMa2048博客文章总览实验室服务器使用:使用VSCode、PyCharm、MobaXterm和CMD连接远程服务器在进行实验室工作时,远程连接服务器是常见的需求之一。本篇文章根据个人的一些使用介绍使用不同工具连接服务器的方法,并提供优化功能,使服务器能够使用本机代理的说明。准备服务器账号信息Host(主机):10.XXX.XX.XXXPort(端口):[SSHPort]U

- HarmonyOS开发实战( Beta5.0)搜索框热搜词自动切换

让开,我要吃人了

OpenHarmonyHarmonyOS鸿蒙开发harmonyos华为鸿蒙移动开发鸿蒙系统前端开发语言

鸿蒙HarmonyOS开发往期必看:HarmonyOSNEXT应用开发性能实践总结最新版!“非常详细的”鸿蒙HarmonyOSNext应用开发学习路线!(从零基础入门到精通)介绍本示例介绍使用TextInput组件与Swiper组件实现搜索框内热搜词自动切换。效果图预览使用说明页面顶部搜索框内热搜词条自动切换,编辑搜索框时自动隐藏。实现思路使用TextInput实现搜索框TextInput({te

- HarmonyOS Next鸿蒙扫一扫功能实现

JohnLiu_

HarmonyOSNextharmonyos华为扫一扫鸿蒙

直接使用的是华为官方提供的api,封装成一个工具类方便调用。import{common}from'@kit.AbilityKit';import{scanBarcode,scanCore}from'@kit.ScanKit';exportnamespaceScanUtil{exportasyncfunctionstartScan(context:common.Context):Promise{if

- 鲲鹏 ARM 架构 麒麟 Lylin v10 安装 Nginx (离线)

焚木灵

arm开发架构nginx服务器

最近做一个银行的项目,银行的服务器是鲲鹏ARM架构的服务器,并且是麒麟v10的系统,这里记录一下在无法访问外网安装Nginx的方法。其他文章:鲲鹏ARM架构麒麟Lylinv10安装Mysql8.3(离线)-CSDN博客鲲鹏ARM架构麒麟Lylinv10安装Node和NVM(离线)-CSDN博客鲲鹏ARM架构麒麟Lylinv10安装Pm2(离线)-CSDN博客鲲鹏ARM架构麒麟Lylinv10安装P

- 【鸿蒙应用】总结一下ArkUI

读心悦

鸿蒙基础鸿蒙应用

ArkUI是HarmonyOS应用界面的UI开发框架,提供了简洁的UI语法、UI组件、动画机制和事件交互等等UI开发基础,以此满足应用开发者对UI界面开发的需求。组件是界面搭建的最小单位,开发者通过多种组件的组合构成完整的界面。页面是ArkUI最小的调度分隔单位,开发者可以将应用设计为多个功能页面,每一个页面进行单独的文件管理,并且通过页面路由API完成页面之间的调度管理,以此来实现应用内功能的解

- python环境安装 pip不能用的问题 pycharm的模板字符

卓越小Y

python学习pythonpycharmpip

学习初衷今天是九月一号,也就是开学日,做大人的也要适当开下学,享受下仪式感。以往都是存储在笔记本的,但是几台电脑,经常很多资料乱成一团,写成博客,方便让有心学习的朋友少走一些弯路。属于自己的开学季也出发了python环境安装和一些小问题环境搭建环境安装添加变量名为PYTHON_HOME地址:安装文件的路径path路径(%代表引用设置好的变量)一般我们会添加一个环境PYTHON_HOME然后指向我们

- 基于高通主板的ARM架构服务器

问就是想睡觉

arm开发服务器运维

一、ARM架构服务器的崛起(一)市场需求推动消费市场寒冬,全球消费电子需求下行,服务器成半导体核心动力之一。Arm加速布局服务器领域,如9月推出NeoverseV2。长久以来,x86架构主导服务器市场,现面临挑战。Arm2008年入服务器领域,虽因性能与生态问题未大突破,但近几年重新冲刺。(二)技术创新引领Arm的Neoverse平台不断发展。2018年推出参考架构,2020年衍生出E、N、V系列

- GEO数据的下载和处理|GEO数据转换为Gene symbol|GEO注释文件提取symbol|查看样本标签|查看GEO数据疾病或正常|生物信息基础

Red Red

生信小技巧学习笔记生物信息r语言GEO数据库数据库

GEO数据的下载和处理|GEO数据转换为Genesymbol|GEO注释文件提取symbol|查看样本标签|查看GEO数据疾病或正常|生物信息基础数据的下载和处理首先在GEO数据库中通过GSEID找到相关数据,然后下载txt文件。数据读取与处理。#设置工作路径,也就是你的分析数据存放以及要保存到地方setwd(dir="C:\\Users\\LiaoMinzhen\\PycharmProjects

- 【开发环境搭建】Macbook M1搭建Java开发环境

weixin_44329069

java开发语言

JDK安装与配置下载并安装JDK:ARM64DMG安装包下载链接:JDK21forMac(ARM64)。双击下载的DMG文件,按照提示安装JDK。配置环境变量:打开终端,使用vim编辑.bash_profile文件:vim~/.bash_profile在文件中添加以下内容来设置JAVA_HOME:exportJAVA_HOME=/Library/Java/JavaVirtualMachines/j

- 深入了解树莓派5:性能与功能的全面升级

像风一样自由2020

树莓派ubuntu

深入了解树莓派5:性能与功能的全面升级引言2023年,树莓派基金会正式发布了备受期待的树莓派5(RaspberryPi5)。作为树莓派系列的最新一代产品,树莓派5在处理性能、连接性和功能扩展方面都有了显著的提升,为开发者、教育者和科技爱好者带来了更强大的工具。本文将详细介绍树莓派5的特性、规格和应用场景。一、产品概述树莓派5是基于ARM架构的单板计算机,延续了树莓派系列低成本、高性能的设计理念。它

- 避免 PyCharm 将该 Python 脚本作为测试运行

MonkeyKing.sun

pythonpycharmide

为了避免PyCharm将该Python脚本作为测试运行(即pytest自动捕获),你可以做以下几步来确保该脚本作为普通的Python程序执行,而不是作为pytest运行。解决方案:1.确保文件名不以test_开头:Pytest会自动检测以test_开头的文件,并尝试将其作为测试运行。如果你的文件名是test_milvus.py,pytest会尝试收集并运行它。可以重命名文件为不包含test_的前缀

- PyCharm配置及使用Git教程_pycharm配置git(2)

2401_84182146

程序员pycharmgitelasticsearch

文章目录1.安装PyCharm2.安装Git3.在PyCharm中配置Git插件4.连接远程仓库5.Clone项目代码6.将本地文件提交到远程仓库6.1gitadd6.2gitcommit6.3gitpush6.4gitpull7.代码回滚8.分支操作8.1新建分支8.2切换分支8.3合并分支

- python做窗口软件界面绑定py程序_PyCharm GUI界面开发和exe文件生成的实现

weixin_39948442

一、安装Python二、安装PyQt5推荐使用pip安装:win+R调出cmd命令窗口pipinstallPyQt5等待片刻,继续安装PyQt5-toolspipinstallPyQt5-tools如果直接pip不成功的话,建议在python库这个网站上搜索相关库,下载相应的.whl文件,然后用以下方法进行安装:①pipwhl文件所在路径whl文件名②在cmd命令窗口先执行cdwhl文件所在路径到

- Kotlin 代替Java接口回调,就这么简单

深海呐

Android#Kotlinjavakotlin开发语言

假如你使用旧的接口回调:通常三步:1定义接口和方法;2使用接口中方法;3继承接口并实现方法;例:classXXXAdapter{publicvarmClickCollBack:clickCollBack?=null//1定义interfaceclickCollBack{//1定义funclick(int:Int)//1定义}itemView.setOnClickListener{mClickCol

- python基于django/flask的NBA球员大数据分析与可视化python+java+node.js

QQ_511008285

pythondjangoflaskjavaspringboot数据分析

前端开发框架:vue.js数据库mysql版本不限后端语言框架支持:1java(SSM/springboot)-idea/eclipse2.Nodejs+Vue.js-vscode3.python(flask/django)--pycharm/vscode4.php(thinkphp/laravel)-hbuilderx数据库工具:Navicat/SQLyog等都可以本文针对NBA球员的大数据进行

- Java基于spring boot的国产电影数据分析与可视化python+java+node.js

QQ_511008285

javaspringboot数据分析pythondjangovue.jsflask

前端开发框架:vue.js数据库mysql版本不限后端语言框架支持:1java(SSM/springboot)-idea/eclipse2.Nodejs+Vue.js-vscode3.python(flask/django)--pycharm/vscode4.php(thinkphp/laravel)-hbuilderx数据库工具:Navicat/SQLyog等都可以 该系统使用进行大数据处理和

- pycharm 运行celery_python远程调试及celery调试

夏小龙

pycharm运行celery

部分来自from:https://www.xncoding.com/2016/05/26/python/pycharm-remote.html你是否经常要在Windows7或MACOSX上面开发Python或Web应用程序,但是它们最后需要在linux上面来运行呢?我们经常会碰到开发时没有问题但是到了正式的Linux环境下面却出现问题。那么怎样保证开发环境跟运行环境的一致呢?通常有两种方法解决。一

- [HarmonyOS Next示例代码] 鸿蒙UI开发 - 组件动态创建

xiaohai_09

HarmonyOSNextUI开发harmonyos鸿蒙

鸿蒙UI开发-组件动态创建源码下载地址介绍本示例介绍了在声明式UI中实现组件动态创建的方法效果图预览主页面广告关闭弹窗使用说明进入应用后,广告组件随即被动态创建。其分为两种,分别为图片广告与视频广告。实现思路构建广告组件。源码参考AdBuilder.ets。模拟从云端初始化卡片列表,根据云端数据生成普通卡片对象和广告卡片对象。源码参考代码可参考MainPage.ets中的aboutToAppear

- 对股票分析时要注意哪些主要因素?

会飞的奇葩猪

股票 分析 云掌股吧

众所周知,对散户投资者来说,股票技术分析是应战股市的核心武器,想学好股票的技术分析一定要知道哪些是重点学习的,其实非常简单,我们只要记住三个要素:成交量、价格趋势、振荡指标。

一、成交量

大盘的成交量状态。成交量大说明市场的获利机会较多,成交量小说明市场的获利机会较少。当沪市的成交量超过150亿时是强市市场状态,运用技术找综合买点较准;

- 【Scala十八】视图界定与上下文界定

bit1129

scala

Context Bound,上下文界定,是Scala为隐式参数引入的一种语法糖,使得隐式转换的编码更加简洁。

隐式参数

首先引入一个泛型函数max,用于取a和b的最大值

def max[T](a: T, b: T) = {

if (a > b) a else b

}

因为T是未知类型,只有运行时才会代入真正的类型,因此调用a >

- C语言的分支——Object-C程序设计阅读有感

darkblue086

applec框架cocoa

自从1972年贝尔实验室Dennis Ritchie开发了C语言,C语言已经有了很多版本和实现,从Borland到microsoft还是GNU、Apple都提供了不同时代的多种选择,我们知道C语言是基于Thompson开发的B语言的,Object-C是以SmallTalk-80为基础的。和C++不同的是,Object C并不是C的超集,因为有很多特性与C是不同的。

Object-C程序设计这本书

- 去除浏览器对表单值的记忆

周凡杨

html记忆autocompleteform浏览

&n

- java的树形通讯录

g21121

java

最近用到企业通讯录,虽然以前也开发过,但是用的是jsf,拼成的树形,及其笨重和难维护。后来就想到直接生成json格式字符串,页面上也好展现。

// 首先取出每个部门的联系人

for (int i = 0; i < depList.size(); i++) {

List<Contacts> list = getContactList(depList.get(i

- Nginx安装部署

510888780

nginxlinux

Nginx ("engine x") 是一个高性能的 HTTP 和 反向代理 服务器,也是一个 IMAP/POP3/SMTP 代理服务器。 Nginx 是由 Igor Sysoev 为俄罗斯访问量第二的 Rambler.ru 站点开发的,第一个公开版本0.1.0发布于2004年10月4日。其将源代码以类BSD许可证的形式发布,因它的稳定性、丰富的功能集、示例配置文件和低系统资源

- java servelet异步处理请求

墙头上一根草

java异步返回servlet

servlet3.0以后支持异步处理请求,具体是使用AsyncContext ,包装httpservletRequest以及httpservletResponse具有异步的功能,

final AsyncContext ac = request.startAsync(request, response);

ac.s

- 我的spring学习笔记8-Spring中Bean的实例化

aijuans

Spring 3

在Spring中要实例化一个Bean有几种方法:

1、最常用的(普通方法)

<bean id="myBean" class="www.6e6.org.MyBean" />

使用这样方法,按Spring就会使用Bean的默认构造方法,也就是把没有参数的构造方法来建立Bean实例。

(有构造方法的下个文细说)

2、还

- 为Mysql创建最优的索引

annan211

mysql索引

索引对于良好的性能非常关键,尤其是当数据规模越来越大的时候,索引的对性能的影响越发重要。

索引经常会被误解甚至忽略,而且经常被糟糕的设计。

索引优化应该是对查询性能优化最有效的手段了,索引能够轻易将查询性能提高几个数量级,最优的索引会比

较好的索引性能要好2个数量级。

1 索引的类型

(1) B-Tree

不出意外,这里提到的索引都是指 B-

- 日期函数

百合不是茶

oraclesql日期函数查询

ORACLE日期时间函数大全

TO_DATE格式(以时间:2007-11-02 13:45:25为例)

Year:

yy two digits 两位年 显示值:07

yyy three digits 三位年 显示值:007

- 线程优先级

bijian1013

javathread多线程java多线程

多线程运行时需要定义线程运行的先后顺序。

线程优先级是用数字表示,数字越大线程优先级越高,取值在1到10,默认优先级为5。

实例:

package com.bijian.study;

/**

* 因为在代码段当中把线程B的优先级设置高于线程A,所以运行结果先执行线程B的run()方法后再执行线程A的run()方法

* 但在实际中,JAVA的优先级不准,强烈不建议用此方法来控制执

- 适配器模式和代理模式的区别

bijian1013

java设计模式

一.简介 适配器模式:适配器模式(英语:adapter pattern)有时候也称包装样式或者包装。将一个类的接口转接成用户所期待的。一个适配使得因接口不兼容而不能在一起工作的类工作在一起,做法是将类别自己的接口包裹在一个已存在的类中。 &nbs

- 【持久化框架MyBatis3三】MyBatis3 SQL映射配置文件

bit1129

Mybatis3

SQL映射配置文件一方面类似于Hibernate的映射配置文件,通过定义实体与关系表的列之间的对应关系。另一方面使用<select>,<insert>,<delete>,<update>元素定义增删改查的SQL语句,

这些元素包含三方面内容

1. 要执行的SQL语句

2. SQL语句的入参,比如查询条件

3. SQL语句的返回结果

- oracle大数据表复制备份个人经验

bitcarter

oracle大表备份大表数据复制

前提:

数据库仓库A(就拿oracle11g为例)中有两个用户user1和user2,现在有user1中有表ldm_table1,且表ldm_table1有数据5千万以上,ldm_table1中的数据是从其他库B(数据源)中抽取过来的,前期业务理解不够或者需求有变,数据有变动需要重新从B中抽取数据到A库表ldm_table1中。

- HTTP加速器varnish安装小记

ronin47

http varnish 加速

上午共享的那个varnish安装手册,个人看了下,有点不知所云,好吧~看来还是先安装玩玩!

苦逼公司服务器没法连外网,不能用什么wget或yum命令直接下载安装,每每看到别人博客贴出的在线安装代码时,总有一股羡慕嫉妒“恨”冒了出来。。。好吧,既然没法上外网,那只能麻烦点通过下载源码来编译安装了!

Varnish 3.0.4下载地址: http://repo.varnish-cache.org/

- java-73-输入一个字符串,输出该字符串中对称的子字符串的最大长度

bylijinnan

java

public class LongestSymmtricalLength {

/*

* Q75题目:输入一个字符串,输出该字符串中对称的子字符串的最大长度。

* 比如输入字符串“google”,由于该字符串里最长的对称子字符串是“goog”,因此输出4。

*/

public static void main(String[] args) {

Str

- 学习编程的一点感想

Cb123456

编程感想Gis

写点感想,总结一些,也顺便激励一些自己.现在就是复习阶段,也做做项目.

本专业是GIS专业,当初觉得本专业太水,靠这个会活不下去的,所以就报了培训班。学习的时候,进入状态很慢,而且当初进去的时候,已经上到Java高级阶段了,所以.....,呵呵,之后有点感觉了,不过,还是不好好写代码,还眼高手低的,有

- [能源与安全]美国与中国

comsci

能源

现在有一个局面:地球上的石油只剩下N桶,这些油只够让中国和美国这两个国家中的一个顺利过渡到宇宙时代,但是如果这两个国家为争夺这些石油而发生战争,其结果是两个国家都无法平稳过渡到宇宙时代。。。。而且在战争中,剩下的石油也会被快速消耗在战争中,结果是两败俱伤。。。

在这个大

- SEMI-JOIN执行计划突然变成HASH JOIN了 的原因分析

cwqcwqmax9

oracle

甲说:

A B两个表总数据量都很大,在百万以上。

idx1 idx2字段表示是索引字段

A B 两表上都有

col1字段表示普通字段

select xxx from A

where A.idx1 between mmm and nnn

and exists (select 1 from B where B.idx2 =

- SpringMVC-ajax返回值乱码解决方案

dashuaifu

AjaxspringMVCresponse中文乱码

SpringMVC-ajax返回值乱码解决方案

一:(自己总结,测试过可行)

ajax返回如果含有中文汉字,则使用:(如下例:)

@RequestMapping(value="/xxx.do") public @ResponseBody void getPunishReasonB

- Linux系统中查看日志的常用命令

dcj3sjt126com

OS

因为在日常的工作中,出问题的时候查看日志是每个管理员的习惯,作为初学者,为了以后的需要,我今天将下面这些查看命令共享给各位

cat

tail -f

日 志 文 件 说 明

/var/log/message 系统启动后的信息和错误日志,是Red Hat Linux中最常用的日志之一

/var/log/secure 与安全相关的日志信息

/var/log/maillog 与邮件相关的日志信

- [应用结构]应用

dcj3sjt126com

PHPyii2

应用主体

应用主体是管理 Yii 应用系统整体结构和生命周期的对象。 每个Yii应用系统只能包含一个应用主体,应用主体在 入口脚本中创建并能通过表达式 \Yii::$app 全局范围内访问。

补充: 当我们说"一个应用",它可能是一个应用主体对象,也可能是一个应用系统,是根据上下文来决定[译:中文为避免歧义,Application翻译为应

- assertThat用法

eksliang

JUnitassertThat

junit4.0 assertThat用法

一般匹配符1、assertThat( testedNumber, allOf( greaterThan(8), lessThan(16) ) );

注释: allOf匹配符表明如果接下来的所有条件必须都成立测试才通过,相当于“与”(&&)

2、assertThat( testedNumber, anyOf( g

- android点滴2

gundumw100

应用服务器android网络应用OSHTC

如何让Drawable绕着中心旋转?

Animation a = new RotateAnimation(0.0f, 360.0f,

Animation.RELATIVE_TO_SELF, 0.5f, Animation.RELATIVE_TO_SELF,0.5f);

a.setRepeatCount(-1);

a.setDuration(1000);

如何控制Andro

- 超简洁的CSS下拉菜单

ini

htmlWeb工作html5css

效果体验:http://hovertree.com/texiao/css/3.htmHTML文件:

<!DOCTYPE html>

<html xmlns="http://www.w3.org/1999/xhtml">

<head>

<title>简洁的HTML+CSS下拉菜单-HoverTree</title>

- kafka consumer防止数据丢失

kane_xie

kafkaoffset commit

kafka最初是被LinkedIn设计用来处理log的分布式消息系统,因此它的着眼点不在数据的安全性(log偶尔丢几条无所谓),换句话说kafka并不能完全保证数据不丢失。

尽管kafka官网声称能够保证at-least-once,但如果consumer进程数小于partition_num,这个结论不一定成立。

考虑这样一个case,partiton_num=2

- @Repository、@Service、@Controller 和 @Component

mhtbbx

DAOspringbeanprototype

@Repository、@Service、@Controller 和 @Component 将类标识为Bean

Spring 自 2.0 版本开始,陆续引入了一些注解用于简化 Spring 的开发。@Repository注解便属于最先引入的一批,它用于将数据访问层 (DAO 层 ) 的类标识为 Spring Bean。具体只需将该注解标注在 DAO类上即可。同时,为了让 Spring 能够扫描类

- java 多线程高并发读写控制 误区

qifeifei

java thread

先看一下下面的错误代码,对写加了synchronized控制,保证了写的安全,但是问题在哪里呢?

public class testTh7 {

private String data;

public String read(){

System.out.println(Thread.currentThread().getName() + "read data "

- mongodb replica set(副本集)设置步骤

tcrct

javamongodb

网上已经有一大堆的设置步骤的了,根据我遇到的问题,整理一下,如下:

首先先去下载一个mongodb最新版,目前最新版应该是2.6

cd /usr/local/bin

wget http://fastdl.mongodb.org/linux/mongodb-linux-x86_64-2.6.0.tgz

tar -zxvf mongodb-linux-x86_64-2.6.0.t

- rust学习笔记

wudixiaotie

学习笔记

1.rust里绑定变量是let,默认绑定了的变量是不可更改的,所以如果想让变量可变就要加上mut。

let x = 1; let mut y = 2;

2.match 相当于erlang中的case,但是case的每一项后都是分号,但是rust的match却是逗号。

3.match 的每一项最后都要加逗号,但是最后一项不加也不会报错,所有结尾加逗号的用法都是类似。

4.每个语句结尾都要加分