如何在FPGA的QSYS里面加入sram ip,当运行内存来用

如何在FPGA的QSYS里面加入sram ip,当运行内存来用

第一次在CSDN发文,有问题的地方请大家指出。

先讲一下自己接触FPGA的历史吧

大学的时候有过这门专业课,但是那学校普及的一直是VHDL语言,这对刚接触这行的人很不好,所以那个时候对FPGA没有提起太大的兴趣,只是大概知道是用来配置各种硬件电路的东西,后来工作了,我之前所在的是手机显示触摸屏行业,由于分辨率提高,之前的三星S3C6410 ARM平台已经慢慢没法满足对产品的测试需求了,听同事说和这个S3C6410核心板停产也有关系,14年的时候我们公司开始大规模引进FPGA核心板来实现lcd的调试和量产测试工作,就是从那时候起重新和FPGA再度相遇了。才发现FPGA可以这么实用和强大,慢慢想做深入学习,那时候从同事那里知道还有veirlog语言也可以写FPGA逻辑,而且和C有点类似,不再像VHDL那么晦涩难以接受了,学起来还挺快的但是也就是写一些比较简单的分频,uart什么的,然后用modelsim仿真一下就完了,就这么玩了一段时间,刚学的时候不知道有qsys这个东西啊,quartus11以前的版本好像叫SOPC我记得是。

由于FPGA平台对我们调试lcd只是一个工具,大部分工作都是在NIOSii系统里面完成,就跟嵌入式开发没有什么区别了,所以也很少去深究它硬件配置电路到底是怎么工作的,后来需要用IIC来和触摸屏通信做测试,就接触到了IIC的IP核部分,这个IIC的IP核我听说是公司的人员要来板子的FPGA工程自己加的,当时给我们更新的工程代码里面只有非常简单的IIC操作指令,由于之前没有接触过这个,所以很好奇,根据里面的备注和自己的理解完善了IIC指令并且去验证是OK的,但是 那个时候还不明白为什么给IIC_BASE地固定偏移地址写一个数电路就会执行相应操作,去问了比较懂FPGA的同事,告诉我这就是IP核,就和ARM里面的寄存器地址映射一样。

大概明白了,但是没有深究这个问题,真正让我对FPGA感兴趣并且决定深入学习是因为同事电脑里面的一本PDF书,我跟他聊天时候无意间看到了,是关于FPGA的就打开看了一会,然后就无法自拔了这本书的名字叫《从零开始走进FPGA世界_V2.1》是一本引人入胜的书,大学想学FPGA的同学可以去网上下载来看看,非常不错,通过这本书我又知道了特权同学,然后也找了他的《深入浅出玩转fpga》来看,便开始了对FPGA的深入学习。

我一直知道公司那一套系统的IIC IP核的大概结构,所以想着自己写一个出来,到qsys里面验证一下,通过网上找资料后来差不多写出来了,仿真也没有问题,后来买了特权的开发板来调试OK了,这个板子没有SDRAM,所以qsys系统运行用的是片上ram,可是板子上有一个32K的SRAM,我想着用这个来当做FPGA的运行内存,但是quartus13没有sram的现成的IP核,我又一次没有了头绪,去网上搜到了Crazy bingo的博客里面以前写过这个IP核,但是那个时候还是SOPC的年代,所以他们也是基于SOPC系统加的,大家可以去这里看看原文

https://www.cnblogs.com/crazybingo/archive/2011/02/27/1966552.html

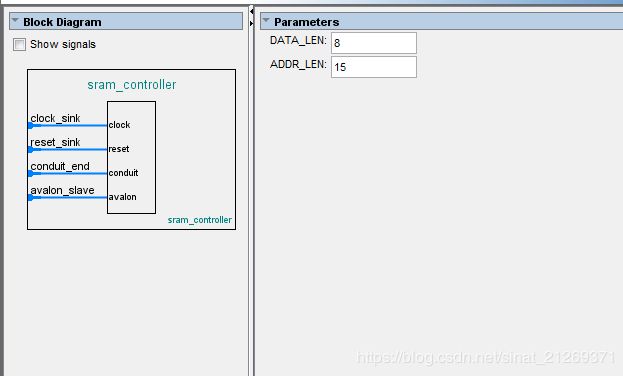

我的sram没有数据位屏蔽信号,所以可以将coe_SRAM_LB_N, 和coe_SRAM_UB_N,去掉,或者不给接口例化,代码如下:

module sram_controller

#(

parameter DATA_LEN=16,

parameter ADDR_LEN=15

)

(avs_clk,avs_rst_n,

avs_add,avs_byteen_n,

avs_wren_n,avs_wrdata,

avs_rden_n,avs_rddata,

////sram

coe_SRAM_DQ, // SRAM Data bus

coe_SRAM_ADDR, // SRAM Address bus

coe_SRAM_LB_N, // SRAM Low-byte Data Mask

coe_SRAM_UB_N, // SRAM High-byte Data Mask

coe_SRAM_CE_N, // SRAM Chip chipselect

coe_SRAM_OE_N, // SRAM Output chipselect

coe_SRAM_WE_N // SRAM Write chipselect

);

input avs_clk,avs_rst_n;

input [ADDR_LEN-1:0]avs_add;

input [(DATA_LEN/8-1):0] avs_byteen_n;

input avs_wren_n,avs_rden_n;

input [DATA_LEN-1:0]avs_wrdata;

output[DATA_LEN-1:0]avs_rddata;

inout [DATA_LEN-1:0]coe_SRAM_DQ;

output [ADDR_LEN-1:0]coe_SRAM_ADDR;

output coe_SRAM_LB_N,coe_SRAM_UB_N,coe_SRAM_CE_N,coe_SRAM_OE_N,coe_SRAM_WE_N;

assign coe_SRAM_CE_N=avs_wren_n&&avs_rden_n;

assign coe_SRAM_OE_N=avs_rden_n;

assign coe_SRAM_WE_N=avs_wren_n;

assign coe_SRAM_ADDR=avs_add;

assign coe_SRAM_DQ=avs_wren_n?'hz:avs_wrdata;

assign avs_rddata=coe_SRAM_DQ;

assign {coe_SRAM_UB_N, coe_SRAM_LB_N} = avs_byteen_n;

endmodule

大家可以看下其实和在avalon总线上挂IP是一样的,

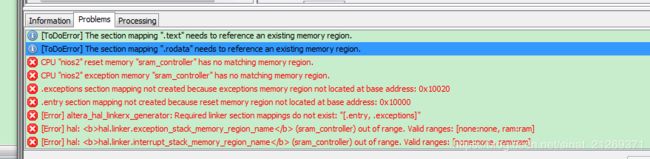

加入到qsys编译没有问题, 但是到Niosii里面就报错,

跑到Crazy bingo的那篇博客里面找原因,发现少设置了一步,

他强调这里一定要选Memory device,但是我在qsys的IP interface那里怎么也找不到这个选项,很纳闷,后来点开了assignment 的edit

这里面的4个默认都是0,也就是没有默认配置的意思,大家可以看看第二项,我觉得就是bingo强调的那个问题,配置为1,编译运行,到niosii里面就OK了,板子可以正常运行

到这里就算实现目标了

可是我还是有一个疑问,niosii处理器是32位的,我的sram的数据位是8bits,处理器难道是检测到我的数据位,然后每次读取一个byte来操作sram当内存么?希望知道的朋友留言探讨一下。