FPGA板级调试方法与原则

FPGA调试借助于示波器和逻辑分析仪是最常见的方法。

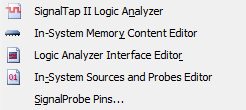

本文列举Quartus II支持的五种较实用的调试方法。

当然还有一些虚拟JTAG调试和LogicLock逻辑锁定等调试方法。

1.信号探针(signalProbe)法:

信号探针方式是不影响原有设计功能和布局布线,只是通过增加额外布线将需要观察调试的信号连接到预先保留或暂时不使用的I/O接口,该方式相应得到的信号电平会随布线有一定的延时,不适合于高速,大容量信号观察调试,也不适合做板级时序分析。

它的优势在于不影响原有设计,额外资源消耗为零,调试中也不需要保持连接JTAG等其他线缆,能够最小化编译或重编译的时间。

这种信号探针法(signalProbe)使用条件有:

1.首先得有多余的I/O管脚;

2.器件是FPGA或CPLD芯片;

3.必须要有外部测试设备,比如逻辑分析仪,示波器。(需要外部设备来观察会导致信号具备一定的时延和不完整性,个人不常用)

具体操作参考博文地址:

https://blog.csdn.net/huan09900990/article/details/78908748

2.在线逻辑分析仪(signalTap II)

SignalTap II在线逻辑分析仪很大程度上可以替代昂贵的逻辑分析仪,为开发节约成本,同时也为调试者省去了原本繁琐的连线工作,而有些板级连接的外部设备很难观察到的信号都能够轻松捕获。如果对设计进行模块的区域约束,也能够使在线逻辑分析仪对设计带来的影响最小化。在线逻辑分析仪的采样存储深度和宽度都在一定程度上受限于FPGA器件资源的大小。

使用该方式必须通过JTAG接口,它的采样频率可以达到200MHZ(若器件支持)以上,不用像外部调试设备一样担心信号的完整性问题。

具体操作参考博文地址:

https://blog.csdn.net/woshiyuzhoushizhe/article/details/83007026

推荐使用在线逻辑分析仪(signalTap II)

3.逻辑分析仪接口(Logic Analyzer Interface )法

这里的逻辑分析仪接口是针对具有外部逻辑分析仪的。调试者可以设置FPGA器件内部的多个信号映射到一个预留或暂时不用的I/O口上,从而通过较少的I/O口就能够观察到FPGA多组内部信号。

该法与第一种信号探针法类似,因此具备信号探针法的缺点,个人不常用。

4.在线存储内容编辑法(In-System Memory Content Editor)

在线存储内容编辑是针对设计中例化的内嵌存储器内容或常量的调试。可以通过这种方式在线重写或者读出工程中内嵌存储器内容或常量。对于某些应用可以通过在线更改存储器内容后观察响应来验证设计,也可以在不同激励下在线读取当前存储内容来验证设计。总之,这种方法对存储器的验证具有很大帮助。

但是首先很遗憾,目前该功能只支持单口RAM以及ROM,不支持双口RAM。

具体操作参考博文地址:

https://blog.csdn.net/huan09900990/article/details/78890356

5.在线源和探针法(In-System Sources and Probes)

这种方法是通过例化一个定制的寄存器链到FPGA器件内部,这些寄存器链通过JTAG接口与器件通信,能够驱动器件内部的某些输入节点信号,采样某些输出节点信号,这就使得调试者不需要借助外部设备就能够给FPGA添加激励并观察响应。

具体操作参考博文地址:

https://blog.csdn.net/huan09900990/article/details/78893435

对于FPGA调试而言,

(1)设计前,首先就要选择好片上调试方案,并规划好存储器和逻辑要求,确定I/O引脚连接和电路板连接方式。

(2)对于使用器件自带的如SignalTap II这一类嵌入式逻辑分析仪进行调试时,需要保留一定的内部存储器资源,以便大量存储采集数据。

(3)如果要使用嵌入式逻辑分析仪,逻辑分析接口,在线存储器内容编辑和虚拟JTAG宏功能,就需要在系统和电路板的规划中专门设计对应的JTAG接口。

(4)要逐渐使用调试工具,减少编译时间,开启渐进式编译。这样就不必重新编译设计来更改调试工具。

(5)确保电路板能支持调试模式,在此模式下调试信号不影响系统运行。

(6)保留I/O引脚,以便于通过逻辑分析仪接口或者额外的信号引脚进行调试。这样就不必在以后为了适应调试信号而更改设计或者电路板。