本编文章的目的主要用简明的方法在纯PS里对DDR3进行读写。

本文所使用的开发板是Miz701

PC 开发环境版本:Vivado 2015.4 Xilinx SDK 2015.4

10.0本章难度系数★☆☆☆☆☆☆

10.1 搭建硬件工程

Step1:新建一个名为为Miz701_sys的工程

Step2:选择RTL Project 勾选Do not specify source at this time

Step3:选择xc7z010clg400-1为开发器件。

Step4:单击Finish

10.2使用IP Integrator创建硬件系统

Step1:单击Create Block Design

Step2:输入system

Step4:搜素单词z选择ZYNQ7 Processing System,然后双击

Step5:添加进来了ZYNQ CPU IP,双击对其进行配置。

Step6:修改输入时钟为50MHZ,PL端频率FCLK_CLK0为100MHZ。

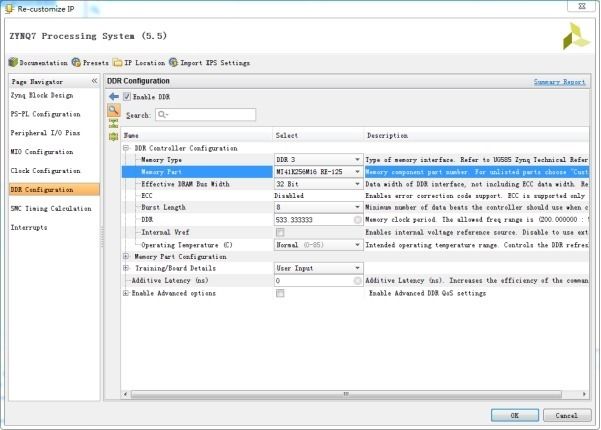

Step7:修改内存类型为MT41K256M16 RE-125。

Step8:在MIO configuration选项中,勾选添加UART1接口,单击OK完成修改。

Step9:单击Run Block Automation

Step10:直接单击OK

Step11:在你点击了OK后,你会发现DDR以及FICED_IO自动的延伸出来。

Step12:连线的作用就是把PS的时钟可以接入PL部分,当然这里我们暂时用不到PL部分的资源。在Block文件中,我们迚行连线,将鼠标放在引脚处,鼠标变成铅笔后迚行拖拽,连线如下图所示:

Step13: 右击 system.bd, 单击Generate Output Products

Step14:支部操作会产生执行、仿真、综合的文件

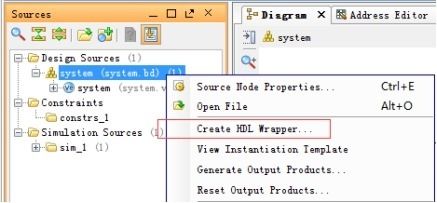

Step15:右击system.bd 选择 Create HDL Wrapper 这步的作用是产生顶层的HDL文件

Step16:选择Leave Let Vivado manager wrapper and auto-update 然后单击OK

10.3导出SOC硬件到SDK

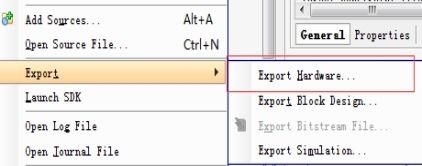

Step1:File->Export->Export Hardware

Step2:勾选Include bitstream 直接单击OK

Step3:File->Launch SDK加载到SDK

Step4:单击OK

10.4软件工程

新建一个miz701_ps_ddr空的工程,并且添加main.c

DDR3的地址建好后,在mem_demo_bsp->ps7->cortexa9_0的路径下,打开xparameters_ps.h这个头文件,这个头文件是cortexA9可以直接控制的外设地址的宏定义。在里面可以找到DDR的地址,可以看到如下代码:

| /* Canonical definitions for DDR MEMORY */ |

等会我们要使用这个地址,对DDR3进行读写操作,读写操作函数在mem_demo_bsp->ps7->cortexa9_0的路径下,打开xil_io.h这个头文件,这个头文件是cortexA9可以直接控制的内存映射或者映射到了地址空间的IO。在里面可以看到如下代码:

//从某个地址读数据

u8 Xil_In8(INTPTR Addr);

u16 Xil_In16(INTPTR Addr);

u32 Xil_In32(INTPTR Addr);

//向某个地址写数据。

void Xil_Out8(INTPTR Addr, u8 Value);

void Xil_Out16(INTPTR Addr, u16 Value);

void Xil_Out32(INTPTR Addr, u32 Value);

OK,有了这些就可以简单的对DDR进行续写操作了

10.4代码实现

| /* * main.c * * Created on: 2016年4月4日 * Author: Administrator */ #include "stdio.h" #include "xparameters.h" #include "xparameters_ps.h" #include "xil_printf.h" #include "xil_io.h" #define DDR_BASEARDDR XPAR_DDR_MEM_BASEADDR + 0x10000000 int main() { int i; int rev; xil_printf("Hello World\n\r"); for(i=0; i<32; i++) { Xil_Out32(DDR_BASEARDDR+i*4,i); } for(i=0; i<32; i++) { rev = Xil_In32(DDR_BASEARDDR+i*4); xil_printf("the address at %x data is : %x \n\r" ,DDR_BASEARDDR+i*4, rev); } return 0; } |

10.5 测试结果

串口终端的结果如下:

Hello World

the address at 10000000 data is : 0

the address at 10000004 data is : 1

the address at 10000008 data is : 2

the address at 1000000C data is : 3

the address at 10000010 data is : 4

the address at 10000014 data is : 5

the address at 10000018 data is : 6

the address at 1000001C data is : 7

the address at 10000020 data is : 8

the address at 10000024 data is : 9

the address at 10000028 data is : A

the address at 1000002C data is : B

the address at 10000030 data is : C

the address at 10000034 data is : D

the address at 10000038 data is : E

the address at 1000003C data is : F

the address at 10000040 data is : 10

the address at 10000044 data is : 11

the address at 10000048 data is : 12

the address at 1000004C data is : 13

the address at 10000050 data is : 14

the address at 10000054 data is : 15

the address at 10000058 data is : 16

the address at 1000005C data is : 17

the address at 10000060 data is : 18

the address at 10000064 data is : 19

the address at 10000068 data is : 1A

the address at 1000006C data is : 1B

the address at 10000070 data is : 1C

the address at 10000074 data is : 1D

the address at 10000078 data is : 1E

the address at 1000007C data is : 1F

....................

10.6 本章小结

通过本章的学习,在仅仅使用PS可以对DDR3读写,这样在处理一些速度不快但是量很大的数据时很方便,当然这种方式每次读写都需要CPU干预,效率是比较低的,主要看需求吧。

淘宝店铺:https://osrc.taobao.com

官网论坛:www.osrc.cn

源码链接:http://pan.baidu.com/s/1kVM12n1 密码:rknx