SCCB(OmniVision serial camera control bus),即串行摄像机控制总线。OmniVision 公司已经定义和

采纳的SCCB总线是一种三线结构的串行总线,用于完成对绝大多数OmniVision 系列图像传芯片功能的控制。

在简化的引脚封装中,SCCB总线可以工作在改进的两线工作方式下。

两线SCCB接口有两条通迅连接线,即SIO_D(数据线)和 SIO_C(时钟线),下面是双总线功能原理图:

在双总线情况下,要求主控机有以下两种功能之一来支持SCCB通迅:

1、主控器件支持并能保持数据在三态模式;

2、如果不支持三态,

二、管脚功能

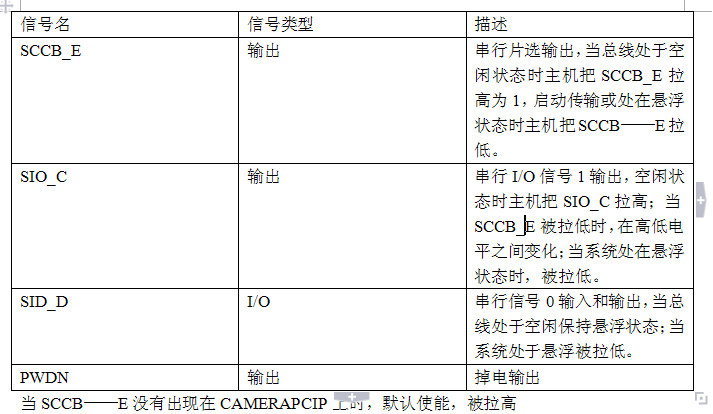

主控器件管脚描述

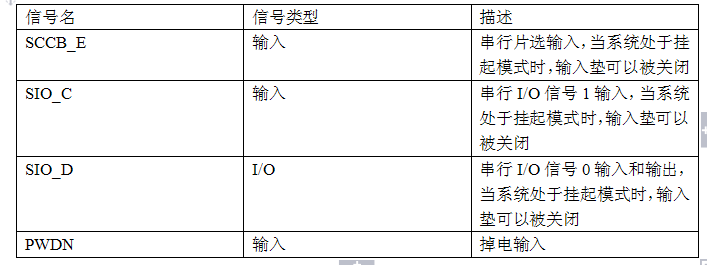

从控器件管脚描述

SCCB——E 信号

低电平有效,一个高到低的转换表明数据传输开始;一个低到高的转换表明数据传输结束;数据传输过程保持为低

电平;高电平表明总线处于空闲状态。在SCCB——E表明数据传输开始之前主机必须将数据线SIO——D置为1,这样可以避免

总线数据传输开始之前的总线不确定状态的出现。

SIO——C 信号

高电平有效,当处于空闲状态时必须被拉高;当启动传输后,SIO——C被拉低表明数据传输的开始,传输过程中高电平

表明一位数据正在传输,所以SIO——D的数据变化只能在SIO——C为低时发生,一位传输时间定义为tCYC,最小为10us。

三总线数据传输

SIO——D信号

可以被主机和从机驱动,当总线处于空闲时保持悬浮或三态;

在传输Don‘t-Car()e或NA位时,总线浮动和争用是允许的

SIO——C的一个高电平表明一位数据的传输,SIO——D只能在SIO——C的低电平期间发生变化,但在传输的开始和结束

也有例外,在SCCB——E断言并且SIO——C拉低之前,SIO——D可以被拉低,在SIO——C拉高之前和去断言之前,SIO——D

也可以被拉低。

数据传输的起始

SCCB——E由高到低的变化,表明数据传输的开始,在SCCB——E断言之前,主机必须把SIO——D拉高,这样可以避免

在数据传输之前传输一个不确定的总线状态;在SCCB——E去断言之后,主机必须把SIO——D拉高在一个定义的时间段

内,来再次避免一个不确定状态的总线状态传输。

在启动传输过程中有两个时间参数,TPRA和TPRC,TPRC被定义为SID——D预充电时间,这表明SIO——D必须先于

SCCB——E被拉高的时间,最小值为15ns,TPRA被是指在SIO——D拉低之前,SID——E必须被断言的时间,最小为1.25us。

数据传输的终止

TPSC是SCCB——E去断言后,SIO——D保持逻辑高电平的时间,最小为15ns,TPSA

是SIO——D去断言后,SCCB——E必须保持低电平的时间,最小为0ns。

传输阶段

SCCB读数据的Verilog实现

`START1 : begin

//Rd_Data <= 8'h0;

if( Shift_Start == 1 )

I2C_Start( Start_Buf);

else begin

if( Scl_r == 1'b1) begin

Scl_Ctrl <= 1'b1;

M_State <= `WR_ID1;

Shift_Start <= 1'b1;

// Scl_Ctrl <= 1'b0;

end

else M_State <= `START1;

end

end

`WR_ID1 : begin

if( Shift_Start == 1'b1 )

Shift8_Out( WR_id );

else begin

Shift_Start <= 1'b1;

M_State <= `WR_SB_AR1;

end

end

`WR_SB_AR1 : begin

if( Shift_Start == 1'b1 )

Shift8_Out ( 8'h11 );

else begin

Shift_Start <= 1'b1;

M_State <= `END2;

end

end

`END2 : begin

if( Scl_r == 1'b1 )

Scl_Ctrl <= 1'b0;

else if( Shift_Start == 1'b1)

I2C_End( End_Buf);

else begin

M_State <= `IDLE2;

// Shift_Start <= 1'b1;

end

end

`IDLE2 : begin

Scl_Ctrl <= 1'b0;//Scl 设置为高电平

Sda_io_Flag <= 1'b0;//Sda 设置为高阻

Sda_Reg <= 1'b1;

M_State <= `START2;

Shift_Start <= 1'b1;

end

`START2 : begin

// Rd_Data <= 8'h0;

if( Shift_Start == 1 )

I2C_Start( Start_Buf);

else begin

if( Scl_r == 1'b1) begin

Scl_Ctrl <= 1'b1;

M_State <= `RD_ID;

Shift_Start <= 1'b1;

// Scl_Ctrl <= 1'b0;

end

else M_State <= `START2;

end

end

`RD_ID : begin

if( Shift_Start == 1'b1)

Shift8_Out ( RD_id );

else begin

Shift_Start <= 1'b1;

M_State <= `RD_DATA;

// Sda_io_Flag <= 1'b1;

end

end

`RD_DATA : begin

if( Shift_Start == 1'b1 ) begin

Shift8_in( Rd_Data );

Sda_io_Flag <= 1'b1;

end

else begin

Sda_io_Flag <= 1'b0;

if( Scl_r == 1'b1 ) begin

M_State <= `END1;

Shift_Start <= 1'b1;

end

end

end

`END1 : begin

if( Scl_r == 1'b1 )

Scl_Ctrl <= 1'b0;

else if( Shift_Start == 1'b1)

I2C_End( End_Buf);

else begin

M_State <= `IDLE1;

// Shift_Start <= 1'b1;

end

end

`IDLE1 : begin

Scl_Ctrl <= 1'b0;//Scl 设置为高电平

Sda_io_Flag <= 1'b0;//Sda 设置为高阻

Sda_Reg <= 1'b1;

M_State <= `START1;

Shift_Start <= 1'b1;

end