实验所用板子为altera DE2板子,FPGA为Cyclone II:EP2C35F672C6,quartus版本为13.0

1.管脚信息

[11:0]DRAM_ADDR : address

DRAM_BA_0 : bank address 0

DRAM_BA_1 : bank address 1

DRAM_CAS_N : column address strobe

DRAM_CKE : clock enable

DRAM_CLK : clock

DRAM_CS_N : chip select

[15:0]DRAM_DQ : Data

DRAM_LDQM :lower byte data mask

DRAM_UDQM : upper byte data mask

DRAM_RAS_N : row address strobe

DRAM_WE_N : write enable

2.实验流程

1)建立工程

2)建立初始顶层文件

module work (

CLOCK_50, // On Board 50 MHz

KEY, // Pushbutton[3:0]

SW, // Toggle Switch[17:0]

LEDR, // LED Red[17:0]

DRAM_DQ, // SDRAM Data bus 16 Bits

DRAM_ADDR, // SDRAM Address bus 12 Bits

DRAM_LDQM, // SDRAM Low-byte Data Mask

DRAM_UDQM, // SDRAM High-byte Data Mask

DRAM_WE_N, // SDRAM Write Enable

DRAM_CAS_N, // SDRAM Column Address Strobe

DRAM_RAS_N, // SDRAM Row Address Strobe

DRAM_CS_N, // SDRAM Chip Select

DRAM_BA_0, // SDRAM Bank Address 0

DRAM_BA_1, // SDRAM Bank Address 1

DRAM_CLK, // SDRAM Clock

DRAM_CKE // SDRAM Clock Enable

);

input CLOCK_50; // On Board 50 MHz

input [3:0] KEY; // Pushbutton[3:0]

input [17:0] SW; // Toggle Switch[17:0]

output [17:0] LEDR; // LED Red[17:0]

inout [15:0] DRAM_DQ; // SDRAM Data bus 16 Bits

output [11:0] DRAM_ADDR; // SDRAM Address bus 12 Bits

output DRAM_LDQM; // SDRAM Low-byte Data Mask

output DRAM_UDQM; // SDRAM High-byte Data Mask

output DRAM_WE_N; // SDRAM Write Enable

output DRAM_CAS_N; // SDRAM Column Address Strobe

output DRAM_RAS_N; // SDRAM Row Address Strobe

output DRAM_CS_N; // SDRAM Chip Selectoutput

output DRAM_BA_0; // SDRAM Bank Address 0

output DRAM_BA_1; // SDRAM Bank Address 0

output DRAM_CLK; // SDRAM Clock

output DRAM_CKE; // SDRAM Clock Enable

assign LEDR = SW;

endmodule

3)编译并导入管脚信息

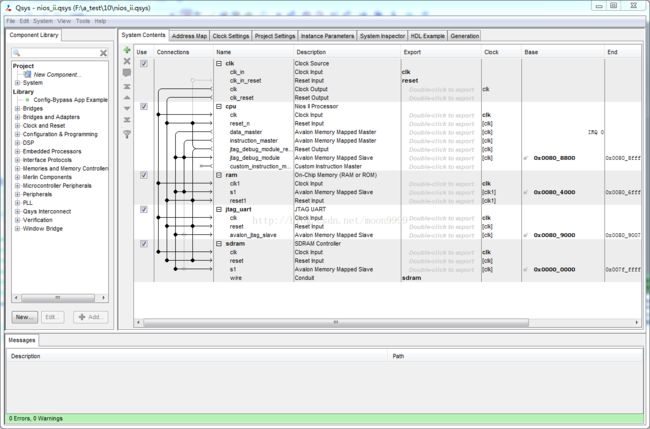

4)建立Qsys

CPU: NiOS II/e

ram: total memory size 12288bytes

jtag_uart: default

sdram_controller: DE2板子上的SDRAM大小为8M

接线图

修改CPU reset位置,自动生成地址,generate

将nios_ii.qsys文件添加入工程中

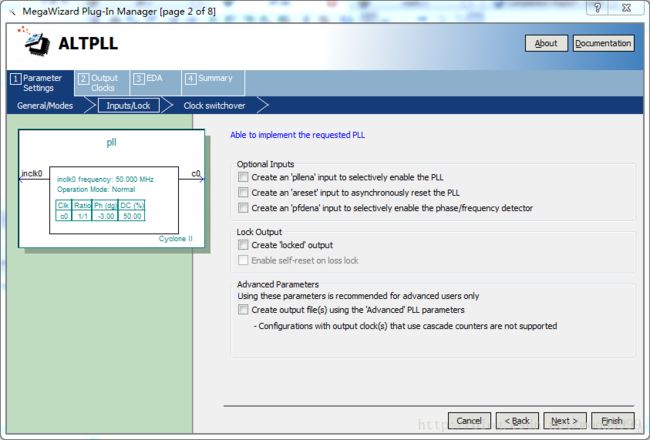

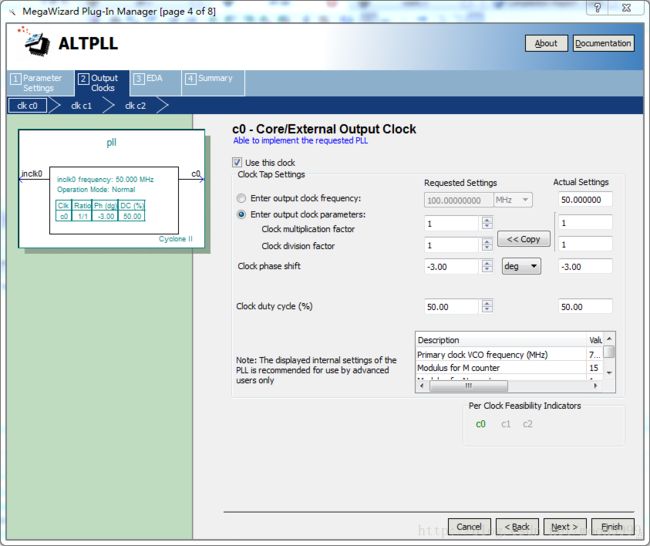

5)生成pll始终分频,将输入SDRAM的始终延时3ns(延时?前移?)

加入pll ip核,只需修改这两处

6)完成硬件代码

module work (

CLOCK_50, // On Board 50 MHz

KEY, // Pushbutton[3:0]

SW, // Toggle Switch[17:0]

LEDR, // LED Red[17:0]

DRAM_DQ, // SDRAM Data bus 16 Bits

DRAM_ADDR, // SDRAM Address bus 12 Bits

DRAM_LDQM, // SDRAM Low-byte Data Mask

DRAM_UDQM, // SDRAM High-byte Data Mask

DRAM_WE_N, // SDRAM Write Enable

DRAM_CAS_N, // SDRAM Column Address Strobe

DRAM_RAS_N, // SDRAM Row Address Strobe

DRAM_CS_N, // SDRAM Chip Select

DRAM_BA_0, // SDRAM Bank Address 0

DRAM_BA_1, // SDRAM Bank Address 1

DRAM_CLK, // SDRAM Clock

DRAM_CKE // SDRAM Clock Enable

);

input CLOCK_50; // On Board 50 MHz

input [3:0] KEY; // Pushbutton[3:0]

input [17:0] SW; // Toggle Switch[17:0]

output [17:0] LEDR; // LED Red[17:0]

inout [15:0] DRAM_DQ; // SDRAM Data bus 16 Bits

output [11:0] DRAM_ADDR; // SDRAM Address bus 12 Bits

output DRAM_LDQM; // SDRAM Low-byte Data Mask

output DRAM_UDQM; // SDRAM High-byte Data Mask

output DRAM_WE_N; // SDRAM Write Enable

output DRAM_CAS_N; // SDRAM Column Address Strobe

output DRAM_RAS_N; // SDRAM Row Address Strobe

output DRAM_CS_N; // SDRAM Chip Selectoutput

output DRAM_BA_0; // SDRAM Bank Address 0

output DRAM_BA_1; // SDRAM Bank Address 0

output DRAM_CLK; // SDRAM Clock

output DRAM_CKE; // SDRAM Clock Enable

assign LEDR = SW;

pll pll_u

(

.inclk0(CLOCK_50),

.c0(DRAM_CLK)

);

nios_ii u0 (

.clk_clk (CLOCK_50), // clk.clk

.reset_reset_n (KEY[3]), // reset.reset_n

.sdram_addr (DRAM_ADDR), // sdram.addr

.sdram_ba ({DRAM_BA_1,DRAM_BA_0}), // .ba

.sdram_cas_n (DRAM_CAS_N), // .cas_n

.sdram_cke (DRAM_CKE), // .cke

.sdram_cs_n (DRAM_CS_N), // .cs_n

.sdram_dq (DRAM_DQ), // .dq

.sdram_dqm ({DRAM_UDQM,DRAM_LDQM}), // .dqm

.sdram_ras_n (DRAM_RAS_N), // .ras_n

.sdram_we_n (DRAM_WE_N) // .we_n

);

endmodule9)打开nios II software编写软件代码

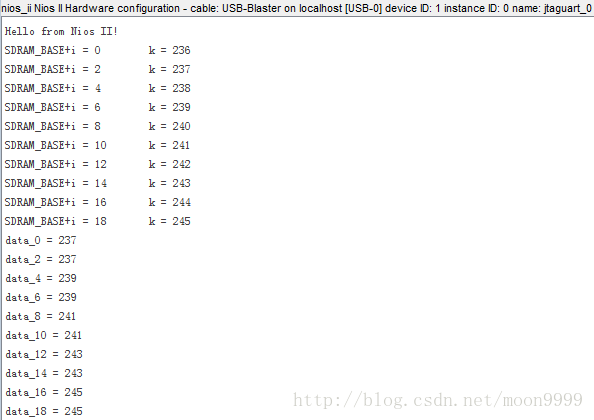

10)软件代码

软件代码里,地址信息跳变尝试了每次+1、+2、+4,在+4的情况下得到了正确数据。

推测这一情况与软核为32位系统,SDRAM存储空间为8位空间有关?

有待进一步探究

#include

#include"system.h"

#include"io.h"

int main()

{

unsigned int i, j, k;

k = 236; //随便写的一个数

printf("Hello from Nios II!\n");

for(i = 0; i<40; i = i + 4){

IOWR(SDRAM_BASE+i, 0, k);

printf("SDRAM_BASE+i = %d\t",SDRAM_BASE+i);

printf("k = %d\n",k);

k++;

}

for(i = 0; i<40; i = i + 4){

j = IORD(SDRAM_BASE+i, 0);

printf("data_%d = %d\n", SDRAM_BASE+i, j);

}

return 0;

} 11)edit BSP -> bulid project -> run as NIOS II hardware烧录软件

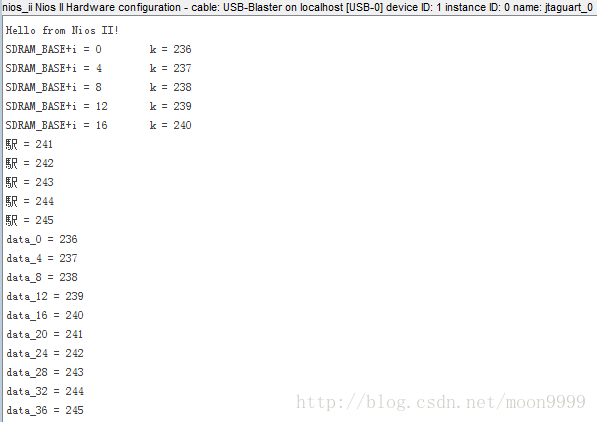

3.读写结果

地址跳变每次 i = i +1; 数据读写与想象不同

地址跳变每次 i = i +2; 数据读写与想象不同

地址跳变每次 i = i +4; 忽略出现的奇怪的显示,数据读写无误

解决:SDRAM的数据一般占据4个地址,或者8个地址,存在对其的问题,因此地址为应该+4或者4的倍数。