Zynq初识

本文内容学习自正点原子的Zynq教学视频:正点原子ZYNQ教学视频-B站

1.Zynq是什么?

我们先从SoC说起

SoC(System-on-Chip):片上系统 就是把原有的处理器(Processor),存储器(Memory),时钟(Clock),接口(Interface)等等资源从原来的焊接在一块PCB(Printed Circuit Board)板上的系统变成一块ASIC(Application Specific Integrated Circuit )专用集成电路也就是芯片。

优点:体积更小。

缺点:需要集成到的一块ASIC上,流片成本高且逻辑功能不能修改。

SoPC(System-on-Programmable-Chip): 可编程片上系统 一般是基于FPGA,用FPGA实现各个功能模块实现片上系统。

优点:相比基于ASIC的SoC更为灵活,可以随意修改。

缺点:FPGA内部资源有限,实现SoC时资源会很限制,并且搭建的处理器速度不会很快。比如:FPGA内部的PLL和Memory资源都是非常有限的。

APSoC(ALL-Programmable-SoC): 全可编程片上系统 全可编程意味着软件可编程(基于ARM的处理器),硬件也可编程(基于FPGA)。说白了就是把FPGA和一块基于ARM的处理器搞到一块芯片上去,这点其实也很好想到。当时我们做电赛练习时就非常想让单片机和FPGA结合起来用,这样既可以利用FPGA并行运算的速度也可以利用单片机做控制和一些其他功能的灵活性。

优点:具有一个真正的硬核处理器ARM,性能好,可以直接运行一个Linux系统。FPGA做并行处理和定制功能,ARM进行控制和操控。

所以

Zynq-7000系列就是Xilinx公司推出的一款基于双ARM Cortex-A9处理器和自己家FPGA的APSoC。

2.Zynq的架构

Zynq实际上就3个部分

1.PS(Processing System):处理系统 核心是ARM Cortex-A9处理器,但不仅仅只有处理器而已。PS才是Zynq的核心

2.PL(Programmable Logic): 可编程逻辑 显而易见这部分就是一块FPGA。

3.AXI(Advanced eXtensible Interface)高级可扩展接口:一种高性能、高带宽、低延迟的片内总线协议。用于PL和PS部分的通信。它是ARM公司AMBA(Advanced Microcontroller Bus Architecture)协议的一部分。

因为PL部分没啥可介绍的,它就是一块儿FPGA所以主要介绍PS和AXI总线。

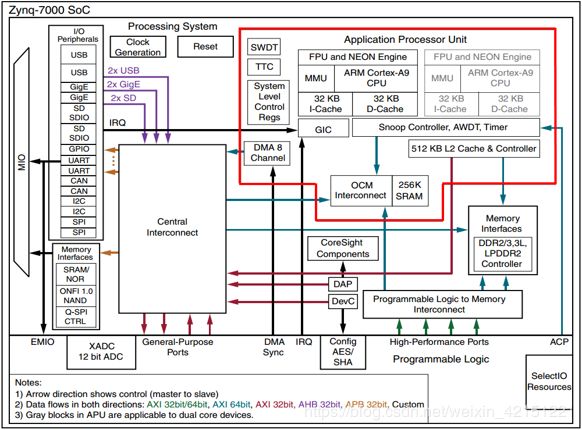

PS(Processing System)

这种图让我一眼看过去真是一脸懵逼,我的理解简单来说就是两块ARM Cortex-A9 CPU 作为核心再弄一些总线、时钟什么乱七八糟的。

红线圈出的部分就是PS的核心部分APU(Application Processor Unit) 。

重点是这张图的下方是PS与PL的连接部分。下面从APU开始一点点稍微了解一下PS里面都有什么

//随便写写反正我觉得了不了解这些应该对于工程实践无关痛痒,但是害怕后面开发的时候遇到什么问题,还是稍微了解一下

APU(Application Processor Unit)

FPU(Float Point Unit)浮点运算单元:专用于浮点运算的处理器。

NENO engine:单指令多数据处理 比如:视频图像处理,可以将很多像素点同时并行处理。并行数据处理加速。

MMU(Memory Management Unit) 内存管理单元:物理地址到虚拟地址的映射。

Cache 高速缓冲存储器:CPU和RAM之间的缓冲存储器。1级Cache I-Cache指令,D-Cache数据。2级Cache两个CPU通用

OCM(On Chip Memory) 片上存储器:实际上是块儿SRAM。

SCU(Snoop Controller)一致性控制单元:实现CPU到2级Cache和OCM的访问控制。

DMA(Direct Memory Access) 直接内存存取:直接将存储器中的数据互相传递而不需要经过CPU

GIC(Generic Interrupt Controller)通用中断控制器

APU之外

Central Interconnect:用于连接各个模块,做通信的管理

I/O Peripherals:连接到MIO(Multiplex IO)使SOC与外界通信,可以配置MIO的接口接到不同的I/O Peripherals的接口上去

与PL连接但不属于AXI的接口

EMIO(Extend MIO):如果PS的54个MIO不够用了,就可以使用EMIO。EMIO是连接到PL部分的,可以通过PL再与外设相连,也可以直接连接PL内部自己写的模块。

X-ADC:PS连接PL里面的硬核ADC接口。

DMA sync:PL和PS实现DMA传输的接口。

IRQ(Interrupt ReQuest)中断请求:PL向PS终端请求的接口,连接到PS的GIC。

Config ASE/SHA:PS配置PL的接口,因为PS才是核心,Zynq也是PS先启动再启动的PL。

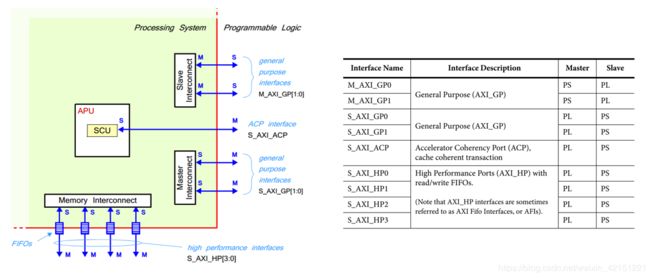

AXI(Advanced eXtensible Interface)

GP(General Purpose Interfaces):PS和PL的通用接口。M(Master)代表PS为通信主机(通信发起人),S(Slave)代表PS为通信从机。

ACP Interface:PL连接到SCU部分。PL到PS的2级Cache和OCM的低延时访问。实现使PL类似CUP到Cache的访问。PL为通信主机。

HP (High Performance Interface):高性能接口,高速大量数据传输。它上面的蓝色方块是一些FIFO(First In First Out)用作数据缓冲。

这里也是PL为通信主机。实际上是PL直接访问PS部分的Memory。