LVDS通信接口详细介绍

1. 概述

LVDS = Low-Voltage Differential Signaling 低电压差分信号,属于平衡传输信号。

这种技术的核心是采用极低的电压摆幅高速差动传输数据,从而有以下特点:

低功耗---低误码率---低串扰---低抖动---低辐射 良好的信号完整性。

推荐的最高数据传输速率是655Mbps,而理论上可以达到1.923Gbps。

在17inch及以上的液晶显示器中得到广泛应用。

2. 硬件结构

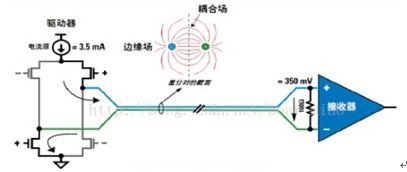

LVDS传输信号为平衡传输信号,TTL传输信号为非平衡传输信号;

LVDS传输信号为电流驱动信号,TTL传输信号为电压驱动信号;

终端匹配电阻标准规定为100Ω,由于恒流源为3.5mA,则摆动电平幅度为

-350mV~350mV。由于偏置电压为1.2V,则差分信号的电压范围为850mV~1550mV。

LVDS 信号传输由三部分组成:差分信号发送器,差分信号互联器,差分信号接收器。

发送器:将非平衡传输的TTL 信号转换成平衡传输的LVDS 信号。有独立和集成之分。

接收器:将平衡传输的LVDS 信号转换成非平衡传输TTL 信号,很高的输入阻抗。

互联器:包括联接线(电缆或者PCB 走线),终端匹配电阻。按照IEEE 规定 ,电阻为100 欧。我们通常选择为100 ,120 欧。

3. 接口分类

单路6位LVDS:采用单路方式传输,每个基色采用6位数据,共18位RGB数据;

双路6位LVDS:采用双路方式传输,每个基色采用6位数据,奇路数据为18位,偶路

数据为18位,共36位RGB数据;

单路8位LVDS:采用单路方式传输,每个基色采用8位数据,共24位RGB数据;

双路8位LVDS:采用双路方式传输,每个基色采用8位数据,奇路数据为24位,偶路

数据为24位,共48位RGB数据;

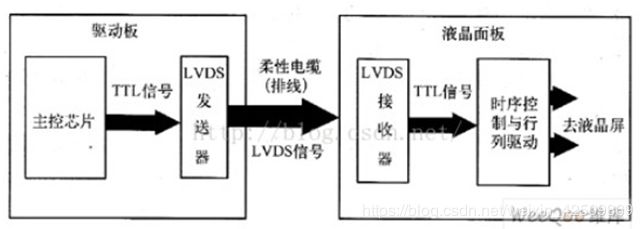

4. 发送芯片

LVDS发送芯片将以并行方式输入的TTL电平RGB数据信号转换成串行之LVDS信号

后,直接送往液晶面板侧之LVDS接收芯片。

四通道LVDS发送芯片:包含三个数据信号(其中包括RGB、数据使能、行同步、场同

步信号)通道和一个时钟发送通道;

主要用于驱动6bit液晶面板,可以构成单路或者奇偶双路6bit

LVDS接口电路。

五通道LVDS发送芯片:包含四个数据信号(其中包括RGB、数据使能、行同步、场同

步信号)通道和一个时钟发送通道;

主要用于驱动8bit液晶面板,可以构成单路或者奇偶双路8bit

LVDS接口电路。

十通道LVDS发送芯片:包含八个数据信号(其中包括RGB、数据使能、行同步、场同

步信号)通道和两个时钟发送通道;

主要用于驱动8bit液晶面板,用来构成奇偶双路8bitLVDS接口

电路。

5. 输入输出信号

- 输入信号

LVDS发送芯片之输入信号来自主控芯片,输入信号包含RGB数据信号、时钟信号和控

制信号三大类,RGB信号+数据选通信号DE+行HS场VS同步信号 = 数据信号。

输入数据信号:

例如:一个6bit液晶面板使用四通道LVDS发送芯片,共有:18个RGB信号+1个数据

使能信号+1个行同步信号+1个列同步信号 = 21个数据输入引脚;

输入时钟信号:

即像素时钟信号,也称为数据移位时钟(在LVDS发送芯片中,将输入之并行

RGB数据转换成串行数据时要使用移位寄存器)。像素时钟信号是传输数据和对数

据信号进行读取之基准。

待机控制信号:

当此信号有效时(一般为低电平时),将关闭LVDS发送芯片中时钟PLL锁相环电

路之供电,停止IC之输出。

数据取样点选择信号:用来选择使用时钟上升沿还是下降沿读取RGB信号数据。

- 输出信号

时钟信号输出:输出信号频率与输入信号频率相同,占据发送芯片一个通道;

串行数据信号输出:四通道发送芯片,串行数据占据三个通道;

注意:液晶显示器驱动板上的LVDS发送芯片的输出数据格式必须与液晶面板LVDS接

收芯片要求的数据格式相同,否则,驱动板与液晶面板不匹配。

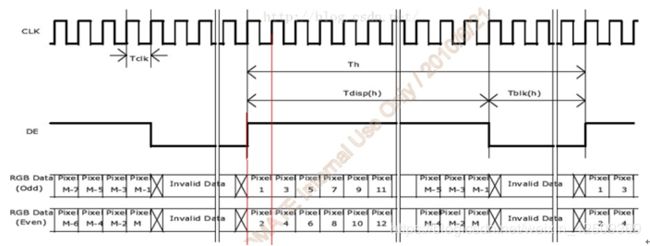

6. 数据输出格式

LVDS发送芯片在一个时钟脉冲周期内,每个数据通道都输出7bit的串行数据信号,而不

是常见的8bit数据,如下图所示:

以8bit RGB显示屏接口为例,每个显示周期需要传输8bit的R信号,8bit的G 信号,

8bit 的B信号,及VS,HS,DE信号,总共为27 BIT。而每对LVDS信号线在一个TX

周期里只能传输7BIT数据,所以需要4 对数据线,外加一对时钟线。

LVDS并串转换如下图所示:

上图每组差分线称为一个pair,四组数据线加一组时钟线称为一个channel;

LVDS发送器总是将一个像素数据映射到一个channel的一个发送周期中。

如果是6BIT 显示屏,则并行数据有21位(18位RGB加3位控制信号),因此LVDS 接口每个Channel只需要 3对数据线和一对时钟线。

如果是10BIT 显示屏,则并行数据有33位(30位RGB 加3位控制信号),因此LVDS 接口每个Channel需要 5对数据线和一对时钟线。

LVDS的时钟一般为20MHz~85MHz,因此输出像素时钟低于85MHz的信号,只需要一个channel就可以。而对于输出像素时钟高于85MHz的,比如1080p@60Hz的输出,像素显示时钟为148.5MHz,就需要将输出像素按照顺序分为奇像素偶像素用两个channel传输;对于更高的1080p@120Hz,则需要四个channel分配。

7.数据映射标准

LVDS接口电路中,将像素的并行数据转换为串行数据的格式主要有两种标准:

VESA和JEIDA

VSEA标准如下图所示:

JEIDA标准如下:

如果像素为6bit RGB,则每个通道只需要最上面的3对数据线,其中的R9…R4, G9…G4, B9…B4 对应实际的R5…R0, G5…G0, B5…B0;

COLOR MAPPING 也可以采用自定义格式,只要LVDS 发送端和接受端采用相同的映射

顺序,就可以显示正确的色彩。