Microsemi Libero系列教程(六)——Identify片上逻辑分析仪的使用

文章目录

- FPGA如何进行在线调试

- 关于Microsemi片上逻辑分析仪

- FPGA片上逻辑分析仪原理

- 预期效果

- 0.准备一个创建好的Libero工程

- 1.新建identify工程,并添加想要监测的信号

- 2.管脚分配,编译下载

- 3.设置触发类型

- 4.IICE逻辑分析仪核资源占用

- 示例工程下载

- 参考资料

系列教程: Microsemi Libero系列教程

FPGA如何进行在线调试

对于嵌入式系统来说,如单片机,进行硬件级程序调试时,通常采用的是JLink/ST-Link调试器,在线调试的方式来获取程序实时运行的状态,可以观察程序运行流程、各种变量的值、中断的触发情况,还可以设置断点、单步运行,方便快速的发现BUG,解决问题。

但是对于FPGA来说,并不是顺序执行的,而是根据每一个Clk并行执行,所以我们不能使用调试器进行单步调试。

FPGA调试需要观察内部信号的值,各个信号之间的时序关系,所以使用逻辑分析仪是最好的调试方式了。

有些FPGA工程,对外的接口,即输入输出,可能只有几个,但是他们之间的逻辑和时序关系非常复杂,所以内部有几十个中间寄存器,程序下载进去了,发现不是我们想要的效果,怎么办?你可能会说,查代码吧!如果这个工程非常简单,你可能只需要耗费几分钟或者几个小时就可以定位代码的问题所在。

但是如果这是一个非常庞大的工程,内部的中间寄存器、信号,几百上千个,各个模块单独软件仿真都正常,整体仿真也正常,就是下载到实际的芯片中运行不正常。你如何进行问题定位?如果再去进行代码审查,这将会消耗非常多的时间。那么如果能在FPGA芯片内部装上一个逻辑分析仪,那不就直接可以看到内部信号的值了,而且还可以看到各个信号之间的时序关系。需求推动技术发展,既然开发者有这个需求,那么FPGA厂商肯定会实现这个功能!下面来一起看一下Microsemi FPGA片上逻辑分析仪的使用方法吧!

关于Microsemi片上逻辑分析仪

几大厂商的片上逻辑分析仪:

- Xilinx厂商ISE开发环境下的ChipScope工具

- Altera厂商Quartus开发环境下的SignalTap工具

- Lattice厂商Diamod开发环境下的Reveal工具

对于 FPGA 工程师来说,这些都是很熟悉的名字。和以上几大FPGA厂商一样,Microsemi Libero也支持片上逻辑分析仪工具,只不过不是自己家研发的,使用的是Synospsy公司出品的Identify工具,其实,Libero中的综合器synplify也是Synospsy公司的。

根据Synospsy官网的描述:Identify RTL 调试仪,这个调试工具除了支持Microsemi的FPGA产品外,还支持Altera和Xilinx的FPGA产品,这两款FPGA我没有尝试过。我只在Microsemi Libero中使用过。

identify的使用,不会影响原有程序的功能和时序,也不会打断原有程序的运行,可以理解为在原有的硬件电路上挂了一个逻辑分析仪,进行监测!

FPGA片上逻辑分析仪原理

Identify片上逻辑分析仪的原理,是通过在FPGA工程中加入一个IICE逻辑分析仪IP核,这个IP核,由控制器和采集器组成,采集器用于采集信号,控制器用于和JTAG调试器连接,并把数据发送到上位机,IICE内部有RAM空间,用于存储触发位置附近的信号,RAM空间的大小,即采样深度,可以自己调整。FPGA工程中加入IICE核,会占用一定的资源,资源占用的大小取决于:采样深度,采样信号的个数,采样信号的触发方式等。

所以综上,FPGA片上逻辑分析仪需要3个组件:片上的IICE逻辑分析仪核、JTAG下载器、上位机。

JTAG下载器也就是我们下载程序时使用的FlashPro x下载器,上位机软件也就是Identify工具,这个工具已经在安装Libero SoC时一同安装并注册激活了。所以不需要安装其他的工具软件,只需要在已经设计好的FPGA公司中,配置一下IIC逻辑分析仪核就可以了。

扯了这么多,下面进入正题,来介绍一下如何在已经创建好的Libero工程中,加入IICE逻辑分析仪核,并演示Identify工具的使用。

预期效果

以Microsemi SmartFusion系列的A2F200M3F芯片为例,其他芯片使用操作方法类似。示例工程功能:led每隔10个clk翻转一次为例,演示identify的使用。

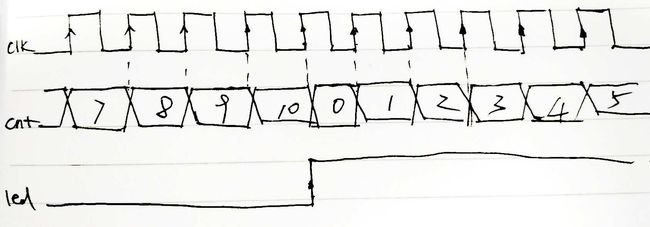

identify添加完成之后,把led设置为上升沿触发,会抓取到类似如下的波形。

0.准备一个创建好的Libero工程

这里以LED每隔10个时钟周期翻转为例。HDL文件内容:

module led_demo(

//inputs

input clk,

input rst_n,

//outputs

output reg led

);

reg [3:0] cnt;

always @ (posedge clk)

begin

if(!rst_n)

cnt <= 0;

else if(cnt == 10) /* max=10, 0-10 */

cnt <= 0;

else

cnt <= cnt + 1;

end

always @ (posedge clk)

begin

if(!rst_n)

led <= 0;

else if(cnt == 10)

led <= ~led;

end

endmodule

1.新建identify工程,并添加想要监测的信号

1.1 在Synthesize上右键,选择Open Interactively

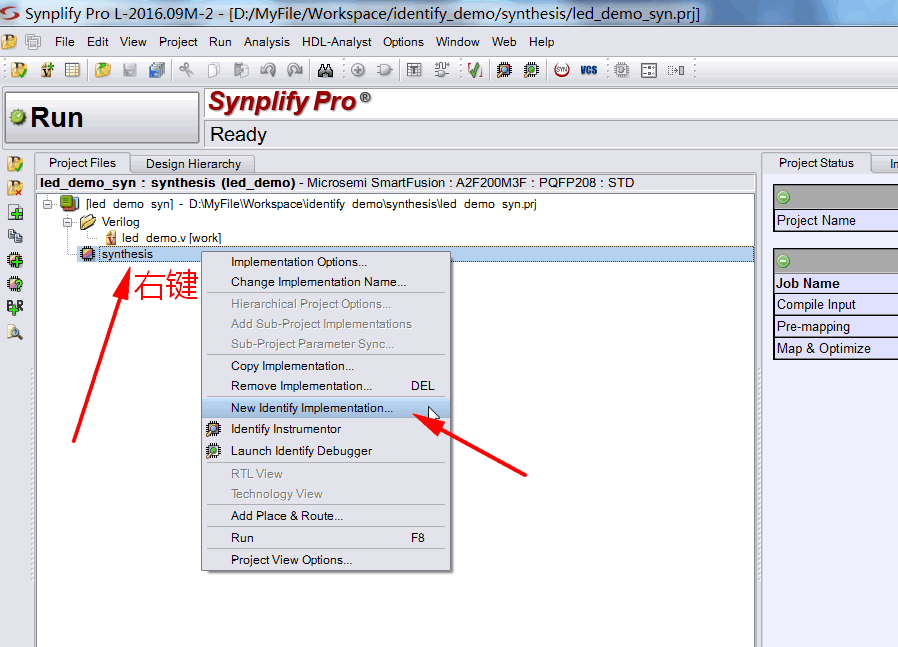

1.2 在Synthesis上右键新建一个Identify工程

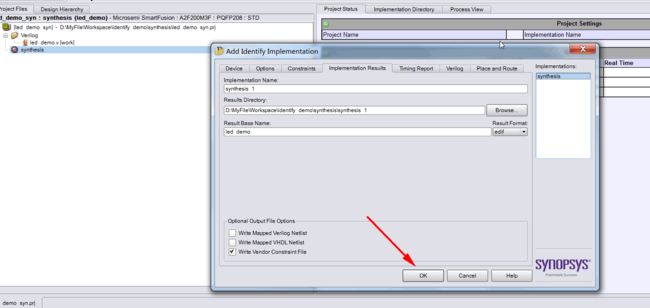

1.3 输入新建的identify工程的名称和保存路径,选择默认的就行。

1.4 在新建的identify工程上右键选择identify instrumentor

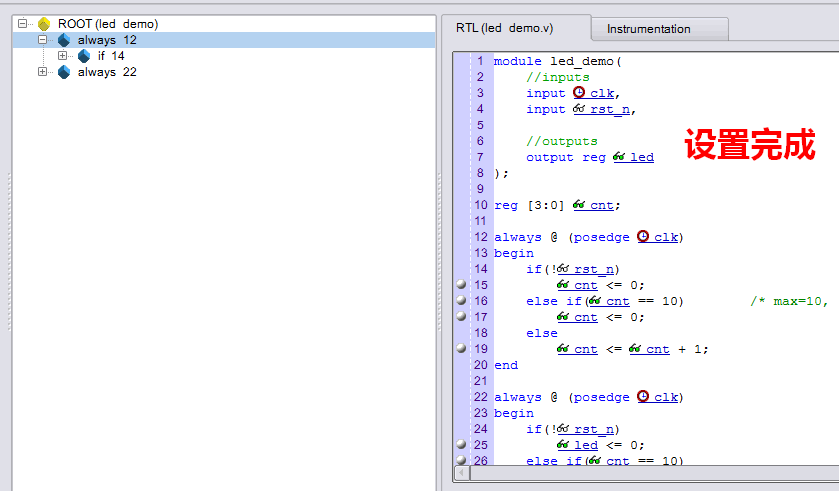

1.5 在HDL文件中选择要监测的信号和采样时钟,采样时钟选择Sample Clock,作为触发的信号选择Trigger Only,要监测的信号选择Sample Only,也可以选择Sample and Trigger,这样会占用更多的资源。

设置完成的信号会有标注

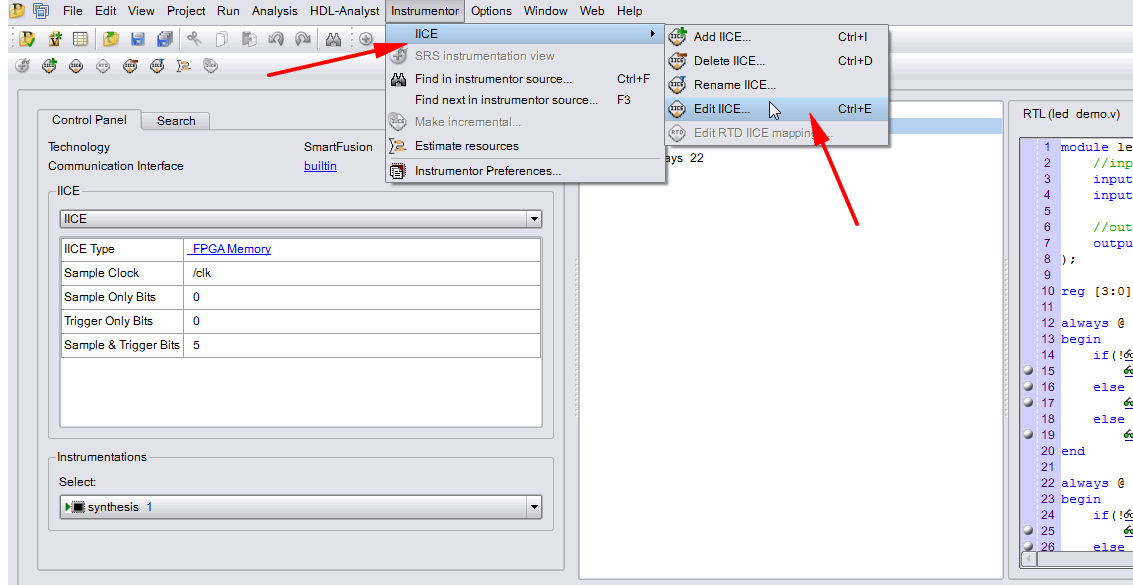

1.6 设置采样深度,选择Instrumentor->IICE->Edit IICE。

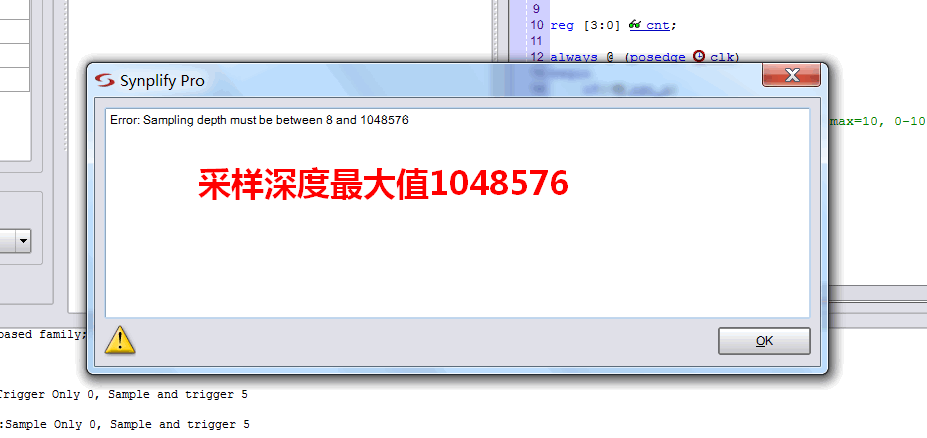

采样深度最大支持1048576

输入采样深度,数值越大,采样时间越长,相应的FPGA资源占用也越多。

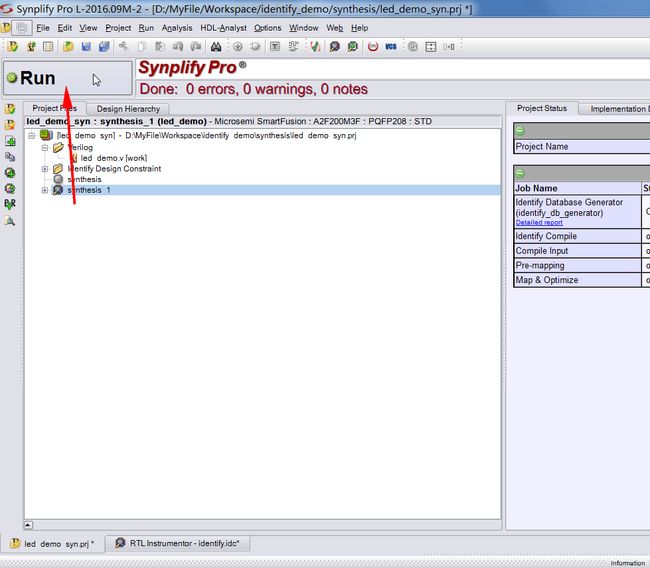

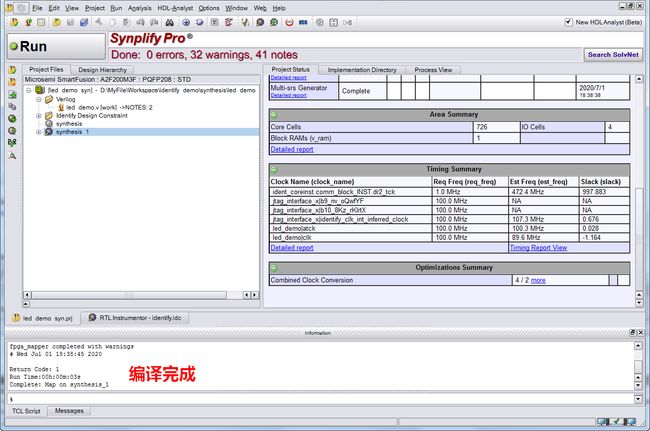

1.7 选择Run->Run

或者直接点击主界面的Run按钮

1.8 编译完成之后,保存退出。

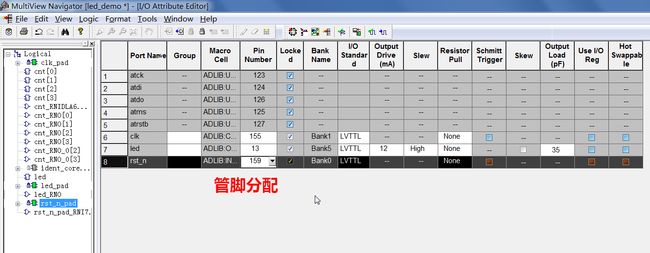

2.管脚分配,编译下载

2.1 和正常流程一样,管脚分配,编译下载。可以看到JTAG部分的管脚已经被IICE逻辑分析仪核使用了。

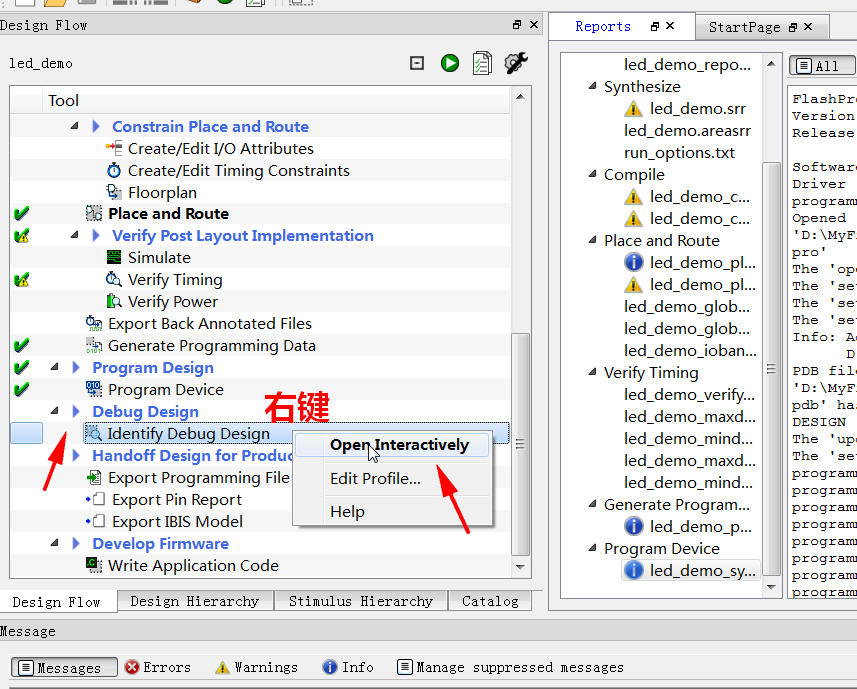

2.2 在Identify Debug Design上右键,选择Open Interactively,打开identify工具

3.设置触发类型

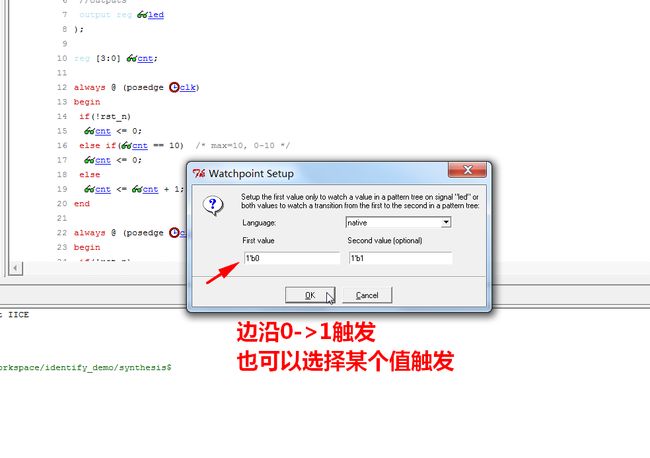

3.1 选择要触发的信号,和触发类型,这里我选择的是led,上升沿触发。

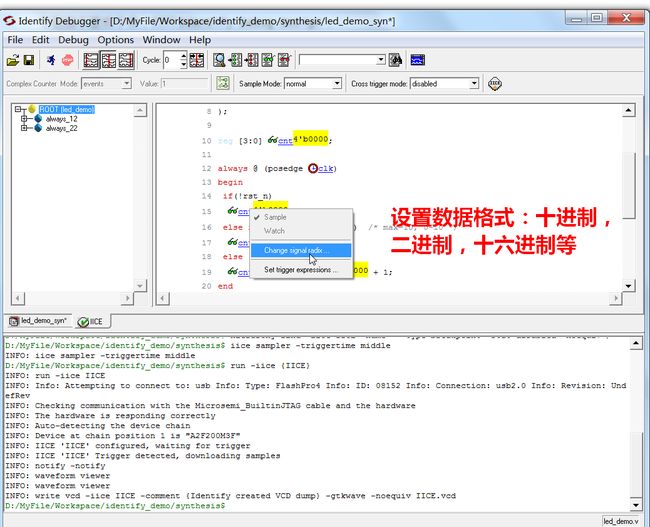

3.2 连接FlashPro下载器,点击小人图标,启动抓取,满足触发条件自动停止。

D:/identify_demo/synthesis$ run -iice {IICE}

INFO: run -iice IICE

INFO: Info: Attempting to connect to: usb Info: Type: FlashPro4 Info: ID: 08152 Info: Connection: usb2.0 Info: Revision: UndefRev

INFO: Checking communication with the Microsemi_BuiltinJTAG cable and the hardware

INFO: The hardware is responding correctly

INFO: Auto-detecting the device chain

INFO: Device at chain position 1 is "A2F200M3F"

INFO: IICE 'IICE' configured, waiting for trigger

INFO: IICE 'IICE' Trigger detected, downloading samples

INFO: notify -notify

INFO: waveform viewer

INFO: waveform viewer

INFO: write vcd -iice IICE -comment {Identify created VCD dump} -gtkwave -noequiv IICE.vcd

D:/identify_demo/synthesis$

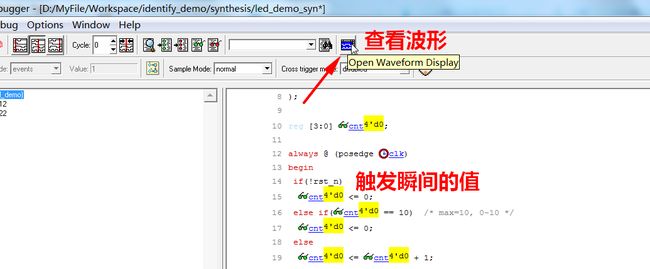

3.3 右侧黄色的显示就是触发瞬间时信号的值。右键可以改变数据格式。

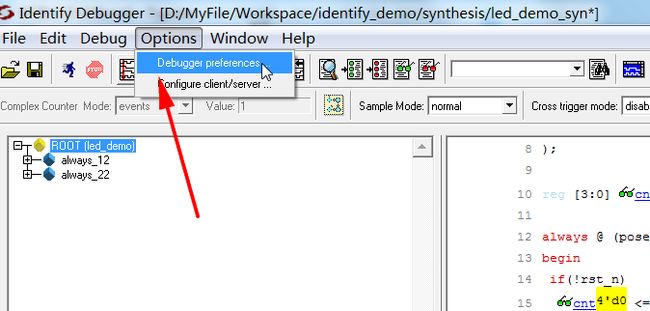

3.4 选择Debugger preferences可以设置采样时钟的周期,用于后面波形的时间测量

3.5 设置采样时钟的周期

3.6 点击波形按钮,在GTKWave中打开抓取到的波形。

3.7 可以按住左键拖动测量时间差

3.8 还可以给每个通道设置不同的颜色,和显示方式。

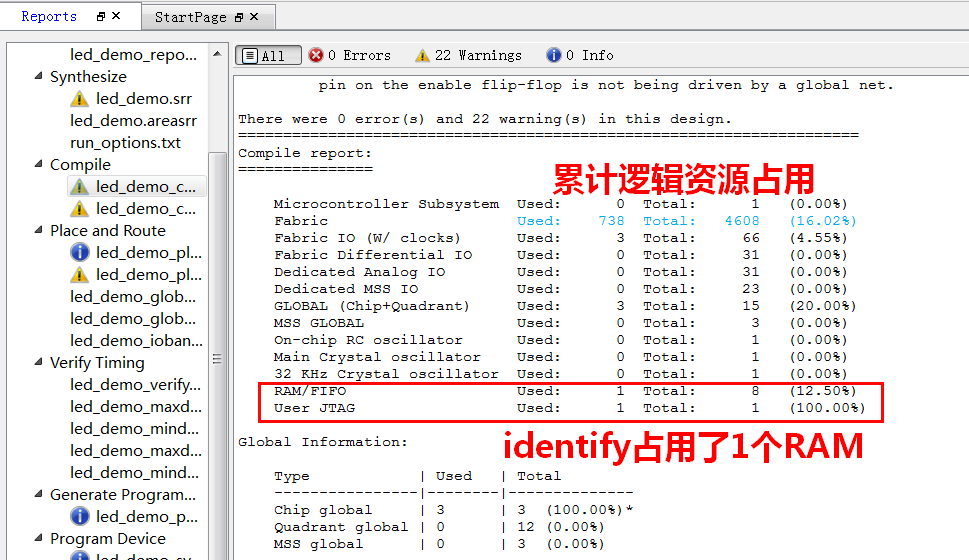

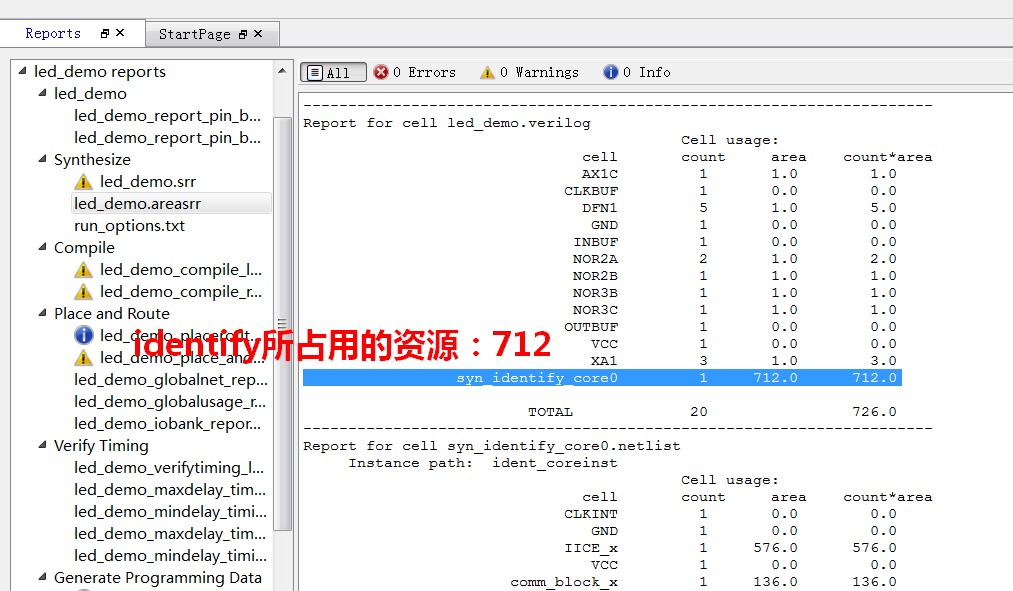

4.IICE逻辑分析仪核资源占用

IICE逻辑分析仪核占用的主要是逻辑资源和RAM资源,可以看到资源占用还是很多的。

示例工程下载

identify_demo.rar

参考资料

- https://zhuanlan.zhihu.com/p/88314552

- https://www.synopsys.com/zh-cn/implementation-and-signoff/fpga-based-design/identify-rtl-debugger.html

- http://training.eeworld.com.cn/video/1059

- https://www.microsemi.com/document-portal/doc_view/132760-synopsys-identify-me-h-2013-03m-sp1-user-guide