SmartFusion从FPGA到ARM(一)——MSS_GPIO点灯

文章目录

- 前言

- 0.开发环境准备

- 1.创建一个基本工程

- 2.配置MSS模块

- 3.生成示例工程

- 4.Keil编译ARM工程

- 5.FPGA工程加载Hex文件

- 6.下载运行

- 7.JTAG_SEL管脚说明

- 示例工程下载

前言

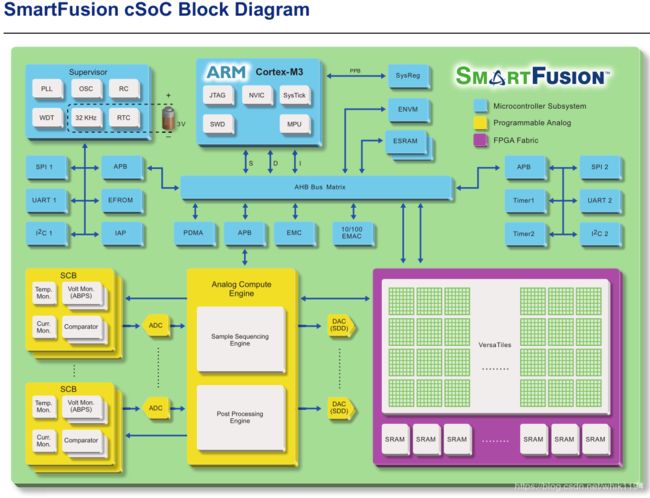

本系列教程,将会以SmartFusion一代芯片A2F200M3F为例,简单介绍片上ARM Cortex-M3 硬核 MCU部分的使用,及其与FPGA逻辑模块进行交互的示例。在学习片上硬核ARM Cortex-M3 MCU的开发之前,要先熟悉Microsemi Libero SoC的使用,可以参考:Microsemi Libero SoC系列教程

关于Microsemi SmartFusion混合型FPGA的介绍,可以参考:Microsemi SmartFusion系列FPGA简介

作为单片机界的“Hello World”,用GPIO点灯恐怕是每个刚入门单片机的朋友的必经之路。本文介绍使用片上ARM硬核MCU的GPIO,即MSS_GPIO,来驱动外部的LED,演示从Libero工程创建,MSS子系统配置,Keil示例工程生成,Hex文件生成和加载,程序运行整个流程。

0.开发环境准备

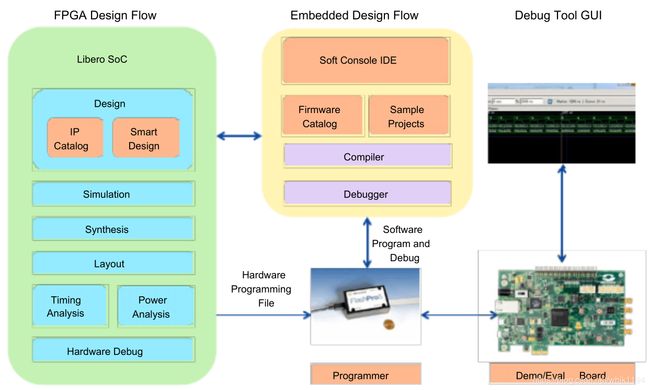

- FPGA开发环境:Libero SoC V11.8

- ARM开发环境:Keil MDK v4/v5,SoftConsole,IAR

- FlashPro下载器:FlashPro 4/5

- 固件库下载地址:Firmware_MSS_GPIO_Driver_v2.0.105

1.创建一个基本工程

准备一个空白工程,没有添加任何的设计文件。

2.配置MSS模块

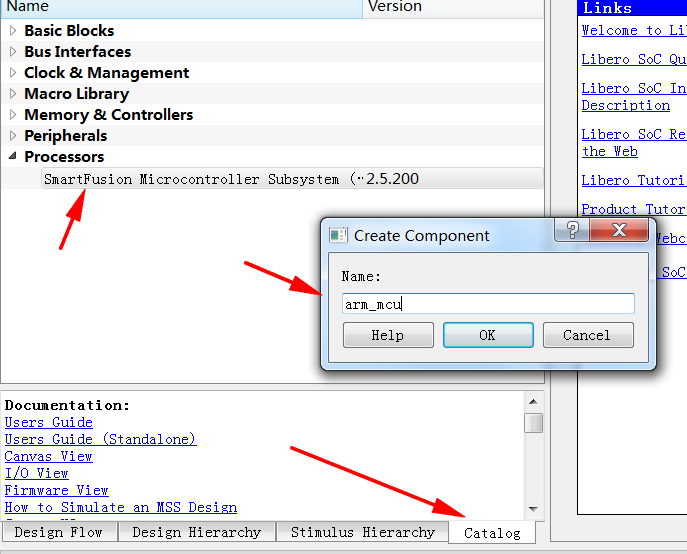

点击工程视图下的Catalog->Processor,双击创建一个Microcontroller System子系统,即片上硬核MCU,并命名为arm_mcu。

这样我们就创建了一个ARM Cortex-M3的MCU

可以看到都是一些非常常见的外设,UART、TIMER、GPIO、SPI、IIC等,这些外设都可以根据我们的需要进行使能,这里我们只使用到了GPIO,所以只开启了GPIO。双击GPIO,可以配置要使用的GPIO模式,MSS_GPIO只有32个,可以根据需要设置为输入,输出,或者输入输出双向。如果不够用,可以通过CoreGPIO IP核进行扩展,后面的教程我们再学习。这里我们把GPIO_0和GPIO_1配置成输出模式,用于驱动LED。

在生成之前,还需要配置内核的主频和PLL的输入时钟。双击Clock,按照图示,配置成外部时钟输入,PLL倍频成100MHz,作为ARM内核的主频。如果不是所有外部晶振,片上还有RC振荡器,使用方法可以参考:片上时钟和PLL的使用

配置完成之后

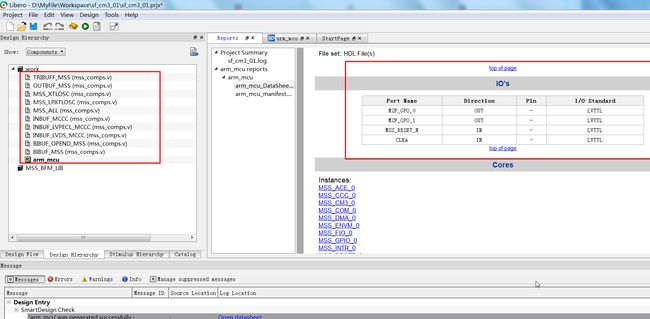

因为我们的工程比较简单,不涉及到FPGA逻辑部分,所以这里我们没有再创建一个SmartDesign画布,用于和其他FPGA模块进行连接。可以直接点击左上角生成按钮,把我们图形化配置的模块,生成verilog文件,每次改动之后,都要重新生成。

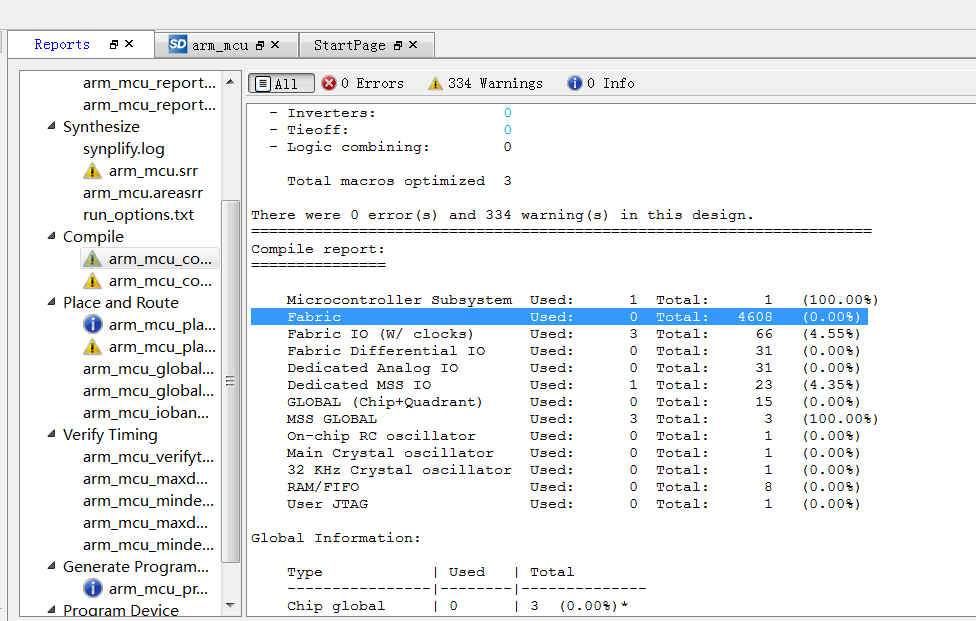

生成完成之后,我们可以看到多了很多的.v文件,还可以查看生成的报告:

FPGA部分就配置完成了,下面我们来生成ARM MCU对应的Keil工程,并写一些控制代码,让LED闪烁起来。

FPGA部分就配置完成了,下面我们来生成ARM MCU对应的Keil工程,并写一些控制代码,让LED闪烁起来。

3.生成示例工程

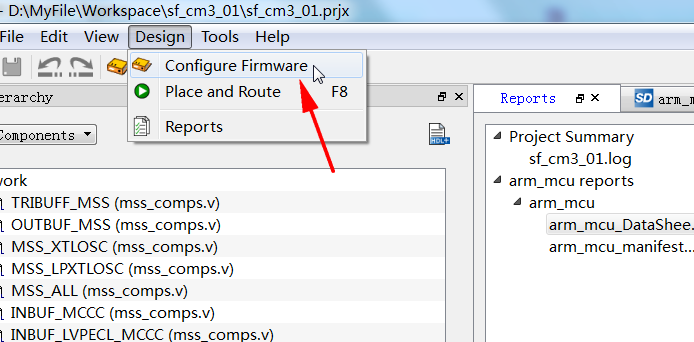

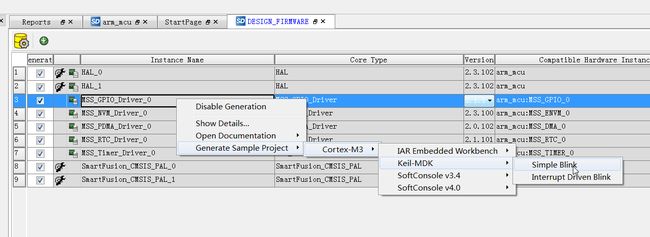

点击Design->Configure Firmware,可以看到当前已经安装的驱动示例包,

在打开的界面中,选择生成GPIO驱动LED的Keil例程,还支持其他IDE的例程,如官方的SoftConsole,IAR等开发环境。

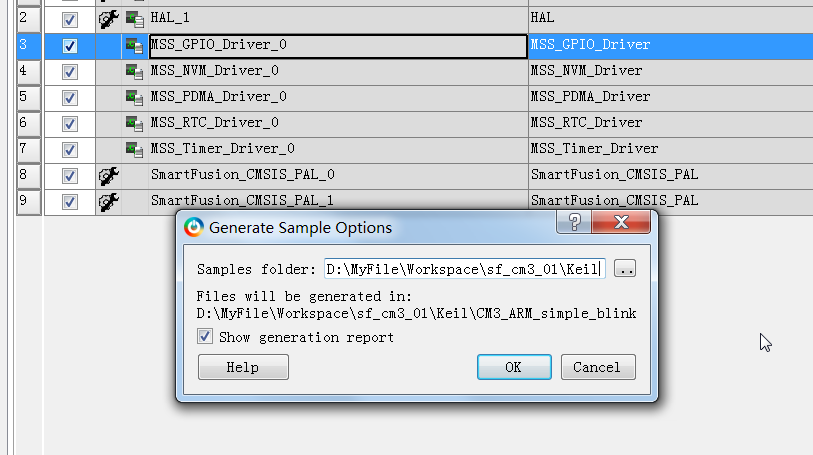

选择保存路径

点击OK之后,会在当前工程目录Keil文件夹下,生成一个简单的LED闪烁的例程。

4.Keil编译ARM工程

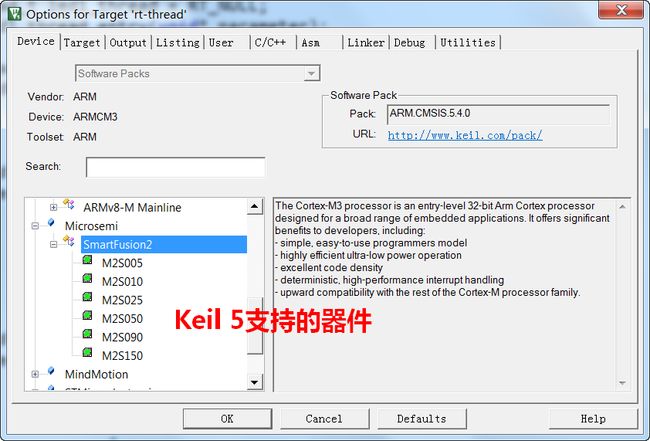

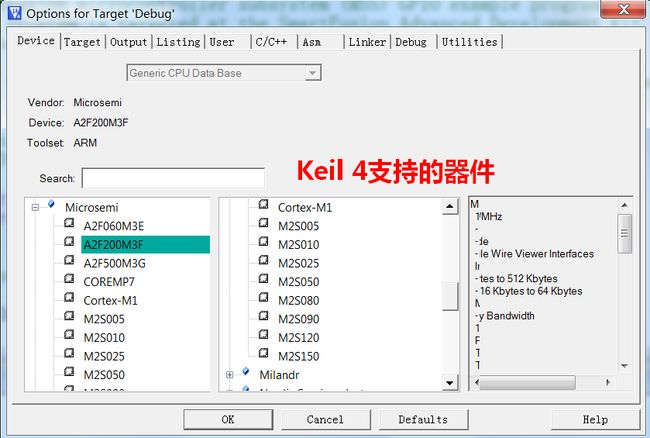

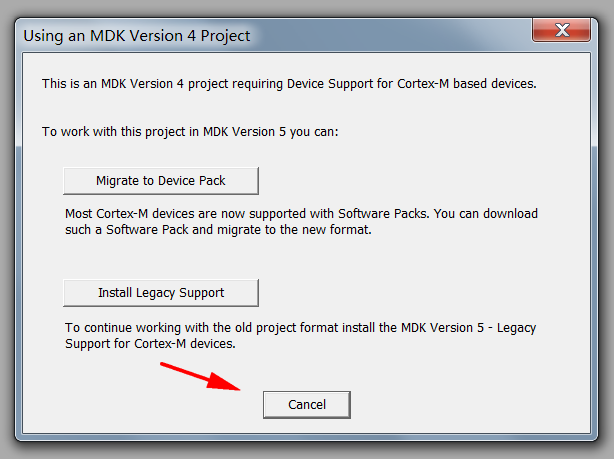

生成的例程是一个完整的工程,包括CMSIS相关的文件,启动文件,驱动库等,可以直接使用Keil打开。默认生成的是Keil 4的工程,我安装的是Keil 5,Keil 4环境集成了器件包,其中就包括A2F200M3F器件,而Keil 5需要手动安装器件包,但是Microsemi的器件包只有SmartFusion 2系列,不支持我们的A2F200M3F。

所以如果只进行编译,不进行在线调试,那么使用Keil 4和Keil 5都行,如果想使用Jlink等调试对ARM内核进行在线调试,那么只能使用Keil 4。这里我们只需要生成Hex文件即可,不进行在线调试,所以直接选择Cancel取消即可。

打开工程之后,就是非常熟悉的C语言代码了,主函数非常简单,初始化了两个GPIO为输出模式,然后死循环,向下计数延时,减到0时,所有的GPIO反转,重新装载计数值。其实我们只想要GPIO_0和GPIO_1翻转即可,这些可以自己调整,都是一些很简单的运算。

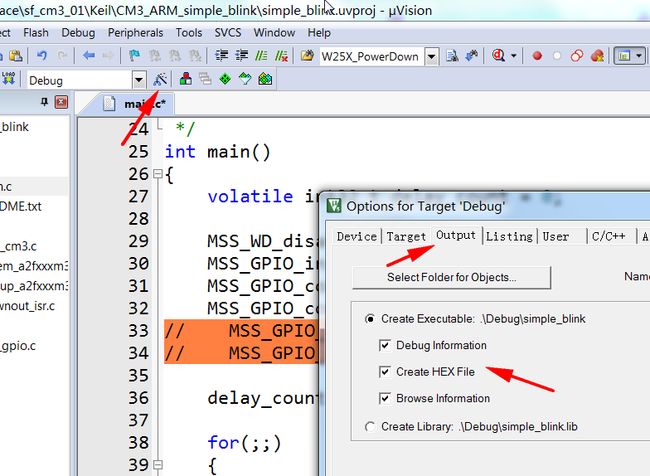

配置工程编译生成Hex文件,默认生成的例程中,并不会生成Hex文件,我们需要手动配置一下。

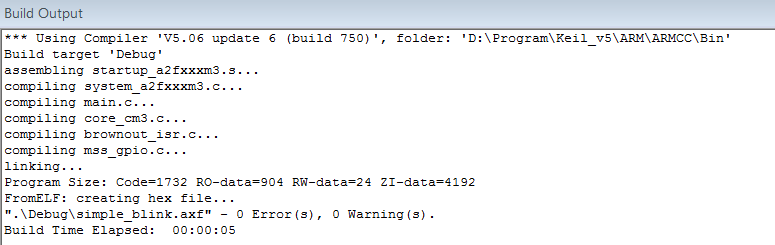

编译,生成Hex文件, 0警告,0错误,我想这是每一个单片机开发者都想看到的输出信息。

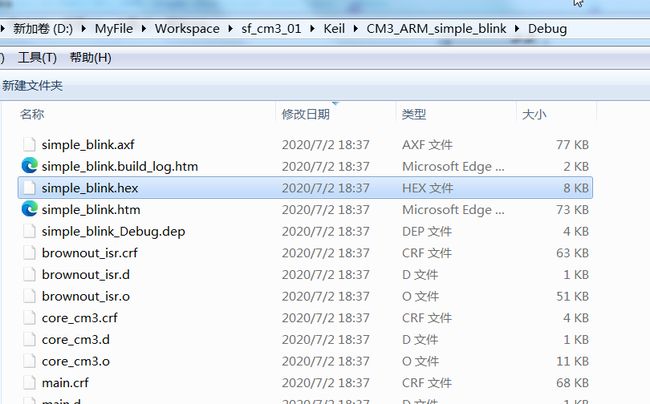

会在Debug目录生成一个Hex文件

5.FPGA工程加载Hex文件

之前,我们只是在FPGA工程中配置了ARM核, 但是并没有加载我们的应用程序,即Hex文件。下面我们把Keil生成的Hex文件,加载到FPGA工程中去。双击ENVM,选择Data Storage,输入名称和Hex文件的路径。

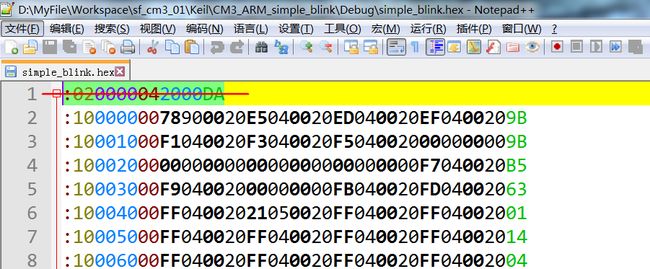

会发现加载失败,这是因为起始地址太大了,再加上Size的大小,超过了Flash的地址范围。提示上面的错误有两种方式可以解决。

第一种方法是把生成的hex文件,以文本方式打开,然后把第一行的内容删除,无视起始地址。

再次加载就没问题了

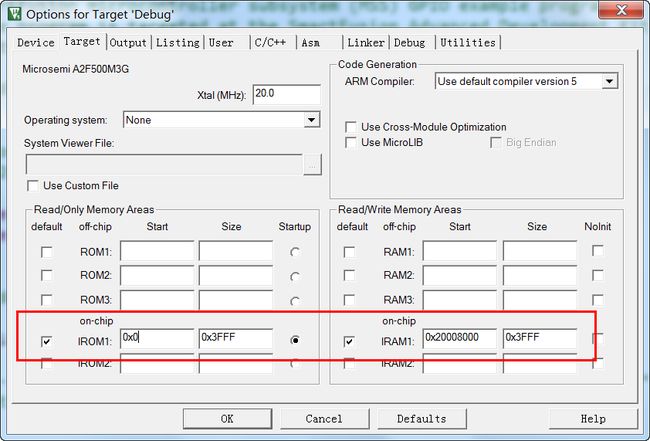

第二种方法,是修改Keil中生成的Hex文件起始地址:

先修改起始地址为0x0

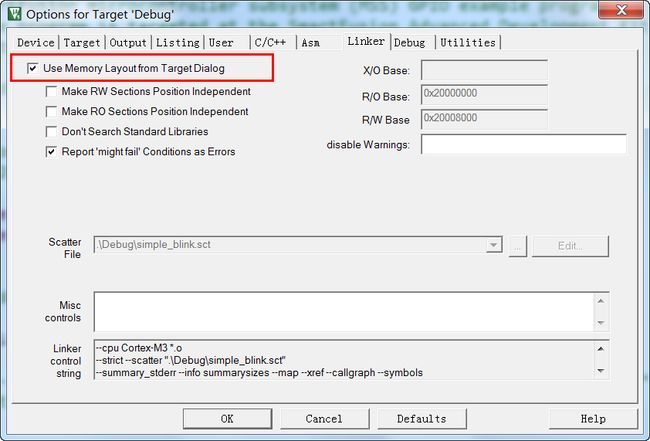

勾选上链接选项中的User Memory Layout from Target Dialog

再次加载就没问题了。

6.下载运行

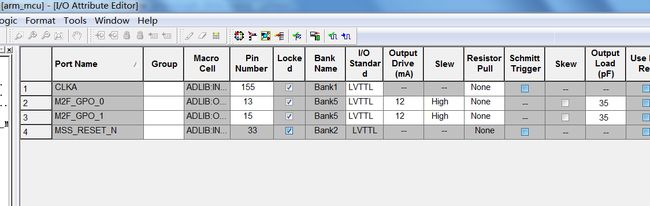

在加载Hex文件之后,要重新生成Component,如果没有错误,就可以进行管脚分配了。

这里就体现了FPGA上硬核的方便之处,这32个GPIO可以根据需要直接分配到任芯片上的用户管脚上,而不是固定为某一个。

从编译报告可以看出,ARM Cortex-M3 硬核的使用,并不会占用FPGA的Fabric资源。

连接下载器,下载运行,可以看到LED灯闪烁起来了。

7.JTAG_SEL管脚说明

如果FPGA工程中ARM硬核已经配置完成,比如配置了GPIO_0和GPIO_1为输出,驱动LED闪烁,但是我想修改闪烁的频率,只需要使用Jlink或其他ARM调试器直接下载ARM程序到FPGA即可,可以通过JTAG_SEL管脚来选择给FPGA下载程序,还是给ARM内核下载程序。

但是,如果FPGA工程中只配置了GPIO_0和GPIO_1为输出,我想再增加GPIO_2为输出,或者是我想修改GPIO_0位输入模式,此时,只修改ARM程序不能完成配置,还需要修改FPGA工程中的MSS模块配置。

示例工程下载

sf_cm3_01.rar