modelsim仿真加速注意点

下面说一下我的使用方法(我一般是在linux下使用,考虑到大家大部分都使用windows,所以下面举的例子为windows下的使用方法):

1.建立modelsim子目录

2.第一次运行时,还是需要先到modelsim的gui一下执行vlib –work,以后就不需要了

3.在modelsim子目录建立 run.bat文件, 内容如下(大家更具自己的环境,要做适当修改) vlog -incr ../ modelsim/yourtest_tb.v -f test.cfg \ +incdir+../ modelsim /include vsim -c -do "log -ports -internal yourtestbench/*; log -r yourtestbench /u0/*; run -all "\ -l log/ yourtest _tb.log -wlf yourtest.wlf work.testbench vlog用于verilog 编译,如果用vhdl 则是用vcom -incr 用于为增量编译开关,可以大大加快编译速度 test.cfg 为仿真cfg文件,里面放的是要编译的文件名,及库的目录 -c 为命令行运行开关 -do "log -ports -internal yourtestbench/*; log -r yourtestbench /u0/*; run -all " 和-wlf yourtest.wlf work.testbench 用来dump 出要察看的所有信号波形文件(波形文件的格式为wlf ,类似于vcs的vpd和vcd文件),yourtestbenc 为仿真入口模块名,u0 为你要测试模块的顶层instance的名字,yourtestbenc和u0都需要根据自己的环境来更改。 使用该命令之后将大大方便大家观看波形,(可能大家在初学时(包括我刚使用modelsim时),都是要看某一个信号时,先从signals的窗口中拉出来,然后再重新运行一编,效率很低)而使用该方法之后,从signals的窗口中拉出来的信号,直接就可以看到波形了,不需要再次运行。 按照以上方法建立好之后,就可以运行run.bat了(直接双击),这样就会弹出一个dos的窗口,所有的运行都在此窗口之下,不再启动modelsim了。

①使用增量编译

vlog -incr

vcom -incr

②不启用GUI界面,记录下仿真波形(仿真完后再看波形),将观察的信号打印到文件,直接比对

vsim -c -do run_sim.do -l vsim.log -wlf vsim.wlf

③启用nodebug模式(默认是debug模式),速度会有所提高,但某些调试功能将被禁止,比如trace x功能就不能用了

vsim -nodebug

④如果调用了IPCORE,研究官方的UG,加速仿真速度(ex:SRIO加速开关)

⑤修改设计,在不影响仿真结果的情况下,修改设计文件,加速仿真速度(ex:将counter从1024改为128)

加快modelsim仿真速度的方法

仿真精度越高,仿真效率月底。

仿真时采用`timescale 1ns/1ns比采用1ns/100ps的仿真效率高

simulation was two billion ns.

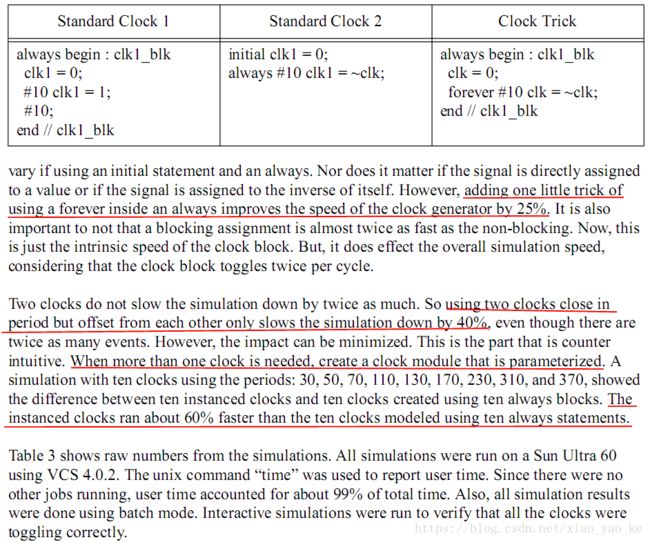

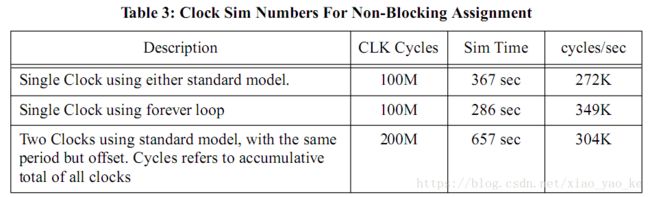

②clock generation coding tips

(from)

②减少层次结构

在设计中层次结构越少,仿真速度越快,这是因为参数在module中通过端口传递会消耗仿真器的时间

③进程越少,仿真效率越高

代码中出现的进程越少,仿真越快。因为仿真器在多个进程之间切换也需要时间。

④减少门级原语的使用,尽量采用行为描述

建模的抽象层次越高,仿真效率越高。描述同样的功能尽量采用行为描述,少使用门级原语

⑤尽量使用case语句,而不是if ...else语句

如果使用case语句和if..else语句能够实现相同的电路,则尽量使用case语句,以提高仿真效率。

⑥减少begin...end语句块的使用

在语义不发生歧义的情况下,尽量减少使用begin...end语句块,以提高仿真效率

⑦减少仿真器的输出显示

过多使用仿真器的输出显示任务,如$display,$fdisplay等,会降低仿真器执行的速度。

注意:以上几点只是用来提高仿真效率的建议,并不是说设计代码一定要这样做,而是建议在保证代码功能,可读性,可维护性和安全性的前提下,

尽量采用提高仿真效率的方法,节约仿真和调试的时间。毕竟代码功能,可读性,可维护性和安全性才是最重要的。

①使用增量编译,当整个仿真系统有大量文件组成时,每修改某个module中的部分信号后,想查看时序波形的时候,如果所有文件都编译一遍,会浪费大量时间。这时,增量编译可以有效的节约仿真时间

vlog -incr

vcom -incr

②不启用GUI界面,不启用modelsim的GUI界面一样可以完成仿真的所有工作,而且速度会比较快;记录下仿真波形(仿真完后再看波形:do wave.do;或将观察的信号打印到文件,直接比对)

vsim -c -do run_sim.do -l vsim.log -wlf vsim.wlf

xxx ③启用nodebug模式(默认是debug模式),速度会有所提高,但某些调试功能将被禁止,比如trace x功能就不能用了

vlog -nodebug

④避免显示不必要的信号

使用 log -r /* (记录所有的信号,运行这个命令后即使在仿真前没有把信号加入wave窗口,仿真完成后直接加入wave窗口就可以查看波形,比较方便,但是缺点是当工程较大和仿真时间很长时仿真速度较慢,占用内存也较大。)

好处是:可以记录所有信号的波形,方便后续查看到所有想查看的波形

缺点是:会降低仿真速度

⑤如果调用了IPCORE,研究官方的UG,加速仿真速度(ex:SRIO加速开关)

⑥修改设计,在不影响仿真结果的情况下,修改设计文件,加速仿真速度(ex:将counter从1024改为128)

⑧Use the vopt command to increase simulation speed.(modelsim.ini文件中:“VoptFlow = 1”默认打开优化)

vsim -vopt

-vopt Run vopt optimization before elaborating the simulator

-voptargs="

-novopt

(optional) Forces vlog to produce code if the VoptFlow variable is set to 1 (optimizations

turned on) in the modelsim.ini. (VoptFlow = 1 is the default behavior.) Use this argument

together with the vsim -novopt command to run the simulator without any optimizations.

For example, you may want to use this argument when you are coding an RTL block with a

small testcase.

-voptargs="+acc" :

The +acc switch is more

related to those, and is used to preserve visibility to certain categories of objects that might

otherwise be optimized away. Objects that get optimized away can make your debug and

analysis efforts more difficult

⑨为了提高仿真性能,应该使采样最小化。

减少仿真输出的总数,可以加快仿真仿真过程。使用计算机的输出设备会减慢程序的运行,因此,记录仿真输出的过程会使仿真变慢。

$monitor $write $display $strobe等系统函数的运用有助于debug,但会减慢仿真速度,根据实际做好平衡。

一个有效的减少数据采样的办法是:当进入testcase中感兴趣的地方时,令激励器打开采样过程。可以通过下面两个系统任务启动和关闭监控:

$monitoron(启动最近关闭的监控任务) ,$monitoroff(关闭激活的监控任务)

always begin:clk_50M_blk

clk_50M = 1'b0;

forever #(20/2) clk_50M = ~clk_50M; //50Mhz

end

always begin:clk_100M_blk

clk_100M = 1'b0;

forever #(10/2) clk_100M = ~clk_100M; //100Mhz

end

ddr仿真加速设置,

1、跳过校准

2、